一种超大摆幅5 Gb/s PAM4发射器设计

2019-03-08汪少波林福江

汪少波,林福江

(中国科学技术大学 信息科学技术学院,安徽 合肥 230026)

0 引言

当今社会,随着信息量的骤增,对数据传输速度的要求越来越高。而在高速传输系统中,高速信号的发送和接收电路起着至关重要的作用。而多种与频率相关的非理想特性,严重限制了系统频率[1]。由于四阶脉冲幅度调制(Four-level Pulse Amplitude Modulation,PAM4) 每一个码元可以携带2倍于不归零码调制(Non Return to Zero,NRZ)的信息量,因此PAM4调制方式越来越受到青睐。

目前,PAM4发射器的理论研究已经取得很多成果,高速与低功耗发射器均有优秀设计[2]。然而其在市场上仍然不能够完全替代NRZ调制器。主要原因在于以下两点:一是目前的设计输出摆幅较小,4个符号电平降低了符号电位差值,增加了判决难度。更大输出摆幅的PAM4发射器迫切地被需求,以此来获得更大的输出眼高,减小误码率。二是传统的开关逻辑存在交叉切换,导致输出存在暂态误码,进一步恶化输出眼图。本文针对这两大缺陷,设计了一款超大输出摆幅的PAM4发射器,并且将传统的两条支路抽取电流方案改为三支路抽取,从而改变了开关逻辑,消除了开关交叉切换带来的暂态误码。

1 设计方案

1.1 整体架构设计

本文所设计的超大输出摆幅5 Gb/s PAM4发射器整体架构如图1所示。其结构按照信号流向主要包括以下4个部分:译码器、单端转差分电路、缓冲器和驱动电路。两路数据信号D0、D1首先经译码器译码产生3路开关控制信号,再由单端转差分电路分别生成3组互补开关控制信号,再使用一个缓冲器增加3对控制信号的驱动能力,最终控制主驱动电路产生四阶脉冲幅度调制。

图1 总体结构框图

1.2 译码器

译码器输入为2 bit的并行信号,译码输出为3路开关信号。以2 bit信号的4种状态为输入,经译码控制3条电流支路的通断,控制输出的4个电平值。其逻辑结构由电路真值表决定,如表1所示。

表1 支路开关信号真值表

根据上述真值表,当D1和D0同时为低电平时,输出电压为最低值1 V,流过电光调制器的电流为最小值20 mA,此时3条支路电流全部为零,3组开关全部为低电平。每导通一条支路,输出电流增加30 mA,输出电压增加1.5 V。另外两种状态依次类推。根据上述真值表,得到译码电路可设计为:

S3=D1+D0

(1)

S2=D1

(2)

S1=D1D0

(3)

本设计工作频率为2.5 GHz,上述逻辑门电路采用静态CMOS门电路即可满足速度要求。

1.3 单端转差分电路

差分电路具有更好的抗干扰能力,并且差分开关能够避免电流源支路完全关断而导致的电流重新建立。所以驱动电路采用差分结构既能获得更高的精度,又能大幅度提升驱动电路切换速度。由译码器产生的3路开关信号需要转变成3组差分信号,所以电路设计中必须包含单端转差分电路。

然而,传统的单端转差分电路必须包含一个运算放大器,如图2所示。在本设计中,系统工作频率高达2.5 GHz,要求在这个频率下运放增益足够大,仍可被视为理想运放,则运放增益带宽积需大于100 GHz。设计该运放将消耗极大功率,并且设计难度也非常高。本文提出一种专用于互补开关信号产生电路,能够避免使用运算放大器。电路由非交叠时钟、锁存器和缓冲器组合而成,电路结构如图3所示。非交叠时钟可将单端输入信号变换输出为一对相位差接近180°、占空比接近相等的输出信号。由非交叠时钟输出的互补信号相位差偏离180°过多,并且3路开关信号存在链路延时差异,会加长输出状态切换时间,所以设计锁存电路对3对开关信号进行同步,并进一步减小非交叠时钟输出信号的相位差。

图2 传统单端转差分电路

图3 专用单端转差分电路

锁存电路在CLK为低电平时,处于保持状态,驱动电路的控制信号不会变化;在CLK为高电平时开关信号的变化才能经锁存器传递到驱动电路。所以可以通过CLK信号对3对开关信号进行同步。最后再利用缓冲器充放电回路不同,分别设计PMOS管和NMOS管尺寸,以此控制每一对开关信号交越电平,即可最大限度地减小开关切换时间,提升驱动电路速度。

1.4 驱动电路

驱动电路电路图如图4所示。在2.5 GHz的高频情况下,要求电路输出摆幅达到超高的4.5 V。大的输出电压摆幅要求大的调制电流,而大的调制电流需要尺寸很大的MOS管,但是大的MOS管尺寸会降低电路速度[3]。本设计中速度与超大摆幅之间的矛盾是设计过程中的重要难点。本文采用了以下三种方法提升系统速度[4]:

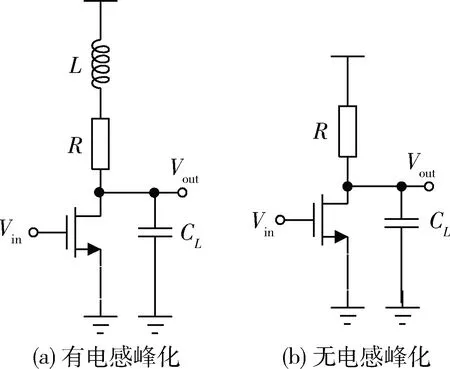

(1)增加并联电感以锐化方波边缘,提升状态转换速度。有无并联电感结构分别如图5(a)和图5(b)所示。

图4 驱动电路原理图

图5 有无并联电感电路原理图

如图5(b)所示,无电感峰化时传递函数为:

(4)

有电感峰化时的传递函数为:

(5)

令:

(6)

则可得到:

(7)

由式(7)可知,改变k值可以获得不同的带宽扩展。

(2)驱动电路采用低压共源共栅电流镜偏置,如图4所示。由于输出端最低电压仅为1 V,采用传统的层叠式共源共栅(cascode)电流镜会导致MOS管过驱动电压很低,需要很大尺寸才能产生所需调制电流。而过大的尺寸会增大输出端与电流源支路之间的耦合效应,使得MOS管栅极会抽取较大电流,加长暂态过程,降低状态切换速度。低压差结构可以有效地提高MOS管过驱动电压,从而减小管子尺寸,提高速度。另一方面,独立给予共栅管栅极偏置电压,可以避免栅极抽取偏置电流,防止暂态时间加长。

(3)本文创造性地提出采用3条电流支路代替传统的两条电流支路方案,能够有效地提高速度并改善眼图。传统两支路PAM4发射器开关信号真值表如表2所示。从表2中可见,两支路方案,开关状态会经历从(0,1)到(1,0)的转变,而在此转变中,必会经历(0,0)或(1,1)的暂态过程。但(0,0)或(1,1)均代表着另一种状态,尤其是(0,0)状态会导致电平朝相反的方向变化。这种现象会显著地加长电平切换时间。同样,从(1,0)到(0,1)的状态切换过程也存在着相同的问题[5]。本文采用3条电流支路来实现四电平调制,从表1可知,3路开关不存在交叉切换,杜绝了上述问题,提升了速度并改善了输出眼图。

表2 两支路方案开关信号真值表

图6 高精度基准电流源

1.5 高精度电流源

支路电流精度直接决定输出电压精度,也就影响着线性度和眼图。所以本文要求电流源精度很高。目前的高精度电流源普遍采用带隙基准电压经电压电流转换电路产生,电路原理如图6所示。

带隙基准电压经运算放大器隔离后加到电阻R上,以此产生基准电流源,其值为:

(8)

由于Vref是由带隙基准产生的,其基本上不受工艺、温度、电源电压的影响,因此由此得到的基准电流源精度很高。改变电阻R的值,就可以得到想要的基准电流值。下面介绍带隙基准电压源电路。

本文采用的带隙基准电压源电路如图7所示。

图7 带隙基准电压源电路

此电路结构没有使用运算放大器,所以没有运放带来的失调等非理想效应,并且大幅降低基准源电路所需功耗。PMOS管尺寸相同,所以3条支路电流相等,NMOS管尺寸也相等,所以Vx=Vy,那么由Q1和Q3的VBE差值即可在R1上产生电流I。此电流经PMOS电流镜复制到电阻R2上形成电压差,并与VBE2叠加得到所需的基准电压输出。其值推导过程如下:

IR1=VBE1-VBE3=VTln8

(9)

于是可以得到输出基准电压为:

(10)

其中,VBE2是负温度系数,VT是正温度系数,适当地选择R1和R2的值就可以获得零温度系数电压。

带隙基准电路存在着简并偏置点,所以需要启动电路使电路脱离此状态并进入正常工作状态。图7给出了一种启动电路。

2 仿真结果

本文设计了一种超大摆幅5 Gb/s PAM4发射器。发射器的供电电压为6.5 V,图8为发射器的输出电平波形图。其单端输出的最大电压摆幅为4.5 V,电压纹波小于50 mV时,可获得的稳定电平时间大于220 ps。电压过冲小于500 mV。图9为发射器输出眼图。眼图高度为1.445 V,眼图宽度为360 ps。本文所设计的PAM4发射器与近年来发表的文献设计参数对比如表3所示[6]。

图8发射器输出电平波形图

图9 发射器输出眼图

文献工艺/nm电源电压/V比特速率/(Gb/s)单端输出摆幅/mV功耗/mW文献[1]651.24045036文献[2]28145650120文献[5]90120-103文献[6]651.260250290本文1306.554 500845

3 结论

基于GlobalFoundries 130 nm SOI CMOS工艺,本文设计了一种超高电压摆幅的PAM4发射器。采用的3支路电流源方案能够避免开关信号交叉切换,从而使交叉切换带来的额外切换时间被移除,有效地提高发射器速度并改善眼图的眼宽。其4.5 V超高的单端输出摆幅能够极大地增大眼图的眼高,减小误码率。