基于V93000的现场可编程门阵列测试时间优化方法

2019-02-22肖艳梅解维坤

肖艳梅,陆 锋,解维坤

(1. 江南大学 物联网工程学院,江苏 无锡 214122;2. 中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 引 言

现场可编程门阵列(FPGA)已成为当前电子系统中广泛使用的数字芯片之一,其质量及可靠性要求越来越高,使得对FPGA的测试需求越来越大. 随着FPGA规模发展到千万门级甚至是亿万门级,配置向量越来越大,测试数据量将非常庞大,这不仅对测试仪的传输带宽、存储深度、频率提出了更高的要求,而且也大大增加了测试时间.

目前的研究大多从测试压缩的角度出发,通过减少测试数据量来减少测试时间,提高测试效率. 如文献[1]~[3]介绍了测试激励和测试响应压缩编码算法[1-3]等,这些测试压缩方法都需要在待测芯片内部增加解压缩电路; 文献[4]提出FPGA多帧写位流压缩方法,不需要在芯片内部增加解压缩电路[4],达到了很好的压缩效果,但是应用到更大规模的FPGA芯片测试中,测试时间仍旧是可观的.

本文从配置时间开销的角度出发,提出基于V93000 SoC测试系统的4X配置方式与FPGA多帧写位流压缩相结合的方法,对FPGA编程下载时间进行优化,提高在系统配置速度,从而降低测试成本.

1 FPGA配置模式及配置流程

1.1 FPGA配置模式选择

基于自动测试设备(Automatic test equipment,ATE)对FPGA进行测试时,加载测试配置时间往往是加测试向量时间的数百倍,因而对配置模式的选择尤其重要. 如表 1 所示:FPGA配置模式主要分为主串、从串、主并、从并模式和边界扫描模式. 本文选择从并配置模式进行FPGA配置,这是因为从模式的时钟CCLK可同时从外部提供,对下载时序的要求比主模式简单得多,而且并行模式可以使用D0~D31数据位并行下载,节省时间.

表 1 FPGA配置模式

1.2 FPGA配置流程

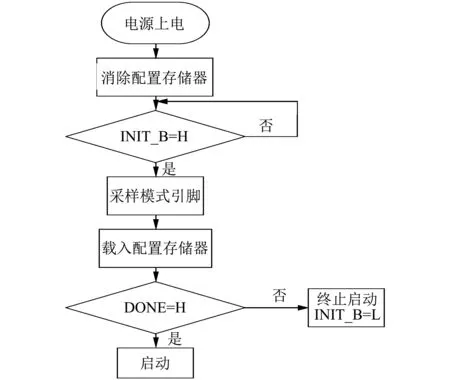

FPGA的配置是加载设计规定的编程数据到一个或多个器件的运行过程,以定义器件内部功能块与其互连的功能[5]. FPGA配置过程主要有4个步骤:清除配置存储器、初始化、配置及启动[6],配置流程如图 1 所示.

图 1 FPGA配置流程Fig.1 The configuration flow of FPGA

2 基于V93000的4X配置方式与测试实现

2.1 4X配置方式

V93000是定位于测试高速、高精度SoC芯片的测试平台,每根通道都有自己独立的向量存储、施加和测量单元[7]. V93000的测试信号是由测试时序和测试向量合成的[8],其中测试时序定义了被测器件(DUT)的信号周期和测试波形,以及每个测试波形相应定时沿(输入驱动沿d1,d2,d3,d4,输出比较沿r1,r2,r3,r4)的时间点[9]. 基于V93000的4X配置方式是:通过在一个周期内设置4个数据驱动沿完成4位向量的输入,4个输出比较沿完成各个输出信号的采样和比较. 4X配置方式的数据读取速度是一般配置方式下的4倍,测试配置的编程下载时间将大大减少,同时每个通道可容许的向量深度是现有向量深度的4倍.

图 2 为4X模式示意图,表示在T0~T1一个周期内,时钟引脚CCLK的逻辑值为“1111”(由于时钟是脉冲信号,每个脉冲时钟需要 2个时间驱动来完成,相应的在4X模式下时钟需要8个驱动沿[10]),数据输入脚的逻辑值为“0110”,4个输出比较沿对输出引脚进行采样. 图 3 为基于ATE的一般配置方式及4X配置方式得到的配置向量.

图 2 4X配置方式示意图Fig.2 Schematic diagram of 4X configuration mode

图 3 一般配置方式及4X配置方式下的配置向量Fig.3 Configuration vectors in general configuration and 4X configuration mode

2.2 测试实现

为了验证4X配置方式下的测试时间优化效果,本文选取Xilinx公司Virtex-7系列千万门级FPGA-XC7VX485T[11]电路的一段LVCMOS15电平模式配置向量进行测试. 该配置文件大小为410 M,如此大的数据量要求找到一种快速配置方式来满足向量深度以及测试时间的需求.

选择32 b从并配置模式,采用一般配置方式对FPGA进行在系统配置. 该电平模式下的单次配置时间为1.047 s,实验数据如图 4 所示.

图 4 一般配置方式测试结果Fig.4 Test results of general configuration mode

选择32 b从并配置模式,采用4X配置方式对FPGA进行在系统快速配置. 该电平模式下的单次配置时间为271.329 ms,实验数据如图 5 所示.

图 5 4X配置方式测试结果Fig.5 Test results of 4X configuration mode

实验数据表明:采用4X配置方式,FPGA的单次配置时间由1.047 s压缩到271.329 ms,测试时间是一般配置方式的25.9%,配置时间减少了74.1%,说明该方法是优化测试时间的有效方法. 但是FPGA单次测试时间依旧在几百毫秒量级,对于需要多次配置的FPGA来说,该方法不能满足量产测试对于测试时间的要求.

本文将V93000的4X配置方式与FPGA的多帧写位流压缩相结合,对配置向量进行压缩,降低对测试系统向量空间的需求,对单次配置时间进行进一步优化.

3 多帧写位流压缩与测试实现

3.1 FPGA多帧写位流压缩

多帧写位流压缩方式是对FPGA配置位流文件进行压缩. 该方法以行为单位,通过统计位流文件中配置数据相同的帧,并将这些相同的帧放在一起进行配置,先以普通模式配置第一帧,接着用压缩方式配置其余帧,而不是严格按照帧地址顺序进行配置,并且不需要在芯片内部构建解压缩电路. 位流压缩的原理如图 6 所示.

图 6 位流压缩原理Fig.6 The principle of bitstream compression

3.2 测试实现

同样以Xilinx公司Virtex-7系列千万门级FPGA-XC7VX485T电路的一段LVCMOS15电平模式下的配置向量为例,对4X配置方式与FPGA的多帧写位流压缩相结合的测试方法的测试时间优化效果进行验证.

图 7 多帧写位流压缩+4X配置方式测试结果Fig.7 Test results of combining multi frame write bitstream compression with 4X configuration mode

选择32 b从并配置模式, 4X配置方式下, 结合多帧写位流压缩方式, 对FPGA进行在系统快速配置. LVCMOS15电平模式的配置时间为47.834 ms, 实验数据如图 7 所示.

实验数据表明:在4X配置方式的基础上, 采用FPGA的位流压缩方法, 配置时间由271.329 ms 减少到47.834 ms, 成功地把单次配置时间控制在了100 ms以内, 测试时间压缩了82.4%. 即采用V93000的4X配置方式与FPGA的位流压缩相结合的方法, FPGA的单次配置时间由1.047 s减少到47.834 ms, 测试时间压缩了95.5%. 该方法大大减少了FPGA的在系统配置时间, 提高了测试效率, 节约成本, 满足了大容量FPGA测试对于测试时间的要求.

4 结束语

本文介绍了FPGA配置模式以及配置流程, 从配置时间开销的角度出发, 首先采用Advantest公司的V93000 SoC测试系统的4X配置方式对单次配置时间进行优化. 测试数据表明:配置时间减少了74.1%, 是优化测试时间的有效方法. 但是FPGA单次测试时间依旧保持在几百毫秒量级, 不能满足量产测试对于测试时间的要求. 进一步提出V93000的4X配置方式与FPGA的位流压缩相结合的方法, FPGA的单次配置时间由1.047 s减少到47.834 ms, 测试时间压缩了95.5%, 大大提高了FPGA在系统配置速度, 解决了FPGA测试数据配置与测试时间的矛盾. 研究结果可为高性能大容量FPGA测试时间提供一种新的优化方法.