基于UCC28070的六级交错Boost PFC设计

2019-02-21秦会斌

王 震,秦会斌,王 恒

(杭州电子科技大学 新型电子器件与应用研究所,浙江 杭州 310018)

0 引 言

随着电力电子装置的广泛运用,一些设备由于工作在非线性状态会产生大量的谐波,而这些谐波电流进入电力系统时会污染电网。为了满足国际电工委员会(IEC)IEC61000-4-2标准提出的谐波标准电流限制,在开关电源的应用中应尽量提高其功率因数,减少电网上的谐波污染[1]。

近年来,电动汽车和备用储能电池站不断发展,交流电源供电设备所需的功率也在不断提高,单级Boost PFC已经不能满足要求。本设计采用多级并联CCM模式的升压PFC转换器,具有以下特点:低输入电流纹波;高输入功率因数;有效减小EMI噪声。由于采用的是六级电路交错并联,在同等功率下相较单级Boost PFC,每路上承担的电流应力变小,减小了磁性元件的体积,增加了其系统的功率密度,极大地提高了设备功率[2]。

1 交错并联PFC工作原理

1.1 升压拓扑结构

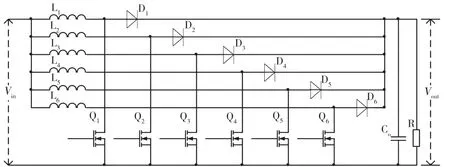

六级交错并联Boost PFC电路拓扑,如图1所示。

图1 六级交错并联Boost PFC电路拓扑

从图1可知,该电路由六级交错并联Boost PFC并联而成。一块UCC28070芯片集成了两级交错并联,通过轮流控制A、B、C三块UCC28070芯片,达到交替导通六级交错电路。这种方法将5 kW的功率输出相同等份地分摊在每一路,使得每路上的承受电流应力减小。在A芯片的导通周期内,它控制的两个并联升压PFC电路,控制Q1和Q2的MOS管驱动信号具有180°的相移,因此工作在交错状态[2-3]。

1.2 工作状态分析

六级交错并联升压PFC电路中,单路的工作原理与单级升压PFC电路区别不大,本质是将一个工作周期的工作量平分给六个电路[2-4]。为了便于分析理解,以下只分析前1/3周期内A芯片的工作状态,而B、C芯片工作原理与其等同,唯一区别是工作时间分别延迟1/3周期。同样地,假设所有的元件都是理想的。

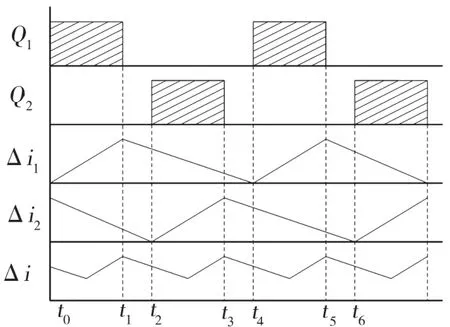

此设计中,两级交错并联型Boost PFC的工作占空比D<0.5,工作状态波形如图2所示。其中,Q1、Q2分别代表开关管Q1、Q2的驱动波形,Δi1、Δi2分别表示电感L1、L2的电流波形,Δi表示输入电流纹波。

图2 当D<0.5时,两级交错并联型Boost PFC的波形图

该电路有三个工作状态,如图3所示,分为四个阶段。

图3 两级交错并联Boost PFC工作状态图

阶段1(t0~t1):开关管Q1导通,Q2关断;二极管D1关断,D2导通;电感L1电流线性增加,能量储存在电感中,电感L2电流下降,进行放电。

阶段2(t1~t2):开关管Q1、Q2都关断;二极管D1、D2导通;电感L1、L2电感电流下降,进行放电。

阶段3(t2~t3):开关管Q1关断,Q2导通;二极管D1导通,D2关断;电感L1放电,电流下降,电感L2电流线性增加,能量储存在电感中。

阶段4(t3~t4):与阶段2相同。正常工作过程中,不断重复这四个阶段。

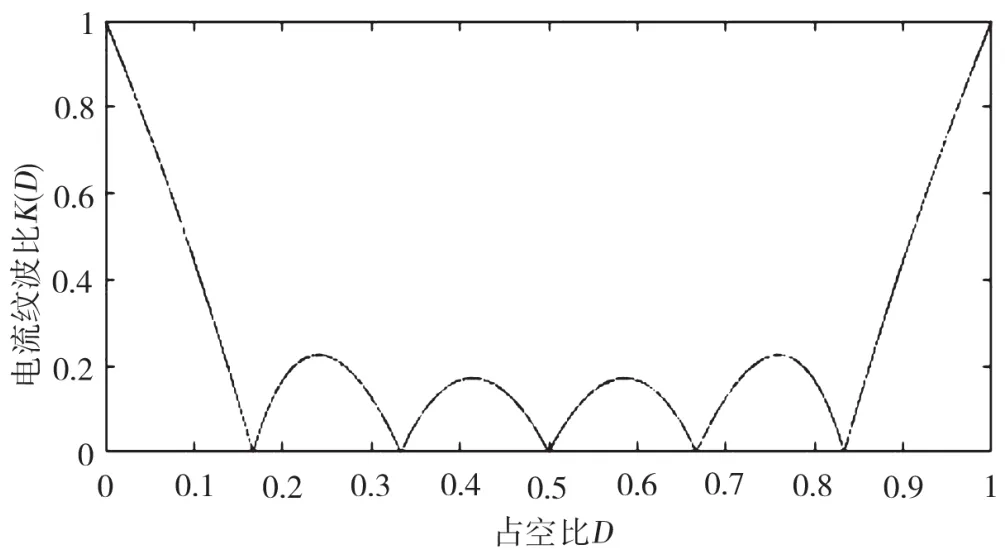

1.3 拓扑控制设计

本设计实现5 kW功率因数校正,采用恒定65 kHz开关频率,电路应用在180~265 V电压范围内,输出电压为400 V,采用DSP F28335芯片产生同步信号控制3块UCC28070芯片工作状态。

1.3.1 升压电感设计

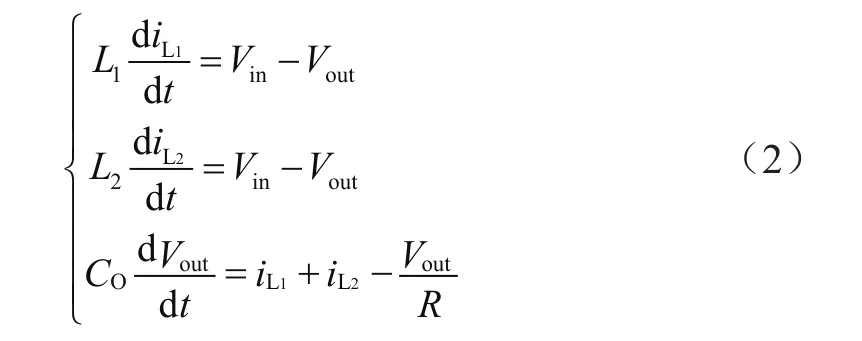

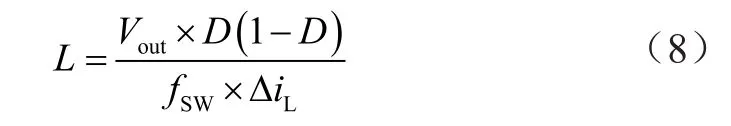

电感电流纹波比K(D)为:

其中Δi是总的输入电流纹波,ΔiL是每一级上的电感电流纹波。六级交错并联Boost拓扑电路纹波比值的一般函数表达式为:

由图4可知,在占空比0.3~0.5时,电流纹波比K(D)<0.2。虽然此电流纹波比小于单级Boost PFC,但是相较三级交错纹波电流比优势并不明显。

实际应用中,输入电压会在VINMIN到VINMAX之间变化。对于升压拓扑结构,输入电压最低点为“最恶劣”电压,即峰值电流达到最大值时的电压。根据式(6),可求最大占空比为:

图4 六级交错纹波电流比K(D)波形图

进而通过式(5)求出K(D)max,然后通过式(7)计算每一级电路的最大纹波电流:

其中Iin_pk为输入电流峰值。于是,每个电感的电感值为:

其中fsw是系统的开关频率,由此求得最“恶劣”情况下系统的电感值。

1.3.2 输出电容设计

输出电容的值必须足够大,以此提供所需的保持时间。UCC28070数据手册中[4]给出的输出电容经验算法为,每瓦输出功率约为0.6 μF。这表明在5 kW时,电容约为3 000 μF,而实际取值会相对取大一些。

1.3.3 同步信号处理

为了确保在GDA和GDB引脚输出精确的180°相移,RDM引脚上的脉冲频率fSYNC必须是fPWM的2倍。本设计中采用65 kHz的开关频率,则fSYNC应为130 kHz。

为了确保内部振荡器不会干扰SYNC功能,振荡器频率编程引脚的定时电阻RRT的取值设置,必须使内部振荡器频率至少低于fSYNC的10%,即:

当使用外部信号同步时,在UCC28070内部定时电路和SYNC信号的下降沿之间,存在50~100 ns的传播延迟,可能导致在最高开关频率下的关断时间减少。因此,最大PWM占空比编程引脚的最大占空比电阻RDMX应稍微向下调整,按照(tSYNC-0.1)/tSYNC进行补偿。

对于六级交错并联电路,每个控制器接收到相位相差120°的SYNC信号,以此获得最佳纹波消除。在多级交错系统中,每个电流回路独立且分别处理,只有一个公共电压回路。计算负载阻抗时必须调整为1/6,以保持与单个控制器相同的性能。

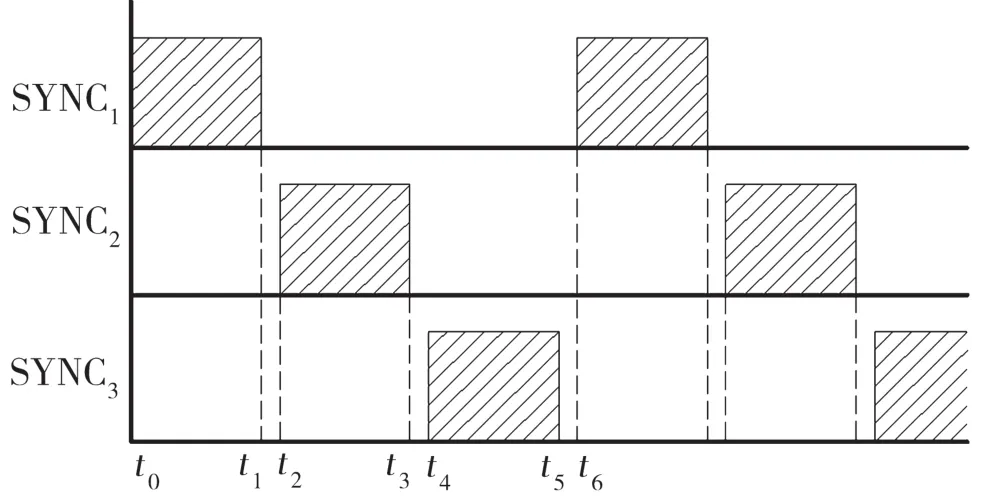

1.3.4 F28335产生同步信号

F28335具有增强型脉宽调制系统(ePWM),而每个ePWM模块都是一个独立的小模块。每一组ePWM模块包含7个模块:时基模块TB、计数比较模块CC、动作模块AQ、死区产生模块DB、PWM斩波模块PC、错误联防模块TZ和时间触发模块ET。利用F28335调制产生的同步信号波形,如图5所示。

图5 外部时钟同步信号波形图

其中,t0~t6为一个周期T,t1~t2、t3~t4和t5~t6为死区时间。SYNC1、SYNC2、SYNC3分别为A、B、C三块UC28070芯片提供外部时钟同步信号。

2 实 验

设计了一个5 kW的六级交错Boost PFC电路实验样机,目的在于观察六级交错电路的稳定性和测试相关性能。该实验中利用Chroma 66202型号的数字功率计进行测量。因为Chroma 66202设备的最大电流限制,所以测量时最大功率只加到了3 100 W左右,测得的实验结果如表1所示。

表1 Chroma A62003测得参数

随着功率的提升,功率因数的变化如图6所示。可知,该样机随着功率的提升,PF值不断增加,最终稳定在0.99以上。

图6 不同功率下的PF值的趋势图

图7 为3 800 W左右时的输入电流电压波形图,信号1是输入电压,信号2是输入电流。从图7可以看出,电流和电压之间的相位基本相等,达到了设计的要求。

3 结 论

设计的交错并联Boost PFC电路的电感电流的上升下降是六级交错的,由于输入电流的频率是每一级电路的6倍,有效减少了输入EMI滤波器的尺寸,提高了功率密度。在同等功率的情况下,多级交错对于开关管的应力要求更低,相较两级交错电路在5 kW功率下设计的磁性元件选型,优势明显。此设计过程中尚存在不足,样机中PCB的布局、热管理、EMI等方面仍可改进与提高。此外,该设计测试了提高电路级数的可行性,理论上还可以加大其使用功率。采用六级交错并联的方案,与三级交错电路相比,元器件的使用量增加了一倍,得到的电流纹波比K(D)值小于0.1,与三级交错电路相差不大。可见,本文通过多块芯片的组合提高交错并联级数,利用现有已成熟的技术,提高了应用功率。

图7 3 800 W左右时输入电流电压波形图