100GSR4并行光模块光电子集成封装的研究

2019-02-19杨松李佼洋蔡志岗

杨松 李佼洋 蔡志岗

关键词: 并行光模块; 光电子集成; COB封装; 芯片Bonding; 100G SR4; 有源耦合

中图分类号: TN15?34 文献标识码: A 文章编号: 1004?373X(2019)03?0152?05

Abstract: The wavelength of 100G SR4 parallel optical transceiver is 850 nm, and its single?channel transmission rate is 25 Gb/s. The 4?channel VCSEL emitting light is used in transmitting end, and the 4?channel PD receiving light is used in receiving end. An optoelectronic integrated packaging method used in 100G SR4 parallel optical transceiver is proposed, that is COB (chip on board) light bending active coupling packaging technique. The technology of COB light bending active coupling packaging is discussed emphatically, and the influence of the Bonding is analyzed. The100G SR4 parallel optical transceiver designed by this technique method has the advantages of high coupling efficiency, low cost and easy realization.

Keywords: parallel optical transceiver; optoelectronic integration; COB packaging; chip Bonding;100G SR4; active coupling

0 引 言

近年来,随着电子商务、高清传输、云计算和个人存储等业务的迅猛发展,对数据传输带宽的需求越来越高,光纤通信作为大批量数据传输的最佳选择,可通过提高传输速率和采用复用技术等各种方法提高传输带宽。早在2000年就已经推出了32×2.5 Gb/s DWDM(密集波分复用)系统,研制8×10 Gb/s DWDM系统及32×10 Gb/s DWDM系统[1]。现在,100 Gb/s传输速率的端口已经开始应用于数据交换设备中。各运营商、电子商务平台、互联网业务公司和大型企业等积极建设数据中心,实现数据业务的集中处理、分析和存储。数据中心内部和接入网下行端口对于短距离传输需求非常高,并行光收发模块作为高速、大容量光传输的技术方案之一,具有传输速率高、技术成熟和成本低等优势,广泛应用于数据中心和数据通信接入网,拥有巨大的市场前景。

传统的单路10 Gb/s或25 Gb/s速率的光模块采用SFP(Small Form?factor Pluggable,小型可插拔)封装外壳,尺寸[2]为56.5 mm×13.4 mm×8.5 mm,将电子芯片和TO(Through?hole)封装的光发射、接收组件焊接到PCB板上组成具有收发功能的光电转换模块。100 Gb/s的光模块主要采用QSFP(Quad Small Form?factor Pluggable)封装外壳,尺寸为76.4 mm×18.35 mm×8.5 mm, 具有4路25 Gb/s的信号传输通道[3]。如果采用传统设计SFP的方法将电子芯片和分立的光组件焊接到PCB板上设计100G SR4,将4组电子芯片和光组件一起焊接到PCB板上,不考虑单路速率的增加带来空间增加的影响,就需要4倍左右SFP大小的空间。但是QSFP只是稍微比SFP的尺寸大,因而,100 Gb/s的光模块采用传统的设计方案不能做到QSFP小型化外壳封装。

要解决并行光模块的设计,需考虑光电子集成封装的方法。光电子集成封装是将光器件和电子裸芯片一起集成在一个小空间内,要实现集成封装,需要考虑封装的可实现性,以找到一种适合光电混合封装的方法。

对于并行光模块集成封装,一些厂家采用将光电集成器件置于软板上面,通过软板与PCB连接的电折弯方法,这种技术借鉴了倒装工艺芯片(Flip Chip)封装技术。Flip Chip封装技术以各种焊料的裸芯片面朝下放置在相应的PCB焊盘上,通常使用特殊设备从晶圆片中取出芯片,将其倒转并放置在小Waffle Pack中[4]。Flip Chip封装技术更加提高了引脚封装密度,使引脚与焊盘之间的连接更加短,有利于减少高速信号连接产生的寄生参数等信号完整性问题的影响。但是可靠性检查比较复杂,只能借助X光或超声原理进行检查,工艺操作复杂度、难度和精度都要求很高,需要较高的工艺技术积累。而且Flip Chip封装夹具的制作精度要求比较高,要实现并行光模块光电子集成封装问题还得解决高精度夹具和工艺设备的问题,同时对自动控制和图像识别技术的依赖也较高。

并行多通道光器件和电芯片的集成封装决定了100G SR4并行光收发模块研发的成败。在本文设计方案中,采用COB(Chip On Board)封装技术,通过粘胶剂或焊料将晶片直接粘贴到PCB板上,与引线键合实现晶片与PCB板间互连互通实现器件封装。COB封装可以较大地提高封装引脚密度。同时,基于COB封装技术,为了提高耦合效率,采用光折弯技术,实现光纤耦合;在具体的耦合过程中采用有源耦合的方法降低成本,提高耦合准确度;整个封装技术的工艺操作简单,不需要投入其他高精度封装的夹具和工艺设备。将这种基于并行光模块的封装技术称为COB光折弯有源耦合封装技术。

1 100G SR4并行光模块

SR4并行光模块主要应用于数据中心內部交换机与交换机之间、交换机与存储器之间短距离的互连。光互连论坛(Optical Internetworking Forum,OIF)VSR?5[5?6]主要针对 SR4光互连制定了接口标准。IEEE Std 802.3bmTM [7]定义了以太网100G Base?SR4传输的指标要求。

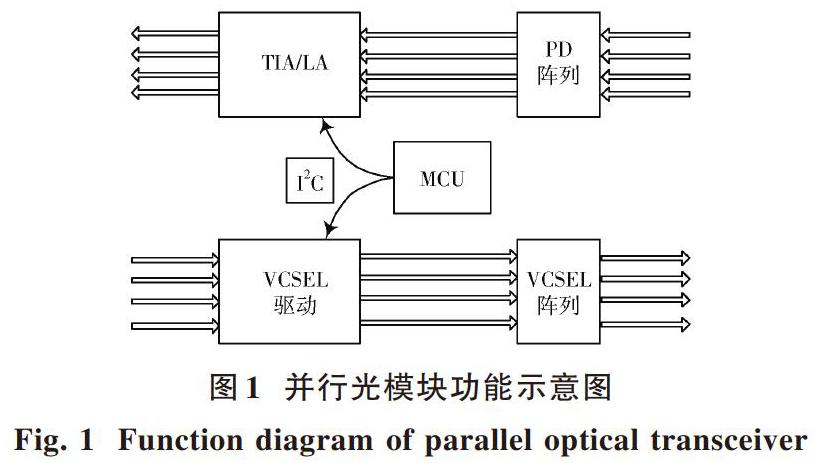

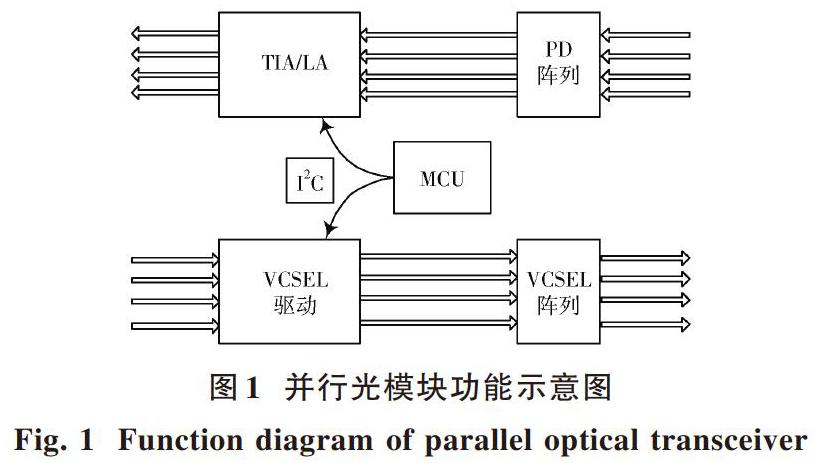

100G SR4并行光模块采用850 nm波长,单路25 Gb/s的传输速率,发射端使用4路VCSEL(Vertical Cavity Surface Emitting Laser,垂直腔面发射激光器)发射光,接收端使用4路PD(Photo?Diode,光电二极管)接收光。

根据SR4并行光传输要求,在QSFP等光模块封装中实现4路25 Gb/s信号的光电转换,进而实现4路光信号的并行传输。并行光模块包含的光电器件有4路VCSEL阵列、4路PD阵列、发射VCSEL驱动芯片、接收TIA/LA(Trans?Impedance Limiting Amplifier)芯片。对于单路25 Gb/s的高速传输,为提高信号质量,VCSEL驱动和TIA/LA芯片都需要集成CDR(Clock Data Recovery)功能。

典型的并行光模块组成示意图如图1所示,在发射端,发射驱动芯片驱动VCSEL阵列,将电信号调制到光信号中并耦合进光纤传输,实现电?光转换。在接收端,将光纤传输的光耦合到PD阵列转换成电流信号,电流信号经TIA/LA放大处理,解调出携带信息的差分电信号,实现光?电转换。MCU实现控制、数据存储、协议功能和信号监控等功能;同时,MCU也与耦合控制机台组成闭环的有源耦合控制回路,为COB封装提供有源耦合的软硬件技术支持。MCU与TIA/LA和VCSEL驱动芯片之前通过I2C通信,TIA/LA和VCSEL驱动芯片作为从机;MCU作为I2C主机,通过MCU的GPIO端口模拟I2C实现[8]。

要实现100G SR4光模块的光电子集成封装,需要将图1所示TIA/LA芯片、VCSEL驱动芯片、VCSEL阵列和PD阵列集成封装在一个小空间内并建立其电气连接,通过预留接口与MCU和PCB板建立物理连接。

本文100G SR4光模块的设计方案将此小空间直接置于PCB板上,即直接将TIA/LA芯片、VCSEL驱动芯片、VCSEL阵列和PD阵列一起通过焊料直接粘贴到光模块的PCB上,顾名思义Chip on Board(板载芯片或板上芯片封装)。VCSEL阵列与光纤、PD阵列与光纤采用透镜实现光折弯的方法,将VCSEL阵列的光耦合进光纤,将光纤传输的光耦合到PD阵列上;耦合工艺技术采用有源耦合的方式。这种工艺技术和封装方法形成了一套完整的光电子集成封装技术,将这种专用于并行光模块的封装技术称为COB光折弯有源耦合封装技术。

2 并行光模块光电子集成封装技术——COB光折弯有源耦合封装技术

2.1 封装技术方案

根据对100G SR4并行光模块的介绍,COB光折弯有源耦合封装技术就是将图1所示的功能芯片集成在QSFP等小封装空间里面。基于QSFP等封装的小尺寸、空间有限、技术要求和成本的控制,传统的光器件封装模式不能匹配并行光模块的设计。本文提出的COB光折弯有源耦合封装技术可解决并行光模块光电子集成封装的设计和制造问题。

100G SR4并行光模块的COB光折弯有源耦合封装技术是将光芯片、电子芯片和光波导LENS组成一个整体,一起集成在一块PCB板上,并通过PCB板上的MCU控制,实现并行光模块的光电转换和光传输功能。基于VCSEL驱动芯片、TIA/LA放大芯片和MCU设计的电路作用于光器件实现光电转换功能,光波导LENS器件将VCSEL发射的光耦合进光纤和将光纤传输的光耦合到PD上。

为降低光纤耦合的精度,VCSEL和PD拟采用阵列的形式,如果是单个VCSEL和PD,需要逐个对器件进行定位,增加4倍的定位和耦合精度要求。VCSEL驱动和TIA/LA芯片也需要采用阵列芯片,并且需要未封装的裸芯片,因为4路分立的电芯片集中放置在QSFP封装的PCB上,空间有限,如果将阵列芯片做成表贴的QFN(Quad Flat No?leadPackage,方形扁平无引脚封装)等芯片小封装形式,也已经超出了PCB尺寸范围,因而需要通过Die Bond和Wire Bond操作将裸芯片Die与PCB电路、光芯片通过金丝建立起电气连接。

由于VCSEL是垂直发光,发光方向与光纤垂直,将光耦合进光纤的光波导的实现方法有多种,本文采用LENS阵列实现光折弯的光纤耦合。LENS阵列的设计考虑匹配标准的MPO/MTP阵列光纤,将LENS的光接口设计成能与MT插芯直接连接的接口,基于全反射原理,根据光芯片光发射角和光敏面等参数设计符合要求的LENS阵列。LENS阵列中LENS之间的间距参考标准MT插芯中光纤的间距,设计为250 μm,有利于与MT插芯或者MPO接口的光纤连接,不需要再做接口转换。相应地,光芯片也采用间距为250 μm的VCSEL和PD芯片阵列,刚好和LENS的间距匹配,这样可进一步降低耦合精度要求,通过LENS的聚焦实现光折弯,提高光的耦合效率。

2.2 封装工艺流程

确定了技术方案和关键参数,接下来将介绍如何实现COB光折弯有源耦合封装。

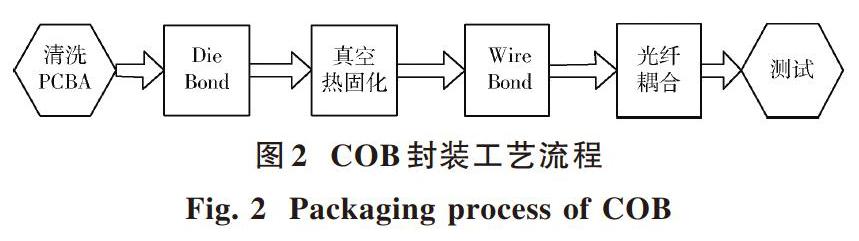

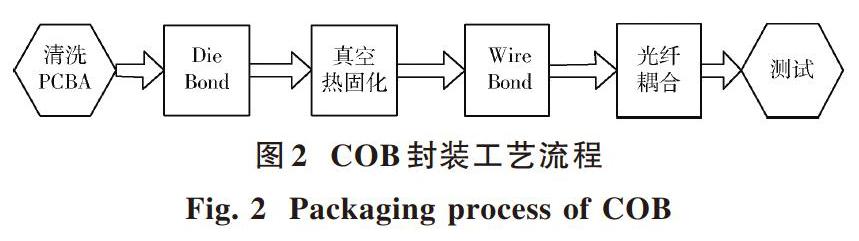

并行光模块COB光折弯有源耦合封装技术工艺流程如图2所示。在进行COB封装前,需要清洗已贴好电子元器件的PCBA(PCBA为已贴好电阻和电容等电子元器件的PCB),以避免PCB上的绿油和灰尘等附着物对Bonding的影响,进而影响合格率和产品性能,为了不损坏PCBA,最好使用等离子清洗机清洗。

清洗好PCBA后,接下來将进行Bonding的操作,借助Bonding设备将光电子芯片与PCB上的焊盘连接起来,形成一个具有完整电气性能的系统。Bonding的工艺操作主要是定位贴片和打线。首先需要进行定位的贴片操作为Die Bond,先在PCB需要贴片的位置上敷好银浆,然后将芯片定位在需要贴片的位置,光芯片定位的好坏会直接影响光耦合效果。根据实验和分析,一般精度要求是3~5 μm。贴好片后需要热固化处理来固定芯片,为防止在高温下氧化反应影响芯片功能,一般采用真空充氮气热固化的方法。根据银浆热固化的时间要求决定烘烤时间,烘烤后取出PCBA进行Wire Bond操作,将光电芯片焊盘与PCB焊盘用金丝连接起来。打线的好坏会影响产品的高速信号传输性能,进而导致产品的误码率提高或者发射传输信号质量问题。因为Bonding操作是整个封装技术的基础,下一节将会重点讨论。

接下来将对已经打好金线的PCBA进行光纤耦合。如前所述,在发射端,VCSEL激光器发射出来的光耦合到光纤中;在接收端,经光纤传输的光耦合到PD器件的光敏面上。

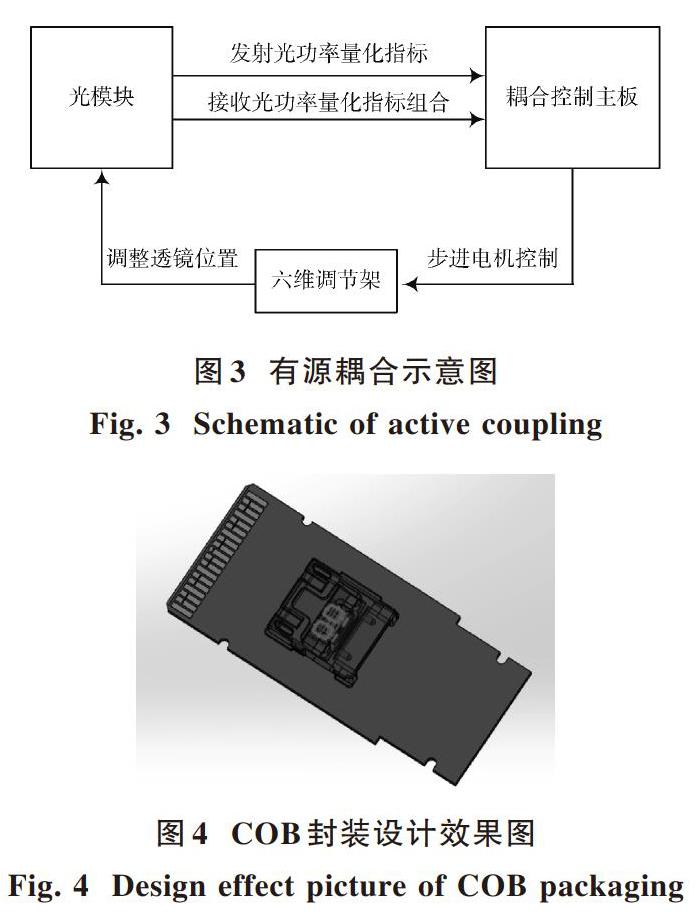

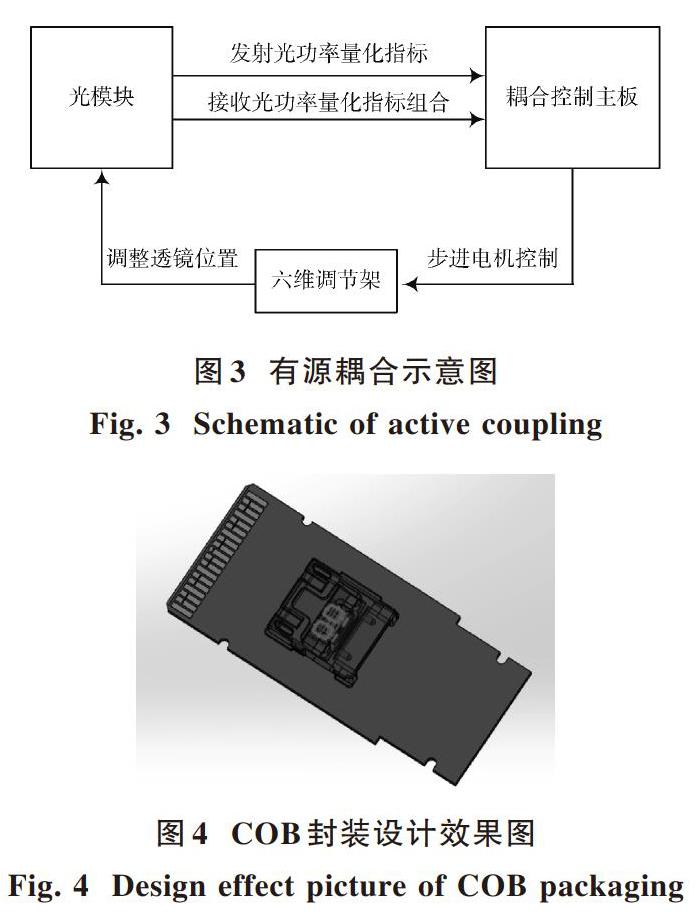

本文采用有源耦合的方式实现光纤耦合,有源耦合示意图如图3所示。由于利用LENS实现光折弯,光纤与LENS采用标准MT接口,可直接连接,因而光纤耦合转变成VCSEL和PD阵列与LENS之间的耦合。有源耦合的机理是利用光模块MCU与耦合控制主板的通信形成闭环控制,耦合主板从光模块获取发射光功率和接收光功率的量化指标,根据量化指标通过步进电机控制六维调节架调节LENS的位置,进而实现LENS与VCSEL和PD阵列的对中耦合。相比较需要借助图像识别技术的无源耦合方法,本文有源耦合方法工艺操作简单,而且耦合控制主板也是基于MCU控制,容易开发,无需投入精密控制的设备,具有制造成本低的优势。

LENS的位置确定后,通过紫外胶将LENS固定好,然后对耦合好的光电器件做密封处理。

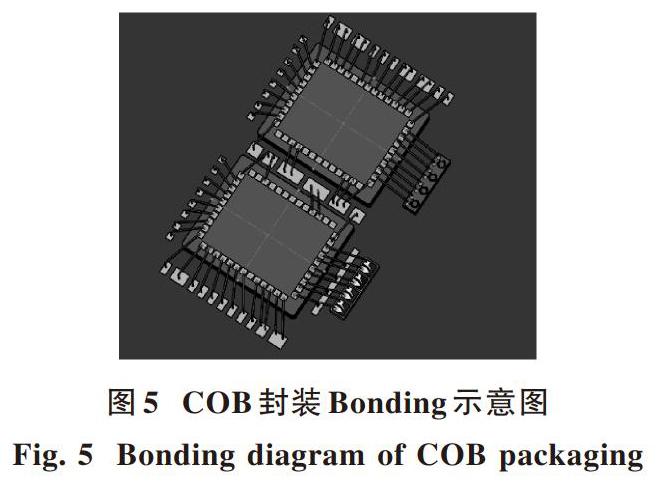

采用COB光折弯有源耦合封装技术设计的100G SR4并行光模块设计效果图如图4所示。

2.3 性能指标测试

最后对封装好的光模块性能指标进行测试,以判断是否符合要求。衡量光传输系统性能是否达标和优劣,需要对发送机和接收机分别进行测量,发送机主要测量平均光功率和消光比组成的眼图指标,接收机主要测量接收机的灵敏度[9]。根据实验测试,采用上述提出的COB光折弯有源耦合封装技术生产制造的100G SR4光模块眼图Margin达到30%左右,光纤耦合效率可达60%以上,发射光功率可达800 μW以上。接收端灵敏度为[-12] dBm左右,满足100G SR4光模块的传输指标要求。

3 COB光折弯有源耦合封装芯片Bonding工艺分析

在COB光折弯有源耦合封装技术的工艺流程中,Bonding是极其重要的环节,分为Die Bond和Wire Bond。前面提到,芯片定位和打线很重要,结果将直接影响产品性能。图5所示是本文设计的金线Bonding示意图。

在Die Bond的操作中,需要匹配LENS的8个(发射4个,接收4个)传输通道,所以VCSEL和PD阵列的定位很重要。如果定位不好,就会出现耦合效率不高或者个别通道耦合效率不高的问题。为做好Die Bond中芯片定位的操作,需要在设计中综合考虑。首先,采用VCSEL和PD阵列芯片,以降低调节精度要求;其次,为提高定位速度,在PCB设计时通过预留参考点的方法协助芯片定位,如预留PCB光绘点作为定位参考,方便人工或机器识别大致位置;再借助Die Bond设备做精准定位。

Wire Bond操作中,打线的质量直接影响产品的高速传输性能。对于非高速连接线,满足一般的电气连接可靠性就足够了,但是对于高速传输的信号线,打线的好坏对产品性能的影响非常大,不能仅仅满足连通的要求,还需要考虑不等长、非等距和焊盘不均匀带来的寄生参数的影响[10]。

Wire Bond有球焊和压焊两种工艺。球焊操作相对容易,对PCB焊盘的连接要求也低,金线弧度较好控制,但是焊点较大,容易带来寄生参数影响。压焊的焊点相对小,但是操作难度高,对焊盘的要求也相对高,如果焊盘粗糙程度不够会经常导致脱焊的情况。综合PCB制作工艺,PCB焊盘制作建议采用镍钯金的沉金工艺。

理想情况下,同一对差分线的两条线在适当的弧度下平行等长,但为了降低通道串扰的影响,每一对差分线之间的金线尽可能不平行走线;焊点尽可能小,避免寄生参数和反射的影响。实际操作中可调整Bonding设备的超声功率、线尾巴长度和压力大小等参数,确保焊点小而牢固。综合考虑,对于传输高速信号的金线建议采用压焊的技术,尤其对于单路25 Gb/s的速率,球焊比压焊带来的寄生参数影响要大得多。

经过试验,采用阵列芯片和PCB参考点设计可降低Die Bond精度控制和定位的难度;Wire Bond操作尽量降低金线的长度,保证差分线等长,对于25 Gb/s的速率,使用压焊可降低信号线的寄生参数影响,确保高速传输的信号质量。

4 结 语

本文提出采用COB光折弯有源耦合封装技术的100G SR4并行光模块的设计方案;介绍了光电子集成封装技术的工艺流程和关键实施方案,Chip On Board利用光折弯实现光耦合到光纤和采用有源耦合的技术方法;讨论了在工艺流程实施中Bonding的影响,并提出Die Bond和Wire Bond的建议。根据实验结果,COB光折弯有源耦合封装技术是一种非常适合并行光模块的集成封装方法,具有耦合效率高、成本低和易实现的优点。

随着数据中心光互连产品需求的逐渐增多,这种性价比较高的光电子集成封装方法将广泛应用到并行光模块产品的批量制造以及其他系列的光互连产品中。相信经过不断的工艺改进和研究,并行光模块的光电子集成封装工艺技术将越来越成熟。

参考文献

[1] 王海潼,孟杰.对光纤通信现状与未来的思考[J].现代电子技术,2003,26(16):5?7.

WANG Haitong, MENG Jie. Thinking of present and future of optical fiber communication [J]. Modern electronics technique, 2003, 26(16): 5?7.

[2] Agilent Technologies, Blaze Network Products, E2O Communications, Inc., et al. Small form?factor pluggable (SFP) transceiver multisource agreement (MSA) [EB/OL]. [2000?09?14]. https://www.baidu.com/link?url=vSNWdXdnkA8LXoS?dzsVOi

[Jaqsh4alcCAGj9NnZSHM9pfI_p7uTJTGbsIPmTxK93Z_ET1iDeM?][l_n7 YoZbLt 4fNpcUQ05 AgekDKzClhiN7 u&wd = &eqid = 8a?]

7076730000e65a000000035c04e286.

[3] SFF Committee. SFF?8665 QSFP+ 28 Gb/s 4X pluggable transceiver solution (QSFP28) [S]. US: SFF Committee, 2013.

[4] 鲜飞.先进芯片封装技术[R].武汉:烽火通信科技股份有限公司,2013.

XIAN Fei. Advanced chip packaging technology [R]. Wuhan: FiberHome, 2013.

[5] Optical Internetworking Committee. OIF?VSR5?01.0 very short reach interface level 5 (VSR?5): SONET/SDH OC?768 interface for very short reach (VSR) applications [S]. US: Optical Internetworking Forum, 2002.

[6] Optical Internetworking Committee. OIF?SFI5?02.0 serdes fra?mer interface level 5 phase 2 (SFI?5.2): implementation agreement for 40 Gb/s interface for physical layer devices [S]. US: Optical Internetworking Forum, 2006.

[7] IEEE Committee. Part3: carrier sense multiple access with collision detection (CSMA/CD) access method and physical layer specifications; amendment 3: physical layer specifications and management parameters for 40 Gb/s and 100 Gb/s operation over fiber optic cables [S]. US: IEEE Committee, 2015.

[8] 吴玮,胡必春,张敏明.I2C总线驱动在嵌入式系统中的两种实现[J].现代电子技术,2007,30(8):56?58.

WU Wei, HU Bichun, ZHANG Minming. Two implementations of I2C bus driving in embedded systems [J]. Modern electronics technique, 2007, 30(8): 56?58.

[9] 丁喆,刘增基.光纤通信的测量技术[J].现代电子技术,2004,27(6):79?80.

DING Zhe, LIU Zengji. Measurement technology of optical fiber communication [J]. Modern electronics technique, 2004, 27(6): 79?80.

[10] BOGATIN E.信号完整性分析[M].北京:电子工业出版社,2011.

BOGATIN E. Signal integrity: simplified [M]. Beijing: Publishing House of Electronics Industry, 2011.