基于FPGA和单片机的高精度数字频率计的设计与实现

2019-02-02崔凯杨天虹席贯周嘉维

崔凯 杨天虹 席贯 周嘉维

摘要:本文主要介绍了一种基于FPGA和单片机的高精度数字频率计的设计与实现。51单片机实现计算功能,液晶屏完成数据显示,FPGA对被测信号计数并将测量结果发送给单片机。实现了频率范围为1Hz~10MHz、有效电压范围为50mV~1V 的正弦波信号频率和周期的测量;以及频率范围在100Hz~1MHz、峰峰值电压范围50mV~1V 的两路同频周期方波信号的时间间隔测量,时间间隔测量范围为0.1μs~10ms。

关键词:FPGA;51单片机;频率测量;时间间隔测量

中图分类号:TN828.6 文献标识码:A 文章编号:1007-9416(2019)11-0162-02

0 引言

随着电子技术的发展,快速准确地获得各种电子信号的频率显得尤为重要。传统以单片机为核心的数字频率计,在测量精度、测量范围、功能以及操作上均有较大改善空间。基于FPGA的数字频率计很大程度上解决了测量范围、稳定度与精度的问题。目前数字频率计的设计可以直接面向用户需求进行设计,设计过程除了系统行为和功能描述以外,其余所有的设计过程几乎都可以用计算机来自动完成,也就是说做到电子设计自动化。

1 高精度数字频率计的基本工作原理

数字频率计的主要功能是测量周期信号的频率,频率为在每个单位时间内信号周期变化的次数。在选定的时间内对信号的波形进行计数,便能得到该被测信号的频率。为确保设计的精度与准确性,首要的就是获取准确的计数时间,在此基础上将被测信号转换成波形与幅度都能被电路识别的脉冲信号,然后通过计数器获得单位时间内的脉冲个数,将其结果通过换算显示出来。

2 高精度数字频率计的硬件设计

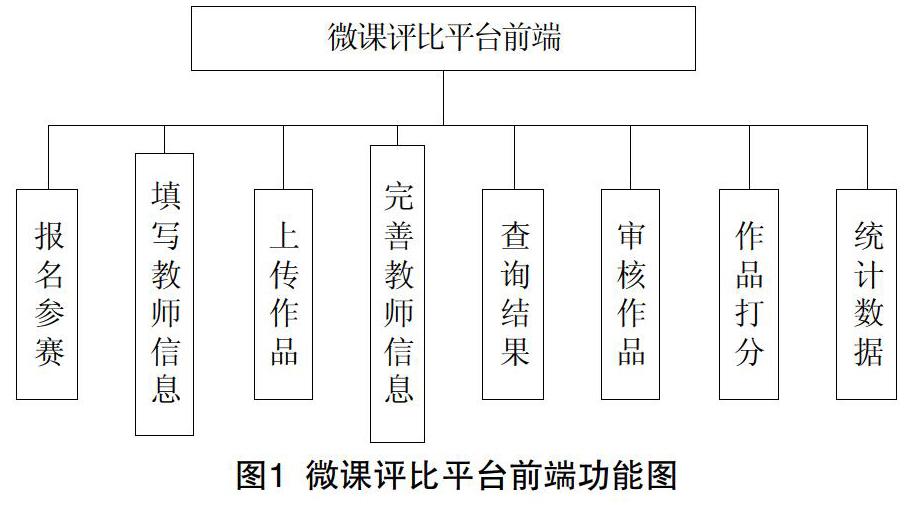

系统主要由放大整形电路、FPGA和C8051F020单片机组成。其中,波形放大整形电路的功能是将输入信号变换成标准矩形波信号,达到FPGA可测量的目的;FPGA主要完成频率和脉宽的测量,既能对输入信号以及标准信号的数目进行计数,又对输入信号的高电平时间进行计数完成脉宽测量。当单片机的读取信号到来时,FPGA将测量值通过SPI串口传输给单片机;C8051F020单片机主要完成数据处理,将FPGA测量的数据读回并进行相应的计算,最终将测量结果显示在TFT液晶屏上,系统整体框图如图1所示。

3 高精度数字频率计的软件设计

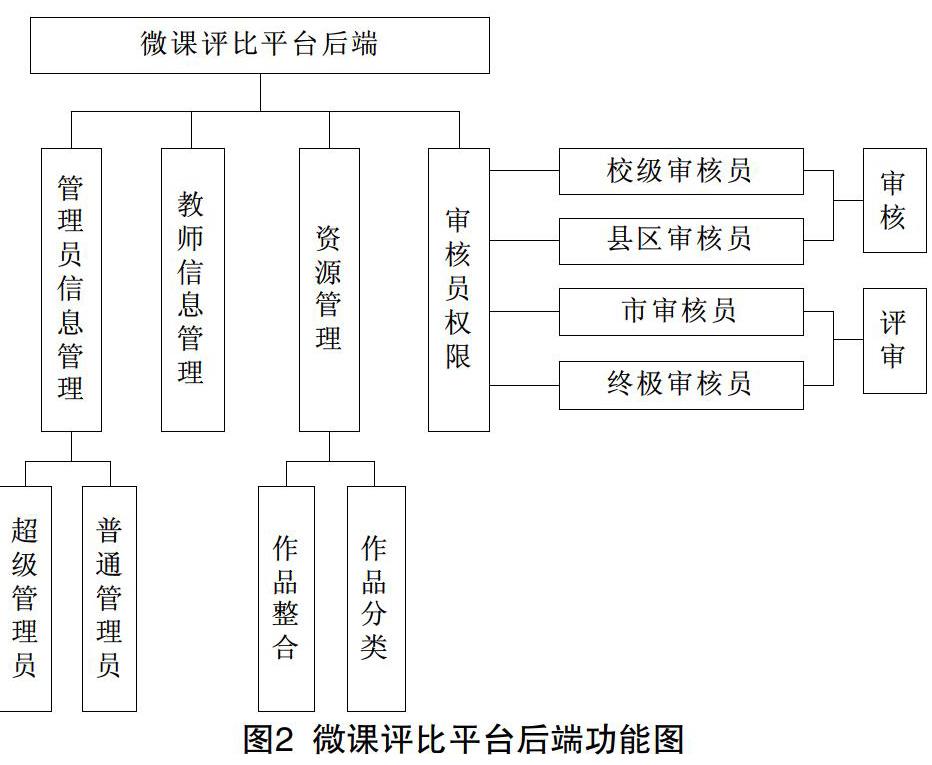

FPGA主要完成的工作是:采用直接测周法和等精度测频法结合测量信号频率,对输入信号个数和标准信号个数进行计数;采用游标法对输入的两路同频周期信号进行测量,并将测量得到的数据通过SPI通信发送给C8051F020单片机进行处理。系统整体结构框图如图2所示。

4 测试结果

4.1 频率和周期测试结果

电压50mV~1V范围内依次测量频率在1Hz~10MHz的正弦信号,测量结果如表1所示。

4.2 时间间隔测试结果

电压50mV~1V范圍内以0°~360°的相位差依次测量频率在100Hz到1MHz的方波信号,测量结果如表2所示。

5 结语

本系统测量有效值电压为50mV~1V、频率为1Hz~10MHz 的正弦波信号的频率和周期;测量峰峰值电压为50mV~1V、频率为100Hz~1MHz的两路同频周期方波的时间间隔,被测时间间隔为0.1μs~10ms;测量数据刷新时间不大于2s,测量结果稳定,准确度高,并能自动显示单位。

参考文献

[1] 王鹏,连帅彬,孙秋菊,等.低复杂度多功能自适应数字频率计设计[J].信阳师范学院学报:自然科学版,2016,29(4):599-603.

[2] 姜志健,庄建军,陈旭东,等.基于FPGA的高精度频率计的设计与实现[J].电子测量技术,2017,40(5):41-46.

[3] 余果,郭心伟,刘小浩,等.基于FPGA的数字频率计设计[J].电子设计工程,2016,24(18):57-59.

[4] 齐宣,李一民,邵玉斌,等.基于STC51单片机的高精度频率计设计[J].软件,2017,38(12):220-222.

[5] 陈靖,徐清.基于可编程逻辑阵列的高精度频率计设计[J].技术研究,2016,9(11):30-33.