电磁超声脉冲激励系统设计

2019-01-30于腾飞任尚坤

于腾飞,任尚坤,张 丹

(南昌航空大学无损检测技术教育部重点实验室,江西 南昌 330063)

0 引言

与传统的压电超声检测技术相比,电磁超声检测技术具有结构简单、易于使用、非直接接触、环境适应性强的特点[1-3]。但是由于其能量转换效率较低,低电压下很难由脉冲激励产生超声波,需要高压、高频的激励脉冲才能得到用于检测的超声波[4-5]。由于被检测材料的特性不同,激励系统的输入参数不尽相同。因此,需要开发一种能够应用在多数材料检测中的激励系统。

目前,国内外已有研制成功的电磁超声脉冲激励系统,如Innerspec科技生产的高频脉冲发生器,在100 kHz~6 MHz频率范围内对50 Ω的负载有8 kW的功率输出,在25 A电流峰值下有着最大1 200 V的电压峰峰值。北京化工大学的李爽等采用了复杂可编程逻辑器件 (complex programmable logic device,CPLD)和EPM1270芯片,设计了一种激励频率为500 kHz、可输出电流峰值约为3 A的激励系统[6]。辽宁科技大学的姜海君等设计了一种采用函数发生器驱动三极管和金属氧化物半导体(metal oxide semiconductor,MOS)管的激励系统[7]。但该系统结构较为复杂,实用性不高。

为使电磁超声技术达到更好的检测效果,本文选用MOS管组成全桥电路,通过在现场可编程门阵列(field programmable gate array,FPGA)芯片中产生若干个脉冲激励信号,完成直流到交流的变换以及功率的放大,实现换能线圈中能量转换产生超声波。输出脉冲的频率范围是300 kHz~5 MHz。

1 激励系统的总体结构

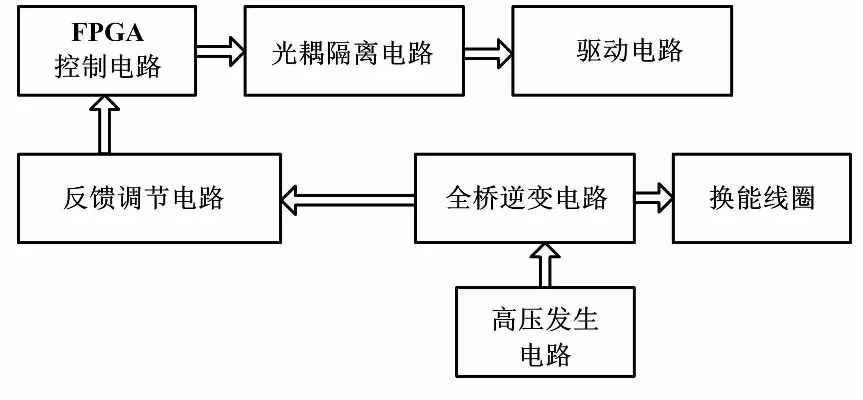

激励系统总体结构如图1所示。被检材料的特性决定了激励脉冲的频率以及脉冲个数,这可以通过预先设定FPGA控制电路的参数来实现。控制电路根据设定的参数产生一定个数的脉冲信号,在光耦隔离后,经驱动电路提高驱动能力控制全桥逆变电路中相应开关管的开启与关断,将直流高压发生电路产生的高压转换成可以驱动换能线圈的高频脉冲。全桥逆变电路输出的激励脉冲信号会在反馈调节电路的监控下实时反馈,并使整个系统得到控制调节。

图1 激励系统总体结构图

2 硬件电路设计

2.1 直流高压发生电路

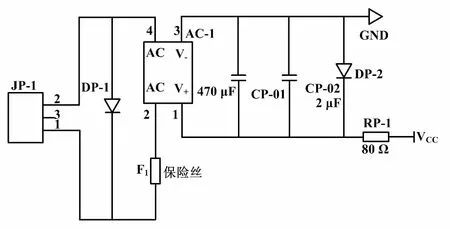

电磁超声的换能效率较低,因此需要提高供电电压才能够激发出超声波。国内外已有的激励系统使用的电压都是几百伏及上千伏,从安全角度和经济方面考虑,本设计高压模块输出电压为280 V左右,能够满足中小功率电磁超声换能线圈的换能需求。

设计中采用了整流桥的方式,直接将220 V交流电转换成需要的直流电压。直流高压发生电路如图2所示。在设计中,DP-1和DP-2分别是双向、单向二极管。这是一种新型高效的电路保护器件,具有极快的响应时间和相当高的浪涌吸收能力。设计中采用的整流桥是GBJ3506-BP,耐压值600 V;滤波电容CP-01选用耐压值450 V、容值470 μF的电解电容。同时,使用了去高频干扰电容CP-02。高频干扰既有电网的干扰又有电源的干扰,只需使用2 μF左右的无极性电容即可滤除高频干扰。

图2 直流高压发生电路

2.2 FPGA控制电路

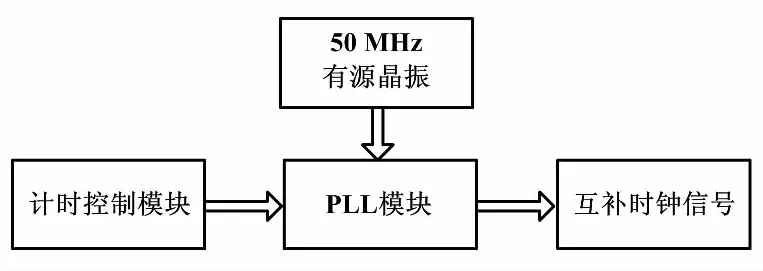

本设计采用了Altera公司的Cyclone IV E系列的EP4CE6E22C8可编程器件。该FPGA芯片功能强大、I/O端口资源丰富,可以实现多路输出。Cyclone IV E芯片有四个通用锁相回路(phase locked loop,PLL),对芯片时钟管理、外部系统时钟管理以及高速I/O接口,提供了可靠的[8]激励信号控制电路,如图3所示。

图3 激励信号控制电路

本设计采用输入时钟为50 MHz的有源晶振提供系统时钟信号。在模块的作用下,PLL将系统时钟信号转换成更加稳定且可以控制占空比、相位差的两路互补信号。PLL模块不是一直输出的,而是在计时控制模块的控制下每隔一定时间输出设定个数的时钟脉冲信号。这两路信号在空闲状态时均处于低电平,激励系统不会产生激励脉冲。相邻两组脉冲的间隔时间可以根据实际检测的要求进行调节,一般以1 s为宜。

2.3 光耦隔离和驱动电路

脉冲发生系统在工作时,会对前端控制信号产生干扰,引起控制信号不稳定,可能产生错误输出导致后端电路无法正常工作[9],因此,高频脉冲激励系统与FPGA控制电路之间需要电气隔离。故在FPGA控制电路后,添加光耦芯片进行隔离。光耦芯片选择的是TLP2348。它是一种超高速光耦,传输速度可达10 Mbit/s,输出电流50 mA。但这远远达不到驱动MOS管工作的要求,所以需要增加额外的驱动芯片使其正常工作。本设计采用了一款MOS管专用驱动芯片UCC27321。它是TI公司推出的一种新的MOSFET驱动芯片,能输出9 A的峰值电流,并快速驱动MOSFET开关管,在10 nF的负载下,其上升时间和下降时间的典型值仅为20 ns,工作电源为4~15 V。

FPGA控制电路产生预先设定个数的脉冲信号,经过光电耦合器后生成的信号与控制电路隔离,不会对前端控制电路产生影响。信号通过驱动芯片,产生可以驱动MOS管的脉冲信号。光耦隔离和驱动电路如图4所示。

图4 光耦隔离和驱动电路

2.4 全桥逆变电路

常规功率放大电路大都使用功放芯片、D类功率放大器以及半桥逆变电路。但这些功率放大电路具有输出功率低、效率低、开关损耗大的缺点。与之相比,本设计采用的全桥逆变电路可以很好地解决以上问题。设计使用的是威世公司生产的N型MOS管SIHP23N60E-GE3。它的最大漏源电压VDS为650 V,持续漏电流为23 A,最大脉冲漏电流为63 A,开启电压为2~4 V,正向导通电阻为0.158 Ω,导通时间为22 ns,关断时间为34 ns,适合作为中小功率脉冲发生器的开关管。

全桥逆变电路如图5所示。

图5 全桥逆变电路

由于开关管的工作频率很高,其导通和关断时间非常短,因此在开关管上可能会产生过压、过流现象,导致开关管无法正常工作甚至损坏。为此,在功率回路上采用了缓冲吸收电路。它是用来吸收开关管关断浪涌电压和续流二极管反向恢复浪涌电压,在某些应用中还可以减少开关管的损耗。其中,元件的选择应能够满足吸收缓冲的要求,电容应该选择无感电容器。电容值为:

(1)

式中:ID为最大漏极电流;Irv为最大漏记电压上升时间;tfi为最大漏极电流下降时间;VDS为最大漏极与源极电压。

需注意的是,电容C要足够大,使得开关管电压上升速度足够缓慢,以保证开关管不受冲击;而由于电容C的损耗,其值不能取得太大。电阻R没有特别的要求,R越小,C放电速度越快,只需保证电容C在下次开关管关断时放完电荷就可以了。因为吸收缓冲电路是在短路时工作,且放电电压是按指数规律下降的,故该电阻应选用较大功率的无感电阻器。电阻R为:

(2)

式中:ton为开关管的最小导通时间;C为吸收缓冲电路中的电容值。

稳压保护电路是防止系统带感性负载时,开关管在高速开关时导致驱动芯片引脚出现负电压,使负载电流流经驱动芯片,引起驱动芯片的损坏。设计中M1器件采用了稳压二极管D6防止反向电压过大,导致前端芯片过压损坏;电阻R107则是提供电荷泄放通道,同时防止静电损坏开关管,其他MOS管以此类推。快恢复二极管的反向恢复时间短(一般在几百纳秒时间范围内),具有正向导通电流大、反向峰值电压高的特点,这能够保证对开关管中产生的突波进行有效的吸收。

与激励系统内的阻抗相比,换能线圈的阻抗非常小,若不进行阻抗匹配很难使输出电压峰峰值达到最大,这将会使换能线圈的效率极低[10]。为此,使用了从线圈和涡流场相互耦合作用方面进行阻抗匹配的方法[11]。为了灵活控制处于活跃状态线圈的阻抗值,设计了由单层完全相同的线圈组成的堆积线圈。这种堆积线圈模型所产生的涡流场的阻抗是不变的,但线圈的阻抗可由所选定的线圈的层数加以控制。

2.5 反馈调节电路

为了防止全桥逆变电路中的电压和电流过大而影响系统安全,设计了反馈调节电路实时监测系统中的电压等参数,使用负反馈的方式来保证输出信号的参数稳定在设定的范围内。

3 试验结果

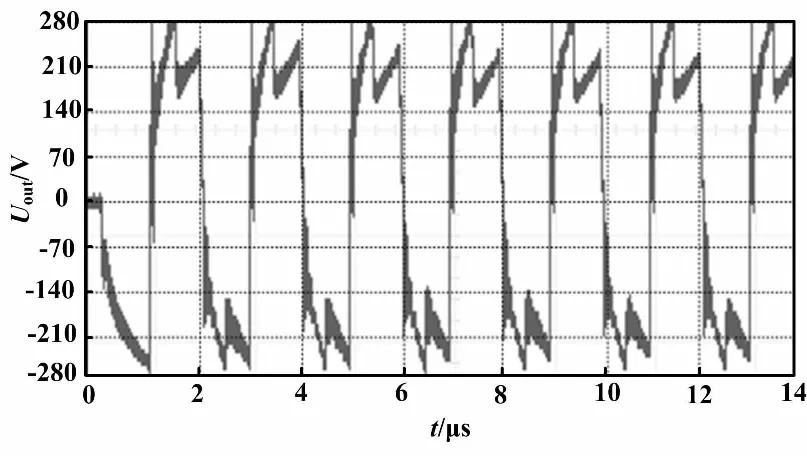

由以上硬件电路组装脉冲激励系统。其中,控制系统电路由FPGA的最小系统及其外围电路组成。对此脉冲激励系统进行测试,FPGA芯片设定的参数为激励频率500 kHz,脉冲个数为8个。从示波器上可以看到,激励系统可以输出8个接近方波的脉冲信号,其最大输出有效电压Vout约为260 V。激励系统输出脉冲信号如图6所示。

图6 激励系统输出脉冲信号

从图6可以看出,该系统能够按照设定参数输出符合要求的近似脉冲方波信号,达到激励换能器工作的要求。但由于缓冲吸收电路没有达到最佳状态,故图6中仍存在尖峰现象。下一步需要根据试验与计算设计出更加实用的缓冲吸收电路,使脉冲波形更加接近理想方波信号,保证换能器激发出实用的超声波。

4 结束语

为了使电磁超声检测技术在实际中得到更好的应用,设计了基于FPGA的电磁超声脉冲激励系统。在设计中,采用了全桥逆变电路实现从直流到交流的变换,同时输出高频脉冲信号;为了防止后端大电压电路对前端控制系统的影响,进而使整个系统出现不可预测的情况,采用了超高速光耦对前后端电路进行隔离;为了满足驱动MOS管的要求,采用了一款新型的专用驱动芯片驱动MOS管工作。系统可以根据检测对象的不同设定不同的输入参数,从而输出满足要求的高频激励脉冲,为进一步开发电磁超声检测仪器奠定了基础。