星间链路传输体制设计与仿真

2019-01-19朱爱民贾占彪

朱爱民,贾占彪

(陆军军事交通学院,江苏 镇江 212003)

0 引 言

星间链路是连接相邻卫星之间的通信链路。它将星座中的各卫星有机地联结为一体,使得系统内任何用户通信链路的建立都不需要地面通信网的支持。目前存在的卫星星座中,Iridium系统和Globalstar系统建立了星间链路[1-2],此外GPS卫星具有相互通信、跟踪的能力[3]。星间链路大大提高了系统的抗干扰和抗摧毁能力,扩大了系统的覆盖范围,便于管理和组成全球无缝网络。对于星座内的卫星来说,一般需要建立的星间链路包括与同一个轨道平面内卫星之间的星间链路和与相邻轨道平面内的卫星之间的星间链路。如果星座是立体多层次的,还有可能需要建立与不同层次轨道内卫星之间的星间链路。在星座运行过程中,建立星间链路的卫星间的星间距离、方位角与仰角是随时间变化的。星间链路能否建立与卫星间的空间距离、方位角和仰角相关。而星间链路能否保持,则与卫星间的空间距离、方位角和仰角随时间的变化率相关[4]。

直接序列扩频通信系统具有很强的抗干扰能力和通信的隐蔽性,特别适合星间链路应用。本论文针对某工程项目的需要,设计了一种星间链路传输体制,以期可靠地实现星间测控和数据传输。该体制通过直接序列扩频通信的方案,大大增强了抗干扰能力。编码调制方式采用卷积编码正交相移键控(QPSK)信号,采用数据辅助的方法实现对接收信号频偏和码相位的估计,并对接收信号进行校正。仿真结果表明,该算法在低信噪比下能够有效实现信号同步与传输。

1 传输体制设计

用户信号体制的选择直接取决于用户星的需求,包括信号的产生方式、调制方式、解调方式等。星间通信信道是频带受限和功率受限的非线性信道,要求选择频带利用率和功率利用率都较高的传输体制。

1.1 星间链路通信系统信号设计

根据电波在空间的传播特性,星间链路信道建模如图1所示。该模型将信道分为空间损耗、多普勒频移、噪声3个模块。信号设计的目标是在该信道模型下,减小信息时延,扩大通信容量,提高星间链路通信的可靠性。

图1 星间链路信道噪声模型

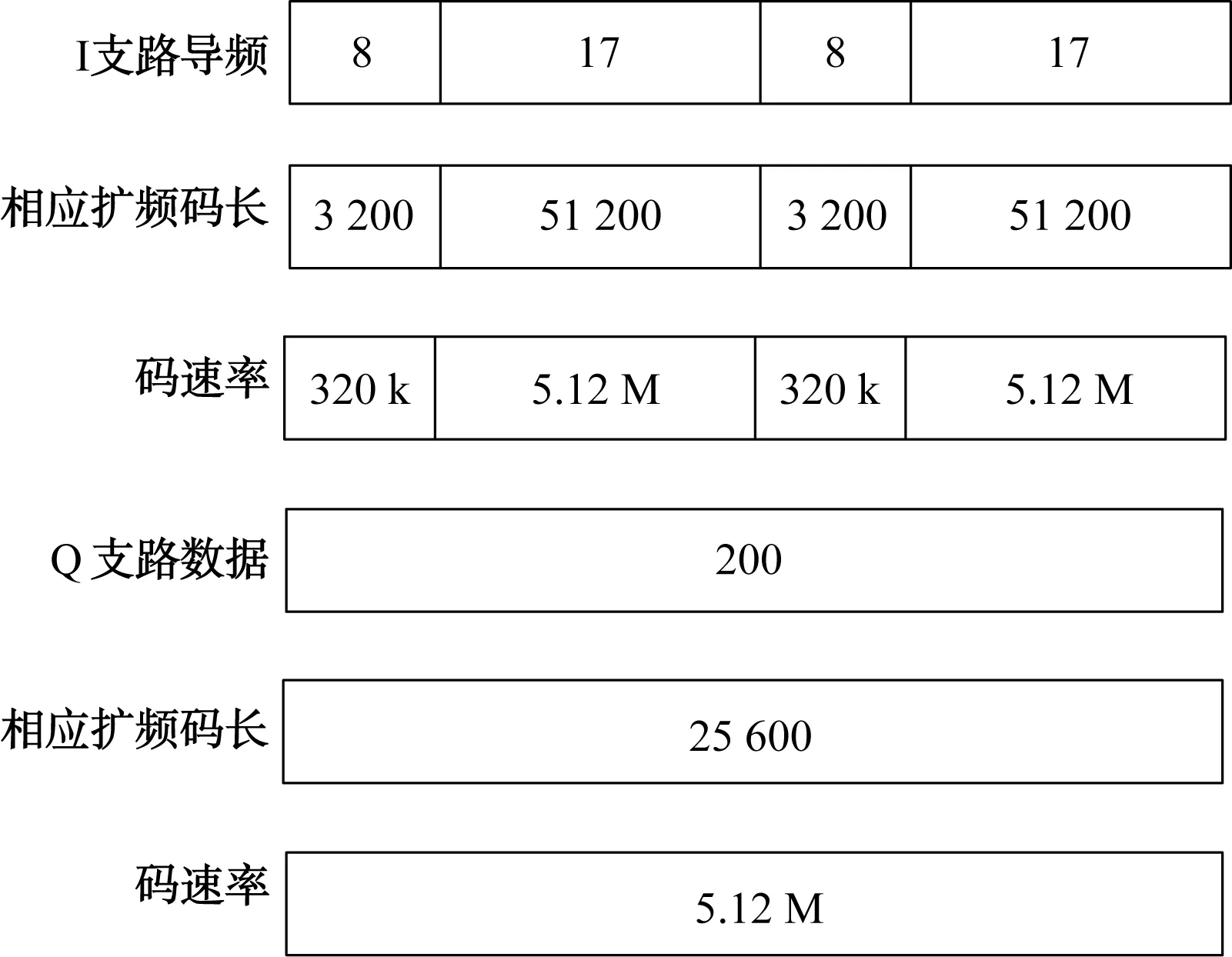

为满足星间链路通信多普勒变化率和误码率的要求,便于信号的捕获和跟踪,对信号进行设计,如图2所示。

图2 星间链路通信信号设计

由信号体制设计可知,I支路为导频支路,导频支路发全1。导频支路又分为高低速码。低速码段用于码序列的初捕,高速码段用于扩频码的精确跟踪。Q支路为数据支路,信息经过卷积编码后扩频输出。

1.2 星间链路通信系统发端设计

星间通信使用全向天线,接收机灵敏度较低。星间链路采用内置导频的方法实现码片同步和载波同步,并通过使用卷积码和正交相移键控(QPSK)调制满足误码率要求。

如图3所示,I路发送导频数据,之后与扩频码进行扩频,得到扩频序列,并经过异步内插成形滤波器实现成形,最后通过数模转换(DAC)将数据输出。Q路为数据支路,数据经过卷积编码后与扩频码进行扩频,得到扩频序列,经过异步内插成形滤波器实现成形,最后通过DAC将数据输出。

图3 发端实现框

1.3 星间链路通信系统收端设计

完成轨道间链路目标的捕获及跟踪,是星间链路建立的基础,是确保中继星与用户星通信服务的关键。收端设计的目标是对扩频码进行准确的捕获和跟踪,同时实现载波同步,最终得到正确的译码输出。如图4所示,中频数据经过数模转换(ADC)采样后进行中频采样,经过定频数字下变频(DDC),然后通过积分梳状级联(CIC)(1/4)抽取滤波器,经过Farrow异步内插修正并下变频,之后经过匹配滤波后将数据分为2路:一路为高速码,用于数字锁相环(DLL)和载波环;另一路为低速码,用于捕获。信号捕获后,可以得到载波频率和码相位。此时,启动DLL闭环跟踪。数据送到载波环处进行精确跟踪。载波环跟踪误差和捕获的频偏共同反馈到DDC处,消除多普勒频移。锁相环相位与I、Q数据复乘后,得到精确的Q路数据,然后通过串转并,将数据送入维特比译码器进行译码。

图4 收端实现框图

2 伪码捕获与载波同步的实现

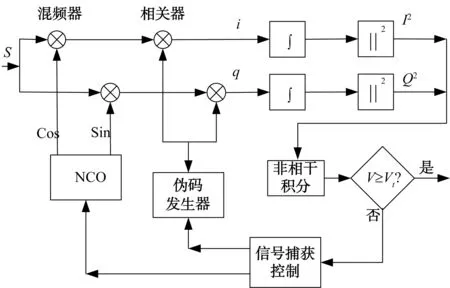

针对伪码同步的实现,本论文设计的传输体制结合了几种传统捕获方法的优点,进行信号的优选,设计了特殊且巧妙的捕获结构。如图5所示,组合序列通过2次相关后进行积分取模等操作,可以同时得到载波频率与码相位。

图5 信号捕获电路

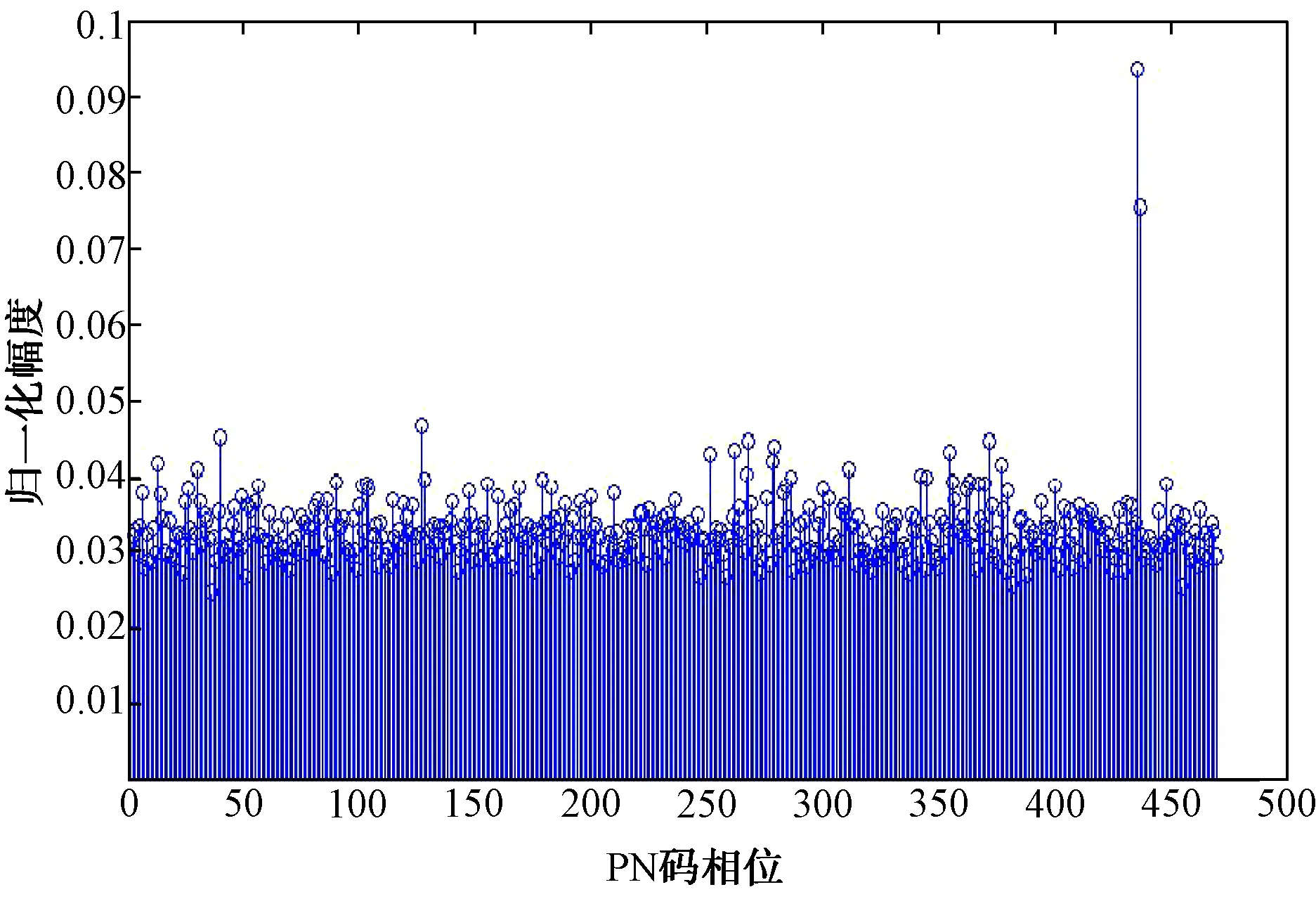

对伪码信号的捕获进行仿真,得到信噪比在19 dB时的伪码捕获结果,如图6所示。由图6可知,伪码捕获点处的信号能量明显大于其他位置。可见,该方案可有效完成捕获操作。

图6 信噪比为19 dB时的捕获结果

针对载波同步的实现,本论文使用分离的二阶锁频环辅助三阶锁相环的结构。为了减少环路时延,将传统的锁频环与锁相环误差同时反馈改为锁相环内部反馈,减小了环路时延。最后,给出了不同载噪比下环路的收敛过程。

由于接收卫星信号的伪码相位未知,相干积分值I和Q可分别表达成:

I(n)=aD(n)R(τ)sinc(feTcoh)cosφe+nI

(1)

Q(n)=aD(n)R(τ)sinc(feTcoh)sinφe+nQ

(2)

(3)

如果舍去噪声项nI与nQ,则I(n)+jQ(n)的幅值为:

(4)

式(4)表明,接收载波与复制载波之间的相位差异φe不影响非相干检测[5]。

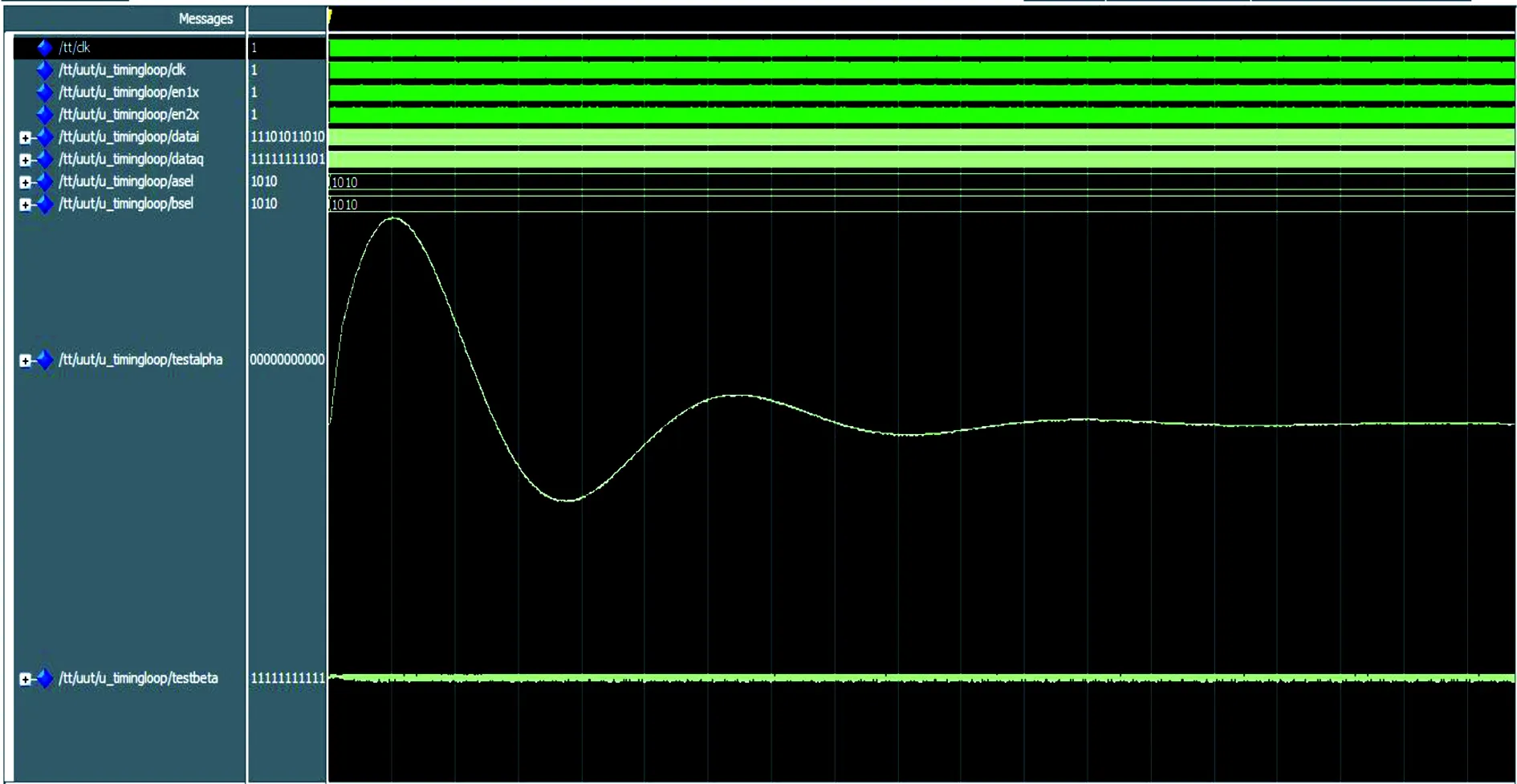

内插之后的数据,经过匹配滤波后,每个符号2个样点。经过码相位搜索后,找到真正的码相位。通过超前与滞后之间的差值鉴相,鉴相误差进入二阶环路滤波器,其输出误差信号反馈到内插NCO处,调整环路滤波器参数后[6],如图7所示。二阶环路滤波器的收敛曲线,其中Alpha可以看到环路明显收敛曲线,Beta在0附近抖动。

图7 DLL环收敛曲线

由上述载波环开环,有剩余频偏时,输入载波环的导频I支路为余弦,数据Q支路为正弦。此时,环路要锁定。要确切知道这一时刻的相差和频差,需要对IQ数据进行鉴相鉴频。其中:

I=cos(φe)

(5)

Q=sin(φe)

(6)

若使用arctan(Q/I)鉴相器可得相位误差:

φe=φe

(7)

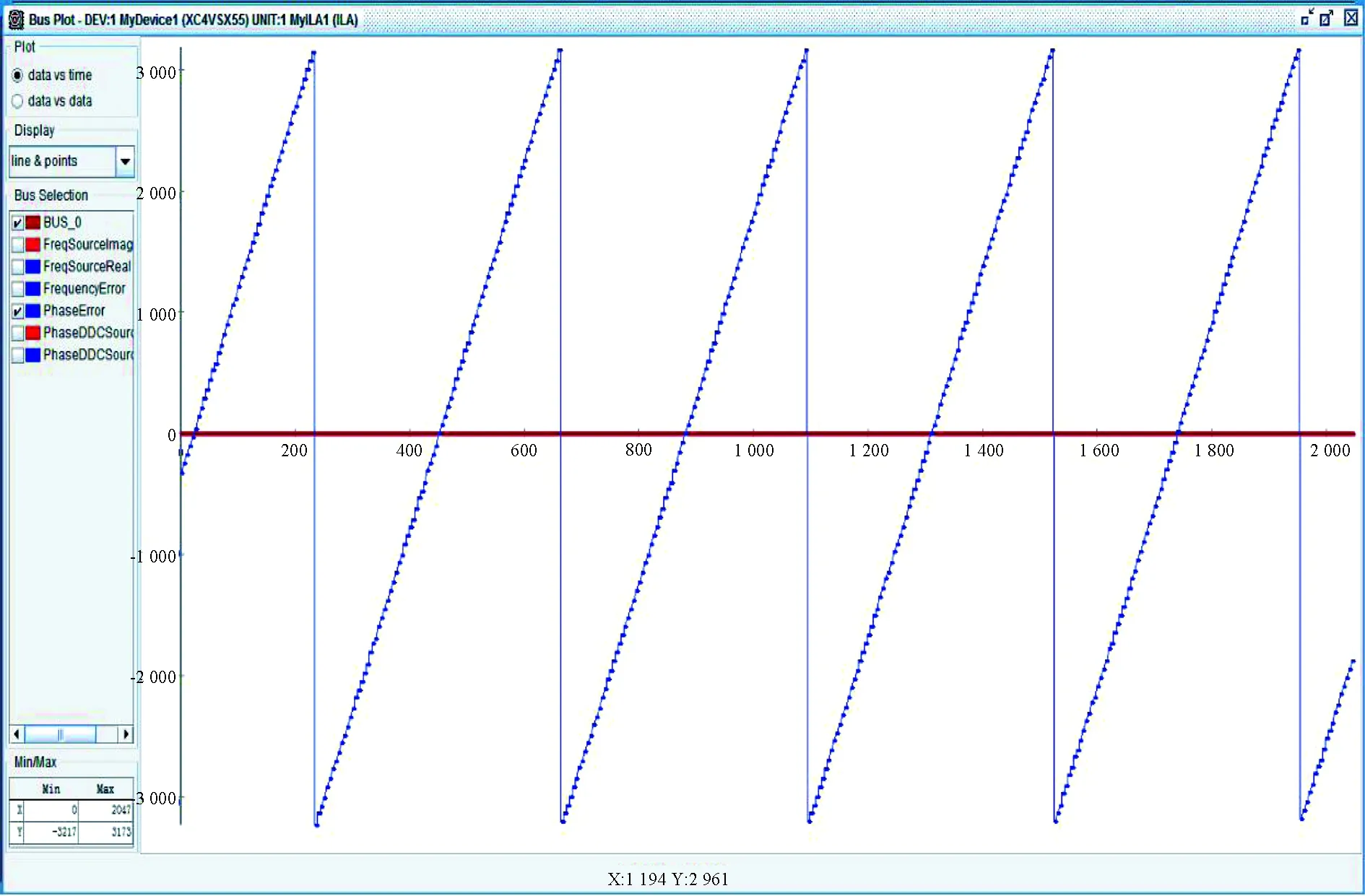

由式(7)可以得出,鉴相器保持线性工作,其实际鉴相结果如图8所示,鉴频结果如图9所示。可见,它的鉴相结果保持线性输出,鉴频输出接近线性。

图8 锁相环鉴相输出

图9 锁频环鉴频输出

3 结束语

星间链路通信是跟踪与数据中继卫星最重要的组成部分,其可靠的通信能力是完成星间测控和数据传输的基础。由于星间通信信噪比很低、动态范围大[7],如何提高通信系统的可靠性成为本论文研究的重点。本论文在相关文献以及项目的基础上,研究星间通信系统信号处理部分,其中最主要的是伪码捕获与载波同步的实现。

本文方案已经过modelsim仿真和硬件下载验证。处理平台采用Xilinx公司Virtex-4现场可编程门阵列(FPGA)系列产品中的XC4VSX55,开发软件选择ISE14.7。捕获的最大频偏为1.6 kHz,频率搜索带宽fbin可达采样速率的2/3,捕获时间不超过6 s,捕获灵敏度可以达到-141 dBm。