基于项目引导和过程考核的FPGA实验教学改革研究

2019-01-10李营吕兆承

李营 吕兆承

摘 要:为了激发学生的学习兴趣,提高学生的综合实践与创新能力,根据工程教育理念和能力培养要求,结合FPGA实践性强的特点,坚持“重基础与技能,求综合与创新”的实验教学改革思路,从课程的实验内容、教学方法、实验条件以及考核评价方式等方面进行教学改革,引入“项目引导,任务驱动”的教学方法与模块化实验设备,建设FPGA网上教学资源,制定具体、合理、规范的评价方式,加强对学生实验过程的指导与考核。实践证明,改革取得了良好的教学效果,提高了实验教学的水平与质量,为今后的教学改革积累了宝贵经验。

关键词:工程能力;任务驱动;模块化设计;过程考核;FPGA;实验教学

中图分类号:TP39;G642文献标识码:A文章编号:2095-1302(2019)12-0-04

0 引 言

伴随着电子设计自动化技术的迅猛发展,利用FPGA进行数字系统的开发已广泛应用于通信、航空航天、医疗电子和汽车电子等诸多领域,该技术已成为现代集成电路设计验证的主流[1]。FPGA是一种新型的电路设计技术,通过软件编程设计硬件电路,能够极大地提高电路设计的效率与可靠性,减轻设计者的劳动强度,成为越来越多领先技术的系统解决方案[2],许多院校根据行业发展需要都开设了FPGA课程。

FPGA课程的专业性与应用性较强,学习难点相对较大,给课程教学带来了较大挑战。从我校近几届电子信息类专业毕业生的知识掌握情况来看,很多学生在学完课程之后仍然出现不具备FPGA设计能力、设计缺乏完整性等问题。面临就业压力,为了提高自身竞争力,一部分学生花费大量的金钱和时间自费到社会培训机构进行FPGA方面的学习。因此,开展FPGA相关课程教学改革研究具有重要的现实意义[3-5]。

1 FPGA课程现状及存在的问题

FPGA是一门理论与实践紧密结合的课程,要求学生不但要掌握硬件描述语言,还要熟悉硬件电路的原理与结构,具备良好的编程语言和数字电路基础,一般安排在C语言、数字电路、单片机等课程之后开设。我校FPGA课程授课课时数是51学时,实验课课时数是15学时,实验课时占到了总学时的三分之一,实验教学环节对课程的教学效果影响至关重要。同时,实验教学是工科专业人才培养中的重要环节,对学生的工程素质与创新能力培养具有重要作用[5]。虽然FPGA课程的实践性很强,但在教学过程中未能充分体现课程的这一特点。

(1)理论与实验课程教学各自独立进行,使得理论变得比较抽象,不利于学生理解,影响了学生学习理论知识的积极性与主动性,相互配合的教学影响力甚微。

(2)实验内容多以验证型实验项目为主,使得学生在实验过程中按照实验手册的流程走过场,仅编写几行代码,很难提高学生的创新能力与主动性。

(3)实验设备存在缺陷。实验教学平台通常采用FPGA实验箱,这种实验箱采用一体化结构,硬件集成度高,功能上难以根据需要继续扩展,只要选择合适的工作模式,学生无需过多了解其硬件组成与连接,参考说明书分配管脚就可进行硬件验证,学生的实际动手能力与分析解决问题的能力并不能得到提高,感受不到设计电子产品的乐趣。

(4)实验考核方法单一,主要以实验报告、出勤率为依据,这种考核模式不能使学生真正从思想上提高培养动手的意识,无法真实反映学生的实际能力。

2 实验教学改革探索

综合上述问题,针对应用型人才培养定位,从FPGA课程工程实践的重要性出发,结合近几年的教学经验,提出以下几点教学改革措施。

2.1 优化实验教学内容,以具体任务为导向

改革前开设的实验项目都是常规的验证性实验,与开发使用的应用系统存在很大的差距,而且相互独立,缺乏综合性与系统性,因此学生只要机械模仿,所做的实验结果完全一样,不利于学生独立思考与解决问题能力的培养。根据FPGA课程与应用型本科学生的特点,结合行业新技术发展与岗位技能需要,以完成典型任务为主线编排教学内容,FPGA实验教学内容的安排见表1所列。

整个实验过程以具体任务为导向,系统地介绍数字系统设计开发环境、开发工具软件、Verilog语言以及应用、组合和时序逻辑电路设计、数字系统设计实践等,由浅入深、循序渐进地安排8个实验项目,增加综合设计性实验,增进实验内容的趣味性,最大限度地吸引学生的注意力,提升学生的学习兴趣。项目1主要学习FPGA开发软件Quartus及配套实验箱的使用,通过简单的门电路的设计,使学生从实践中了解现代数字系统设计所需要的硬件、软件开发环境,并逐渐学会运用Quartus进行数字电路设计,同时让学生在实践中由从直观到抽象、由外到内逐渐理解FPGA以及相关概念。项目2学习Verilog的语法、常用语句及简单组合逻辑电路的设计,使学生从实践中了解Verilog硬件描述语言的基本概念、结构特点、数据类型等,体会什么是组合逻辑电路,如何用Verilog完成组合逻辑基本的建模,逐步掌握清楚几种常用组合逻辑电路的原理以及建模方法。项目3-5主要学习简单时序逻辑电路的设计,使学生从实践中熟悉典型时序电路的Verilog设计方法,建立同步电路设计概念。项目6-7是数字系统设计综合任务,设计难度增加,但每个任务都不是孤立的,与前面的任务具有一定的联系,使学生在实践中掌握数字系统设计与验证的流程,掌握top-down的设计思想,ModelSim仿真工具的使用等,从而提高设计能力,使学生在实验中有较丰富的收获。实验中每个项目都由具體任务入手,引入相关的知识点,通过技能训练引出相关概念、设计技巧,体现做中学、学中练的教学思想。

2.2 更新教学理念,采用基于任务驱动式的教学模式

传统的实验教学以教师为中心、以课堂为中心、以教材为中心,简单地使学生按照教师的安排与讲授得到一个结果,学生缺乏思考与协作,这种方式过于枯燥,影响FPGA课程的教学效果。而基于任务驱动的教学模式是一种以实践为导向、教师为主导、学生为主体的教学方法,从职业发展变化的实际需要出发,选择典型的项目为教学内容,通过师生共同实施项目内容进行教学活动。这种教学法在项目任务完成过程中,能使学生积极地通过持续探索、团队协作参与学习、自觉地进行知识建构、设计与创造,是一种具有全新教学理念的教学模式[6],该模式的教学流程见表2所列。

本文以设计型实验项目数字钟设计为例进行阐述。

(1)任务描述

设计一个简易数字钟,实现“小时”“分钟”“秒钟”的计时与显示,时间显示采用七段数码管显示器。

(2)知识铺垫

根据常识,“秒”“分”与“小时”之间存在各自独立又相互联系的计数与进位关系,“秒”“分”的计数模式相同,每计满60个时钟清零并重新开始计数,相当于一个六十进制的计数器。而“小时”相当于一个二十四进制的计数器。

(3)方案制定

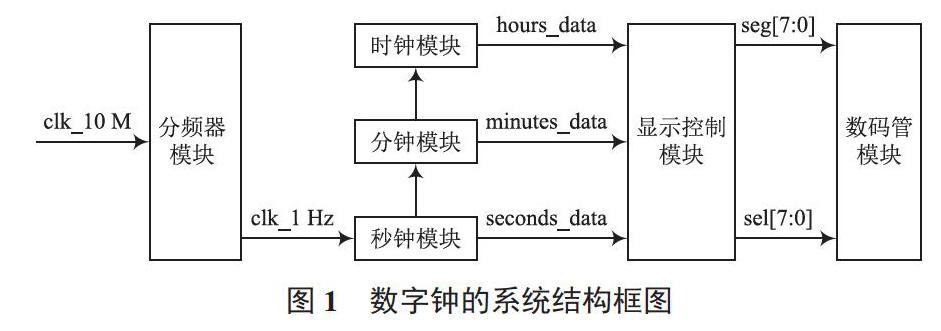

学生根据设计要求在查阅数字钟有关资料的基础上,提出任务所需模块,得出数字钟的系统结构框图,如图1所示。

(4)项目实施

在设计过程中,先采用Verilog设计底层模块,包括分频器模块、计数器模块、显示控制模块,顶层模块通过模块调用的方式完成。通过上述环节的训练,学生在任务分析、系统划分、模块设计等方面都得到了全面的锻炼,建立了系统设计的整体概念,掌握自顶向下的设计方法,进一步熟练Quartus软件的操作与程序调试方法。

(5)评价总结

学生自我检查、自我评价,分析设计优缺点,提出进一步改善要求。

(6)知识拓展

对于学有余力的同学,在完成上述实验内容的基础上,安排两个扩展任务:

①增加闹铃功能,在闹钟定时到时,启动闹铃响,闹铃音为急促的“滴滴滴”音,响声延续30 s;

②设计一个多功能数字钟,除了计时外,增加校时等[7]功能。

2.3 改善实验硬件条件,利用开发板进行模块化设计

传统的一体化FPGA实验箱存在价格昂贵、维修保养成本高、体积大、不便携带等诸多弊端,我校积极建设“FPGA口袋实验室”,利用FPGA开发板进行开放、自主实验教学模式的改革。硬件购买只包含FPGA芯片、电源等必要电路的最小系统开发板,其I/O都以插针形式引出,以方便与外围电路的连接。外围电路则以模块的形式做在电路板上,如拨码开关、数码管、LED点阵等。学生实验时,根据不同的实验项目,选择相应的外围模块与FPGA开发板在面包板上搭建而成。这种模块化的设计能结合实际教学以及学生的情况进行随意更改,扩展性强,灵活性高,增强实验教学的效果[8]。此外,相对于实验箱,FPGA板卡价格便宜,体积小,方便携带,课上、课下都可以由学生负责保管使用,学生能够随时随地验证理论课程的教学内容,并在板卡上运行自己的设计或创意,有利于培养学生的自学能力、实践能力及创新能力。这种“口袋实验室”在实验教学中融入了“模块化”“工程化”“自主化”的思想,弥补了课堂学时有限的不足,可以轻松实现电子芯片的设计,并且可以现场观察实验结果,大大提高了学生学习FPGA的效率和热情。

2.4 改革考核评价方式,加强项目过程指导和考核

实验课程强调实验的操作过程,学生在实验课程中所取得的效果与实验过程管理密切相关[5]。将学生的实验过程直接与实验成绩挂钩,并将实验课堂表现作为实验考核成绩的重要组成部分,为此提高了平时考核成绩的比重,FPGA实验课程考核方式及权重如图2所示。平时考核选取所有实验项目成绩的平均值,每次实验项目的成绩根据学生平时的考勤、课堂表现、课后作业(实验报告)等情况,由指导教师按照百分制分别给出评定成绩,并记录在实验过程材料中。期末考核时,抽取难度适中的实验内容,要求学生进行实际操作并现场验收考查学生,这种考核会更加注重学生的实验过程。良好的过程管理能够促进学生的学习效果,提高学生的实验积极性与主动性[8]。

“预习环节”中,为了保证实验教学效果,要求学生在实验前通过阅读实验讲义,网上查询相关资料,针对实验原理与实验内容提出若干思考题及预习要求,引导学生在弄懂实验原理的基础上做好充分的准备工作,如模块划分、编写程序、进行仿真等。

“实验过程”中,让学生独立、主动地完成项目。当学生遇到问题时,教师应鼓励学生自行解决实验中遇到的问题,或者与同学相互讨论,相互指导。若仍然解决不了则向教师求助。对于共性问题,教师将其归纳总结,列出一个常见问题解答的提纲,交给学生或展示给学生。对于个性问题,教师单独指导[8]。每个实验项目结束后,根据学生在操作过程中的综合表现,给出相应的课堂表现成绩,检查学生的掌握情况。FPGA实验课堂表现评分见表3所列。

“实验总结”中,学生把在实验过程中得到的数据,如Verilog程序、RTL级电路、仿真波形以图片的形式打印出来,粘贴在实验报告中,作为实验数据进行讨论,分析测试数据的正确性,验证设计功能是否得以实现,并记录设计过程中程序调试的故障现象及处理方法。其目的在于引导学生做完实验后,加深对理论与现象间内在联系的理解。

2.5 引入“对分易”微信教学平台,建设课程网上教学资源

为了拓展课堂教学资源,丰富FPGA课外相关知识,借助“对分易”微信教学平台开设FPGA技术课程,将课程常规资料与相关资源分享至该平台。该平台包括考勤、课程资源、作业、微信消息、在线练习等模块,涵盖了课上及课后讲解、练习、分组、讨论、作业等各个环节,是实验课堂的有力辅助手段[9-10]。例如,由于实验学时有限,有小部分学生不能按照要求完成设计,教师可将实验过程录制成小视频,上传到“对分易”平台的“课程资源”中。学生课后可随时多次回顾教师的操作过程。通过实验教学操作视频,一方面可提高学生的学习效率,另一方面,教师可将宝贵的教学时间用于教学难点的指导与对学生能力的考核,促进实验教学顺利开展。该微信教学平台的使用方便学生课外自主学习,使学生的学习不受时间与地点的限制,促进每个学生个性化成长。

3 结 语

通过近几年的改革实践,学生的工程应用能力与创新实践能力得到了较大提高,很多学生参与了教师的科研项目,并主持了安徽省和学校的大学生创新实践活动,发表了学术论文并申请了专利,提高了其在就业市场的竞争力,取得了良好的教学效果。但是还有一些问题有待解决,未来应加强师资队伍建设,通过授课教师到企业挂职锻炼参与项目合作,开展与企业工程师的互动式专题研讨等形式,提升教师的工作实践能力,并进一步完善实验室管理制度,通过科学有效的实验室管理,提高实验仪器、实验室的利用率,营造出一种积极向上的学术研究、技术开发氛围。

参 考 文 献

[1]蒋俊华,王蓓.基于FPGA设计及应用课程的理论和实践教学方法探索[J].商丘师范学院学报,2014,30(12):128-130.

[2]李营,殷小航,吕兆承,等. 基于FPGA的VGA汉字显示器设计[J].延边大学学报(自然科学版),2018,44(4):365-368.

[3]胡靖,杜西亮.基于FPGA技术的课程教学改革探索(高教研究与评估)[J].黑龙江教育,2015,11(3):35-36.

[4]孟祥斌,尹常永,郎东革.EDA课程项目教学法的应用研究与实践[J].沈阳工程学院学报(社会科学版),2013,9(1):113-115.

[5]王墨林,戚昊琛,魯迎春,等.FPGA课程创新实验教学体系的实践[J].实验科学与技术,2018,16(4):137-139.

[6]赵兴康.基于项目的教学方法在远程教育教学中的应用[J].湖北广播电视大学学报,2011,31(2):15.

[7]王静霞,余菲,温国忠.FPGA/CPLD应用技术(Verilog语言班) [M].2版.北京:电子工业出版社,2014:237-247.

[8]赵艳华.EDA课程教学改革的探索与实践[J].设备管理与维护,2016,37(2):15-17.

[9]边玮玮,戚明颖,綦慧敏,等.基于对分易软件的对分课堂在高校化学课程中的应用探索[J].中国教育技术装备,2018,32(10):26-28.

[10]徐运武,李艳.基于FPGA项目式技能培训的“电子信息”课程体系改革与探讨[J].物联网技术,2018,8(2):115-117.