基于Arria10的高速Serdes接口设计

2018-12-29杜冰馨吴海洲

杜冰馨,吴海洲

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

10.3969/j.issn.1003-3114.2018.01.21

杜冰馨,吴海洲.基于Arria10的高速Serdes接口设计[J].无线电通信技术,2018,44(1):99-102.

[DU Bingxin,WU Haizhou.Design of High-speed Serdes Interface Based on Arria10 [J].Radio Communications Technology,2018,44(1):99-102.]

基于Arria10的高速Serdes接口设计

杜冰馨,吴海洲

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

随着航天测控技术的飞速发展,系统传输速率成为了限制系统整体性能的关键因素之一。Serdes接口以其传输速率高、抗干扰能力强、功耗低等优点,迅速成为高速传输接口发展的主流。针对串行链路速率及带宽不断提高的问题,提出了一种基于Arria10 FPGA芯片的高速Serdes接口模块的设计方案。通过板间的高速数据传输实验,使用Transceiver Toolkit验证了经过PMA参数优化后的单路10 Gbps的传输速率以及最高768 Gbps的总传输带宽,解决了高速传输系统对传输带宽要求高的问题,为系统实现高速数字开关矩阵的设计提供了技术支持。

高速Serdes接口;Arria10;Transceiver Toolkit;PMA参数;数字开关矩阵

TN911

A

1003-3114(2018)01-99-4

发稿日期:2017-11-08

国家高技术研究发展计划(863计划)项目(2013AA122101)

DesignofHigh-speedSerdesInterfaceBasedonArria10

DU Bingxin,WU Haizhou

(The 54th Research Institute of CETC,Shijiazhuang 050081,China)

Nowadays,with the rapid development of TT&C technology,system transmission rate becomes one of the key factors that restrict the overall system performance.Furthermore,Serdes interface is quickly becoming the mainstream technology of transmission interface.It has the advantages of high transmission rate,strong anti-jamming capability and low power consumption.Considering the increasing of data rate and bandwidth of serial link,a design scheme of high-speed Serdes interface module based on Arria10 is proposed.The experiment of high-speed data transfer between boards validates,by using Transceiver Toolkit,a data rate of 10 Gbps per channel and a total bandwidth of 768 Gbps after optimizing the PMA parameters.The design and experiment results meet the requirement for wide bandwidth in high-speed transmission system and provide a technical support for the development of high-speed digital switch matrix.

high-speed Serdes interface;Arria10;Transceiver Toolkit;PMA parameter;digital switch matrix

0 引言

随着通信测控系统的发展,系统对数字开关矩阵的容量、传输速率、集成度等方面有了更高的要求。高速Serdes接口以其高带宽、高速率的传输特点,迅速成为实现高性能数字开关矩阵的一项关键技术[1-2]。Serdes接口芯片将低速并行信号转换为高速串行LVDS信号通过串行链路进行传输,同时也能将接收高速串行LVDS信号正确地转换为低速并行信号[3-4]。

Lattice公司和ALTERA公司分别于2009年推出了内嵌Serdes的FPGA产品[5-6]。随后TI公司也研发出了系列Serdes接口芯片,如TLK2711A、TLK3101,文献[7]提出了基于TLK2711的高速数据串行传输方案,TLK2711可支持的单对差分线最高传输速率为2.7 Gbps,最大传输带宽为32.4 Gbps。2016年ALTERA公司又推出了内嵌Serdes的Arria10系列FPGA,其收发器功耗低,具有高带宽,高吞吐量和低延迟的传输性能[8]。

本文基于Arria10系列FPGA芯片设计了一种Serdes接口电路,单对差分线传输速率达到10 Gbps,96对差分线的最高有效传输带宽可达768 Gbps。该接口电路具有VPX通用化设计标准,可实时重构,为实现高性能数字开关矩阵提供了技术支持。

1 Serdes接口电路总体架构

高速Serdes接口电路设计方案的结构框图如图1所示,它包含的主要模块有:电源模块、时钟模块、Serdes接口模块、配置模块和光模块5部分组成。电源模块为板上所有其他器件提供所需的各种电压;Arria10系列10AX115U2F45型号FPGA为核心Serdes接口模块;时钟模块为FPGA提供高精度的稳定时钟[9];配置模块用于对FPGA进行配置;光模块实现光电信号转换,从而通过光纤与外部节点设备进行光信号传输交换功能。

图1 Serdes模块总体架构

2 Serdes模块的设计

Serdes接口模块的核心芯片为Arria10系列的10AX115U2F45型号FPGA,该芯片提供96条高速全双工串行收发器通道,具有8B/10B编解码器,在芯片到芯片收发和背板收发时,能支持的最高速率分别为15 Gbps和12.5 Gbps[10]。

整个Serdes接口模块设计中的主要关键技术有:上电顺序符合要求的电源电路设计、与外围器件电平匹配电路设计、transceiver时钟网络设计以及高频板PCB设计等4个方面的内容。

2.1 电源设计

10AX115U2F45需要提供的电压有:核电压VCC +0.95V、外设电压VCCP +0.95V、收发器发送模拟电压VCCT_GXB +1.03V、收发器接收模拟电压VCCR_GXB +1.03V、存储配置电压VCCERAM +0.95V、配置电压VCCPGM +1.8V、IO电压VCCIO +1.8V、PLL模拟电压VCCA_PLL +1.8V、发送器缓存模拟电压VCCH_GXB +1.8V以及IO预驱动电压VCCPT +1.8V[11]。各种电压的上电和关电排序要求,将上述电源排序分为3个电源组。

第1组电压为VCC、VCCP、VCCERAM、VCCT_GXB、VCCR_GXB;第2组电压为VCCPT、VCCH_GXB、VCCA_PLL;第3组电压为VCCPGM、VCCIO,第1组所有电源必须上电到最低0.81 V后第2组才能上电,第2组所有电源必须上电到最低1.62 V后第3组才能上电,且上电排序必须满足标准或快速POR延迟时间[12]。本设计采用TI公司的电源监视芯片TPS3808G09和TPS3808G18来控制电源模块的上电顺序,该芯片通过在相应的引脚连接不同容值的电容可控制输出加电控制信号的时间。

2.2 外围电路电平匹配设计

10AX115U2F45的FPGA通用I/O的电平为1.8 V,本设计中FPGA主要外围电路是光模块,完成光电信号的转换,从而通过光纤与外部设备进行交互传输。光模块的电平为3.3 V,因此需要桥接电平转换芯片,本设计选用的是TI公司的SN74AVCB164245VR芯片完成的1.8 ~3 V的相互转换[13]。

2.3 Transceiver发送器时钟网络设计

发送器时钟网络将时钟从发送器PLL布线到发送器通道,它对发送器通道提供了串行器的高速串行时钟和低速并行时钟。10AX115U2F45发送器具有3种类型的发送器时钟网络,分别是x1时钟线、x6时钟线、xN时钟线。其中,xN时钟线可布线多个收发器bank中的收发器时钟。xN时钟网络的最大通道跨度是包含驱动PLL和主CGB的收发器bank向上的2个transceiver bank和向下的2个transceiver bank,即最多30个通道可共用一个绑定或非绑定的xN时钟网络[14]。

2.4 高频板PCB设计

本设计中信号工作频率为10 GHz,为典型的高频/数字多层板结构,这种典型结构对于板材要求很高,建议选用介电常数相当稳定、损耗因子较低、耐热特性更好的高频板材,如RO4350、M6或TU-872等材质。另外,高频PCB完整性设计的关键是布局和布线[15]。进行布局时应综合考虑散热和传输线间的串扰等问题,进行布线时应尽量使用较宽的走线,避免长距离并行布线。

3 仿真实验

基于Arria10的高速Serdes接口电路板卡如图2所示,内嵌Serdes的Arria10 FPGA可将接收到的数据做后处理,也可作为高速信号切换的核心器件直接通过光纤将数据传给节点设备。实验中,对板卡的高速Serdes接口进行了8 Gbps、9 Gbps、10 Gbps三种速率的传输性能测试。为保证信号质量,采用Quartus II的Transceiver Toolkit来优化PMA参数,并对信号添加更完备的设置[16]。

图2 基于Arria10的多路高速Serdes接口板卡

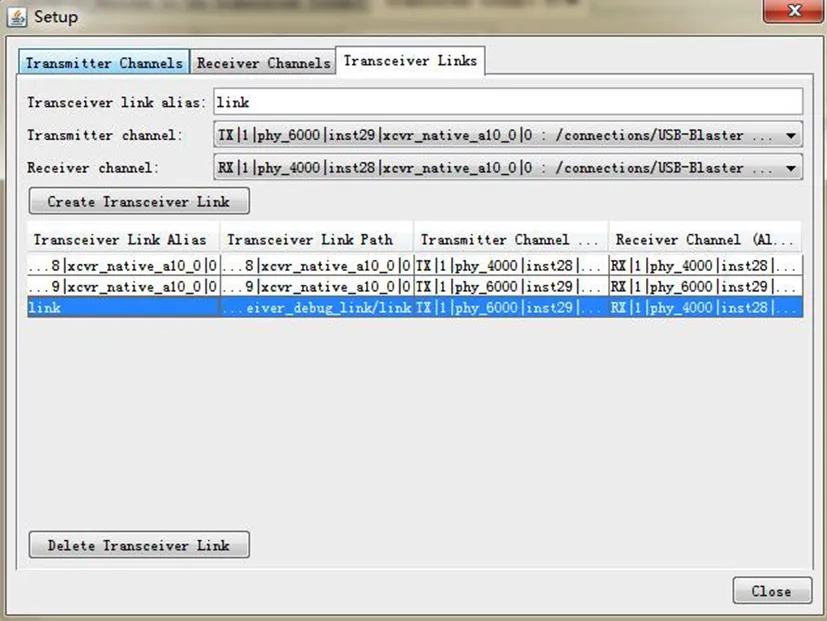

将工程导入并下载到FPGA中,Transceiver Toolkit会自动生成一些共用一条收发通道的链路,我们也可以手动建立或删除收发器链路,如图3所示。

图3 收发器链路建立图

设置测试码型为PRBS31,当VOD、Pre-emphasis、VGA、DC增益、Equalization、DFE等PMA参数未经优化调整,均为系统默认值时,3种速率传输下的误码率情况比较如表1所示。

表1 默认PMA参数下3种速率的误码率

速率8Gbps9Gbps10Gbps误码率(数量级)10-1410-1110-8

由表1可知,当速率为9 Gbps和10 Gbps时误码率较高,这说明未经优化调整的PMA参数无法满足传输性能的要求。为了提高传输性能,需要使用Transceiver Toolkit对PMA参数进行优化,从而补偿信号在传输过程中的损耗。

速率为9 Gbps时,增大VGA参数值,可使误码率降低为10-14数量级。速率为10 Gbps时,仅优化VGA参数值测得的误码率为10-11数量级。当同时优化VGA参数值、调整Equalization模式并开启DFE模式后,误码率明显降低。

表2为PRBS31码型在8 Gbps、9 Gbps、10 Gbps速率下PMA参数调整的对比表。根据上述传输实验可知,在PMA参数优化的条件下,单对差分线可达到10 Gbps的传输速率,由于Arria10的Serdes接口包含了8B/10B编解码模块,因此单对差分线的最高有效传输带宽为8 Gbps。当96对差分线同时进行信号传输时,最高有效传输带宽可达768 Gbps,实现了Serdes接口高带宽的传输特性。

表2 3种速率下PMA参数调整表

PMA参数速率8Gbps9Gbps10GbpsVOD313131Pre⁃emphasis默认值默认值默认值VGA默认值77DC增益默认值默认值2Equalization模式高速率模式高速率模式高增益模式DFE未开启未开启自适应

图4为测试码型PRBS31、速率为10 Gbps,且PMA参数经过优化后的数据传输特性结果图,图右侧的Checker选项可观测到测试码个数为1.127 5×1014,误码个数为0。

图4 PBRS31 10 Gbps误码率测试图

4 结束语

基于ALTERA公司推出的Arria10芯片设计了一种新型高性能的高速Serdes接口电路,并对8 Gbps、9 Gbps、10 Gbps信号的传输特性进行了测试分析。该Serdes接口电路性能优良,可以满足传输速率更高、带宽更宽的要求。该板卡设计可实现数字开关矩阵的功能,其VPX通用标准设计在未来可重构系统平台中扮演重要的桥梁角色,为测控、现代无线通信、电子对抗等多个领域信号切换传输与分配提供了技术支撑。

[1] 闫薇.矩阵交换网络设备的设计与研究[D].北京:中国农业大学,2004.

[2] 刘冀川.5 Gbps高速采样系统的设计与实现[J].无线电工程,2014,44(12):22-24.

[3] 韦雪明.高速 SERDES 接口芯片设计关键技术研究[D].成都:电子科技大学.2012.

[4] Lewis D.SerDes Architectures and Applications[C]∥Proceedings of Euro Design Con,Chicago,USA,2004:1-14.

[5] 王张萌.高速Serdes接口的关键电路设计[D].合肥:合肥工业大学,2015.

[6] 陈超文.面向光纤通道的SerDes电路IP化技术研究[D].成都:电子科技大学,2014.

[7] 贾建超,陈涛,李钊.基于TLK2711的高速数据串行传输传输[J].电子技术应用,2013,39(9):47-49.

[8] ALTERA.Arria 10 Device Datasheet[S].ALTERA,2016.

[9] 马友科.基于CPS1848的SRIO总线交换模块设计[J].无线电工程,2014,44(10):73-76.

[10] ALTERA.Arria 10 Device Overview[S].ALTERA,2016.

[11] ALTERA.Arria 10 GX,GT,and SX Device Family Pin Connection Guidelines[S].ALTERA,2016.

[12] ALTERA.Arria 10 Core Fabric and General Purpose I/Os Handbook[S].ALTERA,2016.

[13] 宿元斌.智能温度传感器MAX1619及其应用[J].仪表技术,2007 (8):64-65.

[14] ALTERA.Arria 10 Transceiver PHY User Guide[S].2016.

[15] 杨章平.高速PCB设计中的信号完整性分析[D].成都:电子科技大学,2014.

[16] ALTERA.Quartus II Handbook Volume 3:Verification[S],2016.

杜冰馨(1988—),女,硕士,工程师,主要研究方向:航天测控、阵列信号处理;

吴海洲(1977—),男,博士,高级工程师,主要研究方向:航天测控、阵列信号处理。