基于ZYNQ和AD9361的软件无线电平台设计与实现

2018-12-27

(公安部第一研究所,北京 100048)

1 引言

软件无线电技术最早是美国在海外战争中为解决互联互通互操作提出来的,美国军方提出Speakeasy项目以及JTRS(联合战术无线电系统)计划,标志着软件无线电进入快速发展阶段。该计划是美军为保证不同设备间的互通性,使各军种间实现高效、可靠的协同通信而研制的三军通用软件无线电台。民用移动通信的需求也是软件无线电技术发展进步的巨大驱动力,移动通信经历了从第一代模拟系统到目前第四代商用通信系统开发研制,存在着多标准多模式共存、硬件资源无法共用等问题,用一个全球统一的标准实现无缝隙覆盖通信体系已成为设备制造商、运营商和用户的共识。软件无线电即是利用一个开放式、标准化、模块化的通用硬件平台,通过可编程的软件实现不同的系统功能,诸如通信协议、工作频段、调制方式,提升系统的灵活性,体现出硬件资源的重用性。

当前的无线通信领域典型的软件无线电平台代表有微软的Sora平台和美国国家仪器研制的USRP平台。这两个平台都需要借助PC来实现软件无线电数字信号处理,无法保障数据处理实时性和高强度计算,不利于设备的集成,更多地用于科研仿真类项目。随着无线通信、微电子等领域的不断发展,小型化、高集成度的软件无线电平台成为软件无线电技术落地应用的基石。Xilinx公司研制的ZYNQ可扩展处理平台为All Programmable概念而生,同时具有软件、硬件和I/O的可编程特性。ZYNQ芯片集成了一个基于双核ARM的处理子系统和一个可编程逻辑。ARM与FPGA之间的数据交互使用AXI接口,最高吞吐量达到9.6 Gbit/s,可以满足高速通信需求。

本文将首先提出基于ZYNQ和AD9361的软件无线电平台框架,设计实现AXI总线接口和SPI控制接口,移植嵌入式Linux系统,并完成各类接口驱动开发,利用ZYNQ逻辑资源开发高速通信算法,并通过仿真验证平台的正确性。

2 基于ZYNQ和AD9361的软件无线电平台设计

2.1 基于ZYNQ和AD9361的软件无线电平台框架设计

针对专用无线通信系统低功耗小体积的应用需求,本文提出了如图1所示的软件无线电框架平台。该平台由Xilinx公司推出的全可编程器件ZYNQ和ADI公司的高性能射频收发器AD9361组成。

全可编程器件ZYNQ包含ARM处理器资源和FPGA逻辑资源,双核芯片的设计有利于降低专用无线通信系统的功耗和布板尺寸。ARM处理器资源非常丰富,除了基于ARM CortexA9的双核应用处理器外,还包括片内存储器接口、外部存储器接口、各类I/O外设和连接接口。用户可根据应用需求合理使用ARM处理器资源和逻辑资源来配合完成相应的应用开发。一般来说,在专用的无线通信系统开发中,可利用ARM侧处理器资源开发逻辑控制程序,利用FPGA侧逻辑资源开发数据处理高速算法,例如ADC、DAC、混频、滤波、增益控制等。ARM侧可以单独使用,不依赖于PL(Programmable Logic,可编程逻辑)部分,可以裸机或嵌入式操作系统开发。整个平台是以ARM为核心的处理器平台,PL可以看成是PS(Processor System,处理器系统)的另一个具有可重配置特性的“外设”,作为PS部分的一个从设备,受ARM处理器控制。ZYNQ中ARM与FPGA之间的数据交互通过AXI接口,满足实时和高速通信的需求。

AD9361射频收发器是ADI公司推出的面向3G和4G基站应用的高性能、高集成度射频解决方案,集成了AD/DA、滤波、放大、增益控制、频率合成器等模块,工作频段为70 MHz—6 GHz,工作带宽为200 kHz—56 MHz,可应用于各种通信系统的通信和数据收发等。AD9361通过FMC接口与ZYNQ平台相连,具有无缝FPGA连接能力,通过该集成收发器上预留的SPI接口,即可完成射频收发模块参数配置和状态信息读取。

图1 基于ZYNQ和AD9361的软件无线电平台框架

2.2 AXI总线接口实现

ZYNQ使用AXI总线协议实现ARM与FPGA之间的数据交互,PL部分开发的模块作为一个IP Core挂载在AXI总线上,PS部分需要通过调用相应的驱动实现数据交互。

AXI接口有三种协议类别,分别是AXI4_Lite、AXI4、AXI4_Stream。其中,AXI4_Lite为轻量级协议,适合小批量数据或简单控制场景,主要用于访问一些低速外设和外设的控制;AXI4和AXI4_Lite差不多,只是增加了批量传输功能;AXI4_Stream是一种连续流接口,不需要地址线,使用时必须有一个转换装置,例如AXI_DMA模块来实现内存映射到流式接口的转换,其本质是针对数据流构建的数据通路,从信源到信宿构建起连续的数据流,这个接口适合做高速实时信号处理。

ZYNQ共有9个AXI硬件接口,包括4个AXI_GP通用接口、4个AXI_HP高速接口和1个AXI_ACP加速接口。GP接口是32位的低性能接口,理论带宽为600 MB/s,HP和ACP接口为64位高性能接口,理论带宽为1 200 MB/s。PL部分开发的模块需要严格按照AXI总线协议,作为一个IP Core挂载在AXI总线上,由PS部分调用实现数据交互。针对不同的应用,用户需合理选择AXI_GP、AXI_HP与AXI_ACP接口。

由于无线通信软件无线电平台中基带数据流吞吐量较大,所以采用用于大数据连续流传输的AXI_Stream协议,物理接口采用AXI_HP。如图2所示,在PL端需利用AXI_DMA模块作为转换装置实现内存映射到流式接口的转换,将PS内存单元中的数据流转为Steam流输出。用户在PL部分开发的算法都需要通过AXI_Stream接口挂载到AXI_DAM模块上。PS端通过调用相应的驱动程序,与PL部分的AXI_DMA转换模块实现数据交互。另外,需采用32位的低性能AXI_GP接口作为控制接口,实现逻辑资源部分AXI_DMA模块初始化和相关配置。

图2 AXI硬件接口实现框图

PL端开发时使用XPS(Xilinx Platform Studio,Xilinx公司开发的嵌入式系统开发套件)工具配置AXI_Stream接口,XPS工具为AXI_DMA分配地址,PS开发时可以根据分配的地址通过CPU像访问外设一样访问AXI_DMA模块。PS端开发的驱动将在/dev里对应一个逻辑设备节点,这个节点以文件的形式存在。模块在调用insmod命令时被加载,调用rmmod命令时被卸载。上层应用访问底层AXI接口时,是以open、read、write的形式,无需考虑过多的硬件底层细节。

2.3 AD9361寄存器配置接口实现

AD9361是一款面向3G和4G基站应用的高性能、高集成度的射频捷变收发器,可通过SPI读写寄存器来控制状态机按需工作。AD9361在管脚中预留了SPI接口,来使其具备完全编程特性。PS部分通过SPI接口可以方便地配置AD9361射频收发模块的工作频段、发送接收增益、射频带宽、滤波器等参数。

如图3所示,ZYNQ使用SPI接口对AD9361射频模块进行参数配置,PL侧需要使用Verilog代码开发SPI接口,其逻辑时序需满足AD9361射频收发器要求的SPI接口配置时序,该接口挂载到轻量级AXI_Lite总线上,通过AXI_GP物理接口连接到PS侧。PS侧开发并加载SPI驱动,上层应用调用SPI驱动实现AD9361射频收发器的参数配置。

图3 AD9361寄存器配置接口实现框图

3 基于ZYNQ的嵌入式Linux开发

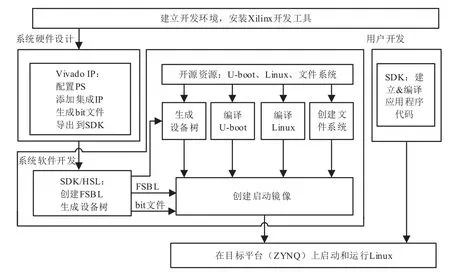

在ZYNQ上移植Linux操作系统相对一般的基于SoC的嵌入式Linux系统移植方法略复杂,如图4所示,基于ZYNQ的嵌入式Linux开发流程分为系统硬件设计、系统软件开发及用户开发三部分。系统硬件设计使用Vivado等软件完成PS部分的硬件配置,并针对特定应用进行PL逻辑开发,添加集成IP Core,最终生成完整的硬件配置bit文件,导出到SDK软件中。系统软件开发部分利用硬件配置bit文件创建SFBL,编译U-boot、Linux内核、设备树和文件系统,最终创建启动镜像。用户开发部分在SDK软件环境中开发特定的软件应用,建立并编译应用程序代码。最终在目标平台ZYNQ上启动和运行Linux系统及用户程序。

图4 基于ZYNQ的嵌入式Linux开发流程

系统开发分为硬件开发和软件开发两部分,硬件部分选择并配置PS部分集成的控制器和外设,根据不同的应用需求,进行自定义PL可编程逻辑开发,并将它们转换或设计成IP核,利用Vivado IP Integrator工具创建整个嵌入式系统的模块化设计,包括开发需要的数据移动工具(AXI_DMA、AXI Memory Master、AXI_FIFO等)以及连接PL与PS的AXI接口(GP、HP和ACP),之后将项目导入到SDK中。软件部分在SDK中可根据硬件配置文件生成FSBL,并开发相应的驱动及应用程序。

系统上电后自动执行片内BootROM中的代码,BootROM会初始化CPU和一些外设,并根据外部启动MIO引脚配置,从外部存储器引导FSBL到内存。FSBL根据硬件配置bit文件初始化PS部分,配置PL逻辑部分,并加载U-boot作为Linux内核的Bootloader程序,初始化CPU及外设,拷贝Linux内核映像到RAM中,再通过设备树文件将硬件相关信息传递给Linux内核,最后由Linux系统加载文件完成启动,根据特定需求运行相关驱动及应用程序。

4 算法库函数API

上述软件无线电平台可用于通信系统研发、无线信号侧向、数据采集处理等,PL部分为用户提供了丰富的通信系统算法库,诸如扰码、卷积、交织、调制、IFFT、上下变频等LTE协议的开发。这些函数由ZYNQ的逻辑部分开发,以FPGA模块的形式提供给客户。利用这些函数可以使客户脱离底层繁琐的硬件及通信物理层设计,有效地缩短新产品开发时间。

5 基于ZYNQ的软件无线电框架平台功能验证

应用ZYNQ和AD9361组成的软件无线电平台可高效实现低功耗小体积的无线信号侧向系统,搭建方案如图5所示。利用ZYNQ ARM侧处理器资源开发逻辑控制程序,并配置AD9361工作模式,利用ZYNQ FPGA侧逻辑资源开发数据处理高速算法,例如信号功率计算、无线信号侧向算法等,利用AD9361完成高性能无线射频信号收发。

图5 基于ZYNQ和AD9361软件无线电的无线信号侧向系统搭建

为验证基于ZYNQ的软件无线电平台及其接口正确性,设计的验证方案如图6所示。使用信号发生器生成433 MHz正弦信号,通过ZYNQ SPI接口配置AD9361,由AD9361下变频后,通过数据接口发送给ZYNQ,PS部分通过DMA接口驱动获取数据,再通过网口发送到MATLAB解析,I路和Q路基带信号的时域图和利萨如图形(Lissajous-Figure)如图7所示。

图6 基于ZYNQ的软件无线电框架平台验证方案

6 结束语

图7 基于ZYNQ的软件无线电框架平台验证方案

本文设计并实现了ZYNQ+AD9361的软件无线电平台,实现了平台底层硬件接口,搭建了完整的高速数据交互通路,移植了Linux嵌入式系统,开发了高速通信算法,最终通过仿真验证了基于ZYNQ的软件无线电平台正确性,可根据用户需求,进行下一步应用开发。