基于FPGA的图像拼接技术研究与实现

2018-12-17徐扬王晓曼朱佶刘鹏姜浩

徐扬,王晓曼,朱佶,刘鹏,姜浩

(1.长春理工大学 电子信息工程学院,长春 130022;2.中国华录·松下电子信息有限公司,大连 116023)

图像拼接技术主要目的在于将多幅有重叠区域的图像拼接成一幅完整的大视场图像,其过程主要为图像配准和图像融合两步,图像配准工作在于找出两幅图像中的重叠区域的坐标关系并将两幅图像拼成一幅图像,图像融合工作主要在于消除图像配准工作拼接图像中由于亮度、对比度等因素引起的拼接缝,最后得出一幅完整的图像。随着技术的发展,目前视频拼接技术发展已经比较成熟,各种视频拼接的技术已经在我们的日常生活中投入使用,如车载监控、智能监管、交通等领域都涉及到大视场成像,会用到视频拼接技术。目前国内有多种软件处理图像拼接,如 videostitch、Kolor autopano、video pro等,这类软件已经具有较高的拼接精度,但是都需要预先拍摄原始图像,再通过软件对图像作拼接处理,达不到实时性的要求,在实际的工程运用中很难适用。在基于硬件的图像拼接系统研究中,图像配准通常由上位机完成算法部分,也难以达到实时性要求。

针对无法满足实时性的问题,本文基于现场可编程门阵列FPGA设计了一套图像拼接系统,采用两个拍摄位置固定的CMOS摄像头同时获取两路图像,并进行亮度调节,FPGA对采集到的图像信息进行图像配准工作,计算出平移量,得出重叠区域,最后采用加权算法消除拼接缝,进行图像融合,由VGA接口输出显示。系统流程如图1所示。

图1 系统流程图

1 系统总体硬件结构

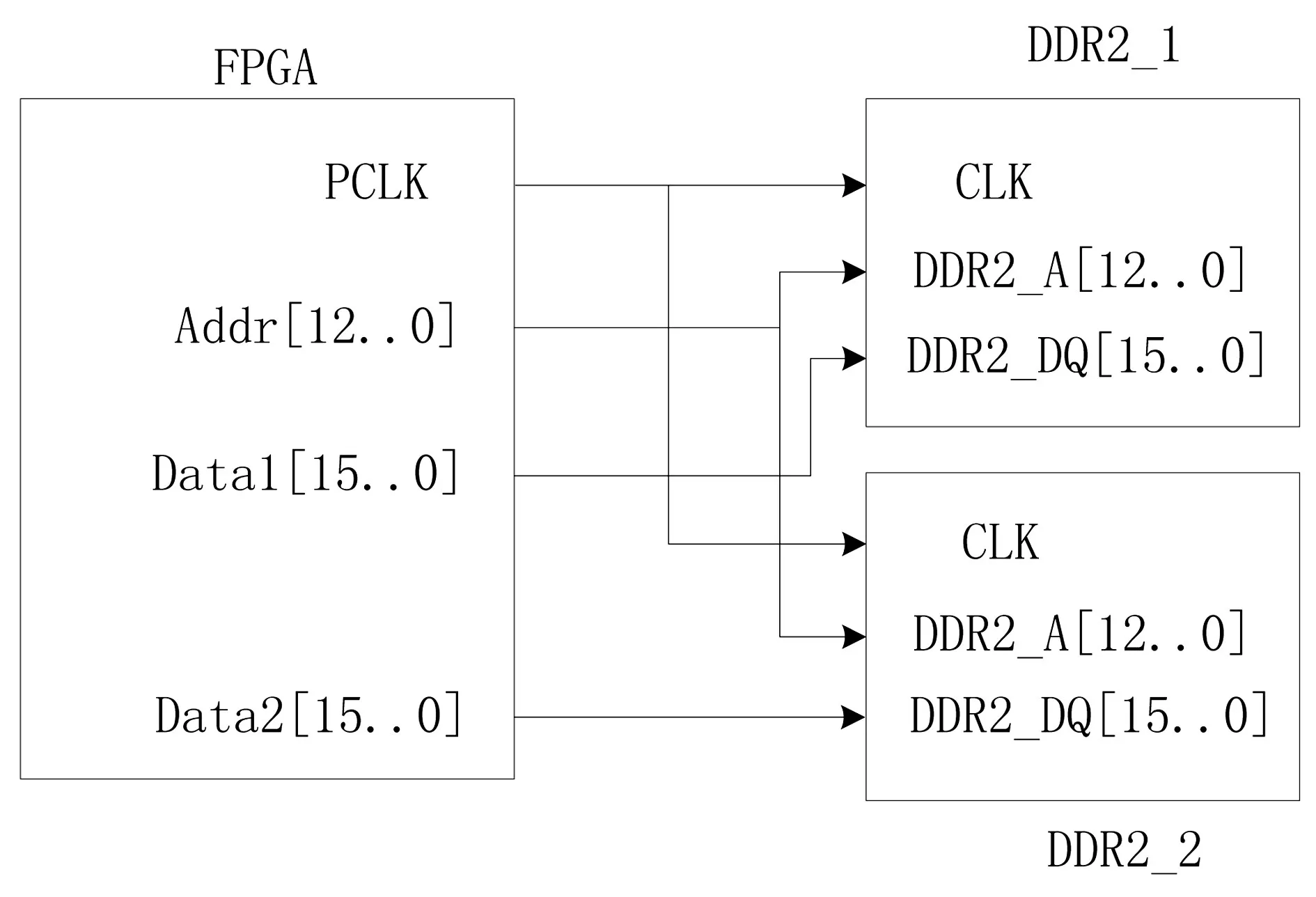

系统总体结构框图如图2所示,以Altera公司的Cyclone IV芯片作为核心芯片,系统整体由电源、JTAG、图像采集、图像缓存、数据处理和显示部分构成。由FPGA对双目摄像头进行配置,获取前端两个CMOS摄像头采集的视频数据,再通过SDRAM控制模块将两路视频数据传输给2片DDR2作缓存,最后根据VGA显示时序读出数据并做图像配准和融合工作后由VGA显示。

图2 系统总体结构框图

2 硬件电路设计

系统的硬件电路主要为图像采集、缓存和输出接口部分。

2.1 图像采集部分

系统采用OV5640双目摄像头采集两路图像,输出RGB格式视频,两个摄像头的信号线相互独立,与FPGA开发板扩展口相连,FPGA通过IIC配置两个摄像头的分辨率,完成IIC配置后接收视频信号。IIC对复位信号和SDA、SCL进行配置,FPGA提供20k时钟信号,在初始化OV5640时对0X5587寄存器修改完成两个摄像头的亮度预处理。控制部分连接图如图3所示。

本系统选取两个摄像头的分辨率为320*240,帧频60fps,像素时钟24M,以RGB565格式输出。FPGA接收的每连续2个8位RGB数据作为一个16位RGB565格式的像素数据进行缓存。FPGA通过接收CMOS_HREF信号采集有效图像数据。VSYNC信号作为缓存读时序的触发信号,时序图如图4所示。

图3 OV5640与FPGA控制部分连接图

图4 CMOS采集时序

2.2 图像数据缓存模块

考虑到数据采集的像素时钟和数据处理的FPGA芯片时钟以及数据输出的VGA时钟三者是不同的,因此需要加缓存模块来将三者隔离,系统采用2片MT47系列的DDR2芯片进行数据缓存,它的容量为1Gbit,16位数据位,两片DDR2容量为2Gbit,32位数据位,带宽高达10Gbit,满足缓存两路分辨率为320*240,帧频60Hz视频数据的要求,FPGA和两片DDR2的端口对应图5所示。两片DDR2芯片分别缓存两路图像数据,每个存储单元存放一个像素16bit图像数据,按照1帧所对应的地址排列,由两组FIFO模块,每组两个FIFO,分别控制两路数据的读写操作,模块图如图6所示。

图5 FPGA与DDR2端口对应图

图6 DDR2缓存模块图

2.3 显示接口部分

本系统显示接口采用VGA接口,将RGB三色模拟信号输出显示,对FPGA输出的16位数字信号转化为模拟信号,采用外接ADV7125数模转换芯片转换。ADV7125芯片具有3通道8位数据口,可将RGB信号转化为3路模拟信号输出,输入RGB565格式信号时将多余数据口接地,时钟和控制消隐信号由FPGA提供,如图7所示。

图7 FPGA与ADV7125连接图

3 系统软件设计

系统的软件设计主要集中在图像拼接部分。其中对图像明暗度的预处理已经通过改变OV5640寄存器完成,图像拼接主要包括图像配准和图像融合两个部分,两个部分的功能由Altera EP4CE6F17C8芯片完成。

3.1 图像配准

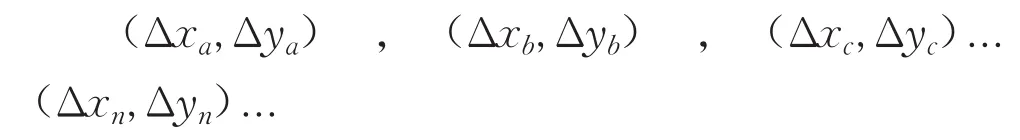

图像配准算法主要分为两种,基于灰度特征的配准和基于变换域的配准,而无论是类似基于灰度特征的harris算法还是基于变换域的FFT法,计算量都十分庞大,故一般基于硬件的图像拼接的图像配准部分都由ARM或者DSP来完成计算,再将偏移量传给FPGA做处理。而考虑到两个摄像头的位置固定,因此视场角相同的情况下两幅图像的偏移量是固定的,故不必用复杂算法计算出两幅图像的偏移量,因此采用相位标校方法对图像配准。先将采集到的两路图像在显示器上显示,设CMOS1图像为P1,CMOS2图像为P2,P1起始坐标为(0,0),P2起始坐标为(320,0),P1和P2有明显的重叠区域,采用标校方法消除重叠区域,具体原理如下:

(1)选取合适背景,取多个定位点a、b、c...将摄像头对准背景采集图像。

(2)测算出 a、b、c...多点在 P1和 P2的位置

并计算出两个参考点在P1和P2上的相对距离

其中

(5)将P2整体在x方向平移Δ,在y方向平移Δ,得到两幅图像的重叠区域分辨率为:

在FPGA中,图像配准工作在VGA_Controller模块中完成,如图8所示。oCoord_X和oCoord_Y为VGA显示时扫描的橫纵坐标,oRequest1和oRequest2分别为两路图像数据的读取信号,模块内部设置常量X_START和Y_START,分别表示行列消隐部分。起始时将两幅图像分别以起始点(0,0)和(320,0)显示在显示屏上,再通过改变有效输出数据消隐X_START和Y_START的大小,逼近背景板上的定位点,直到起始点为定位点为止,即可得出多出消隐部分即为定位点坐标,得出3个定位点的6个坐标后,即可计算得出平均偏移距离和重叠区域大小,根据重叠区域大小将P2与P1拼接起来,得到有拼接缝的拼接图像,再进行下一步图像融合工作。

图8 VGA_Controller模块bsf框图

3.2 图像融合

在得出两幅图像的重叠区域后,开始拼接缝区域作图像融合工作,考虑到算法在硬件系统中的使用的难易程度,采用了计算较方便的线性加权平均法。由于通过相位标校已经得出拼接缝的位置,故不必对全区域作自适应加权,只需在拼接缝附近作加权平均算法,达到消除拼接缝的目的。

由于之前已经做过关于亮度的预处理,因此对于重叠区域作分组加权法,根据相位标校所得图像重叠区域为220列像素,将这220列像素分为10组,每组22列像素,对每一组的像素乘上不同权值进行图像融合处理。将标校后的图像分为A、B、C三个区域,其中A区和C区分别为CMOS1和CMOS2拍摄到的图像区域,B区为重叠区域,将B区划分成10组,从左至又分别为B0,B1,B2,B3,B4......B8,B9设拼接后图像信息为I(x,y),A区图像信息为A(x,y),C区图像信息为C(x,y),σ1为权值,则融合公式如下所示:

其中,对于σ1的取值如表1所示。

表1 σ1取值表

由于FPGA内部计算小数乘法计算量较大,FPGA本身对于2的整数次幂的操作较容易实现,因此将σ1的值用2的负数次幂的形式相加表示,则16位图像数据和权值的小数乘法运算可转化为16位数据左移不同位数并且相加的加法运算,转换公式如下:

因此16位视频数据乘法的计算结果可以转化为Data值分别左移a、b、c...n位之后相加的值。而精确度越高,则加法运算中2的负高位次幂越多,本次数据位为16位,因此n的取值不超过15即可,本次精确度到0.01以后,则各个区域σ1的转化后的值如表2所示。

表2 近似值转化表

在对2幅图像进行融合处理时,将A、B、C三个区域分开处理,当计数器扫描到A、C区域时,直接输出A/C区图像数据,当扫描到B区域时,将两组数据按上述线性加权算法处理后输出,根据oCoord_X大小划分A、B、C区域,最终输出加权平均值Data_average_R、Data_average_G、Data_average_B作为输出值。模块图和仿真图如图9、图10所示。

图9 图像融合模块Data_average bsf框图

图10 加权平均算法仿真图

4 实验结果分析

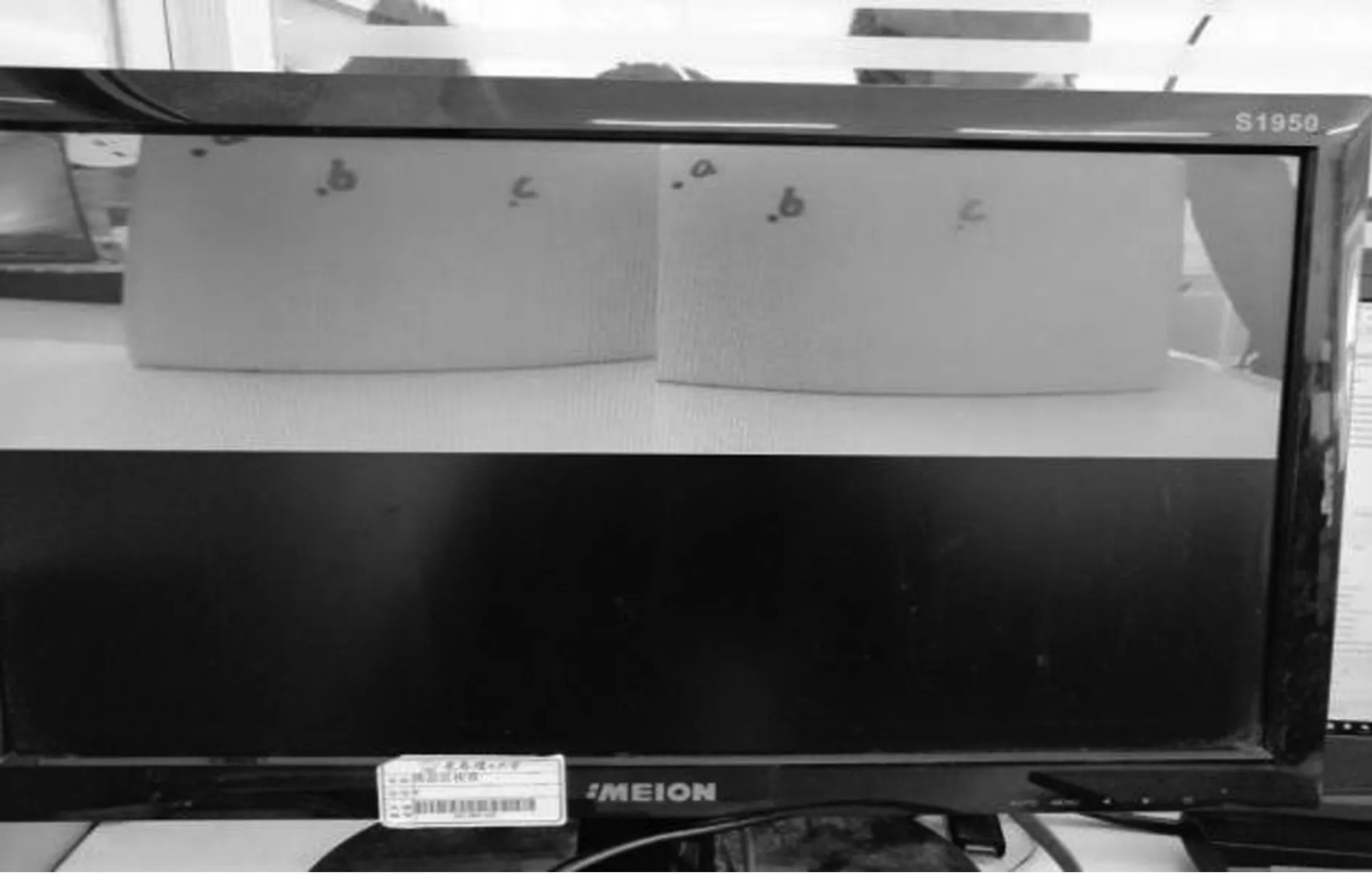

系统使用Altera公司的FPGA开发板,采用OV5640双目摄像头采集图像数据,OV5640通过开发板扩展口与开发板相连,两个摄像头保持一定间距。如图11所示。

图11 图像拼接系统示意图

在对两个摄像头初始化阶段进行两路视频的亮度预处理,基本效果如图12。两幅图像亮度基本趋于一致。

图12 亮度预处理后图像

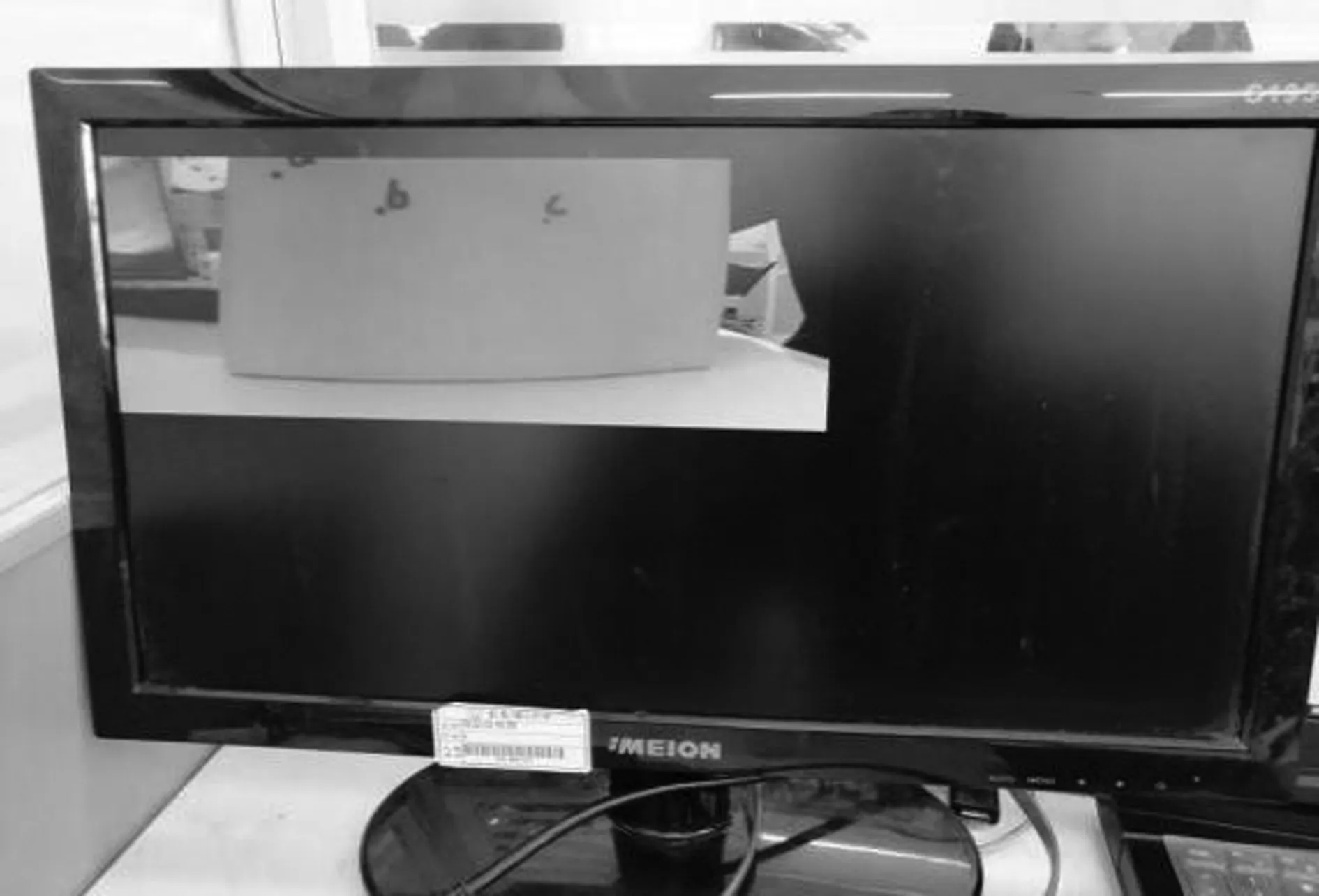

亮度处理后对图像作标校工作,首先选取一个背景板,在上面标定a、b、c三个点,将摄像头对准背景板拍摄图像,如图13所示,经过图像标校后坐标位置如表3所示。

表3 a、b、c三点位置坐标

得出三点位置后根据公式计算出对应的偏移量,X方向为222,Y方向为15,得出实际重叠区域大小为220*225,由于受到实际固定角度的影响,两个摄像头拍出图像在水平方向上有所偏移,去除上边界后得出实际分辨率为406*192,再根据重叠区域大小将两幅图像作拼接并做加权算法,对两副图像重叠区域作加权,在2个时钟后输出新的像素值,由于图像配准得出两个摄像头重叠区域后不必再次计算偏差量,因此拼接过程中加权算法速率直接影响图像拼接后的帧频,两幅图像初始帧频为60帧/s,经加权处理后最终拼接图像处理一帧时间为18.7ms,帧频为53帧/s,满足实时性要求。最终得到图像拼接完成图,如图14所示。

图13 初始2路图像对比图

图14 图像拼接处理完成图

经过图像融合处理后图像的视场有所扩展,且无明显的拼接痕迹,帧频无明显下降,达到了预期的效果。

5 结论

本文基于FPGA实验平台,通过外接双目摄像头,完成了图像采集、缓存、处理的双摄像头图像拼接系统。系统中缓存模块有效解决了图像采集、数据传输之间的时钟同步问题,图像拼接部分利用两路摄像头拍摄位置固定这一点进行寄存器调整亮度和相位标校调整重叠位置,不采用软件算法的手段对图像的位置和亮度进行调整,完成图像亮度预处理和图像配准的过程,确保了实时性,且保证有较高的精确度,在此基础上对拼接图像重叠区域分组作加权平均处理,在处理时将小数相乘运算转化为2的幂次运算,保证较高精确度的同时大大减少了计算量,使图像渐变平滑,消除拼接缝,完成效果较好,达到了预期的目标。对于硬件拼接图像有一定应用价值。