一种模数转换电路的关键设计技术研究

2018-11-21谢亚伟居水荣孟亚华王珍李欢

谢亚伟 居水荣 孟亚华 王珍 李欢

摘 要:采用每级为1.5位精度的7级流水线结构也即7级子ADC设计了一个8位80MS/s的低功耗模数转换电路。重点考虑了该ADC中的采样保持电路和每一级子ADC中的动态比较器的结构设计,以提升整个ADC的性能、降低整个ADC的芯片面积和功耗。采用0.18μm CMOS工艺完成加工后,测得该ADC在输入信号为36.25MHz,采样速率为80MHz下的信噪比(SNR)为49.6dB,有效位数(ENOB)为7.98位,典型的功耗电流只有18mA,整个ADC的芯片面积为0.5mm2。

关键词:流水线型ADC;采样保持电路;动态比较器;数字校准和输出寄存;低功耗;信噪比

中图分类号:TN79+2 文献标志码:A 文章编号:2095-2945(2018)28-0036-04

Abstract: A low-power Analog-to-Digital Converter (ADC) with 8-bit 80MS/s is designed using a 7-stage pipeline structure with 1.5bit precision in each stage, i.e., 7-stage sub ADC. In order to improve the performance of the whole ADC and reduce the chip area and power consumption of the whole ADC, the sample-and-hold circuit of the ADC and the structure design of the dynamic comparator in each stage of the ADC are mainly considered. The ADC is fabricated by 0.18 μm CMOS process, and the signal-to-noise ratio (SNR) of the ADC is 36.25 MHz; when the sampling rate is 80MHz, the signal-to-noise ratio (SNR) is 49.6 dB, the effective number of bits (ENOB) is 7.98 bits, the typical power consumption current is only 18 mA, and the chip area of the whole ADC is 0.5 mm2.

Keywords: pipelined ADCC; sample-and-hold circuit; dynamic comparator; digital calibration and output register; low power consumption; signal-to-noise ratio

1 概述

在圖像视频处理和无线通讯等应用领域中,流水线型构架的高速低功耗模拟数字转换器(ADC:Analog to Digital Converter)被广泛应用, 如何进一步降低这类ADC的功耗、提高其性噪比和精度、缩小其芯片面积等是目前针对这类ADC的主要方向[1~2]。

本文介绍了一种基于0.18μm工艺的8位、采样速率为80MHz的流水线型ADC设计中的关键技术。首先采用一种基于CMOS互补开关及仅使用一个电容的栅压自举开关的全差分过底极板采样保持电路,减小了开关的导通电阻和信号的非线性失真,并且有效地抑制了电荷注入效应时钟馈通及偶次谐波失真,整体功耗和面积都较小。其次选择优化的电路结构设计每一级子ADC中的动态比较电路,降低整个ADC的功耗和芯片面积;最后设计精简且高效的数字校准和输出寄存模块用来消除流水线型ADC实现过程中各种因素对整个ADC性能指标的影响,提高ADC的精度和信噪比,降低ADC的功耗和面积,使得该ADC特别适合作为IP被应用在系统级芯片中,进而可以广泛应用于仪器仪表、超声系统、高分辨率图像处理和高清晰度电视等场合。

2 8位Pipelined-ADC整体设计思想及其关键设计技术

图1是本文8位高速低功耗流水线型ADC的结构框图。

作者针对流水线型ADC已经开放过第一代产品,与上一代ADC产品相比,图1所示的ADC作了几个方面的优化设计,出发点是基于高速低功耗流水线性ADC设计中的以下几项关键技术:

首先,采样保持电路是流水线型ADC的第一级,其性能直接制约了ADC整体性能的提高。在作者所研发的上一代产品中,省略了图1中的专用采样保持电路,只是利用每一级子ADC中的钟控开关和电路来实现采样保持功能;这样做看起来是省略了一些电路结构,但实际上增加了整体设计的难度;另外关于采样电容没有进行精确的设计,也没有专门采用栅压自举开关。从实际测试结果看,尽管某些时刻信噪比和ENOB较高,但很不稳定,功耗指标也一般。

其次,以上每一级子ADC中的快闪ADC用来对前一级处理输出的模拟信号通过其中的比较器量化成数字位,该比较器的设计将直接影响整个ADC的性能,包括功耗和芯片面积等。在上一代产品中采用了电容比例比较器,这种比较器包含锁存器和一些耦合电容,通过调整电容间的比例来调节比较器的阈值电压,其缺点是面积较大,功耗也相对较大,另外电容的匹配对比较器的性能也会有影响。

因此本文将围绕以上两点关键技术对上一代ADC产品进行优化设计,以提升该ADC各项性能。

3 采样保持电路的设计

采样保持电路是流水线型ADC的第一级,直接对输入模拟信号进行采样,因而性能良好的采样保持电路直接决定了整个流水线型ADC的精度。采样保持电路在等时间间隔对模拟信号进行采样,并将采样得到信号保持供后级电路量化,从而实现流水线处理输入信号的模式。下面具体介绍本文中增加的专用采样保持电路的设计。

3.1 采样保持电路整体结构

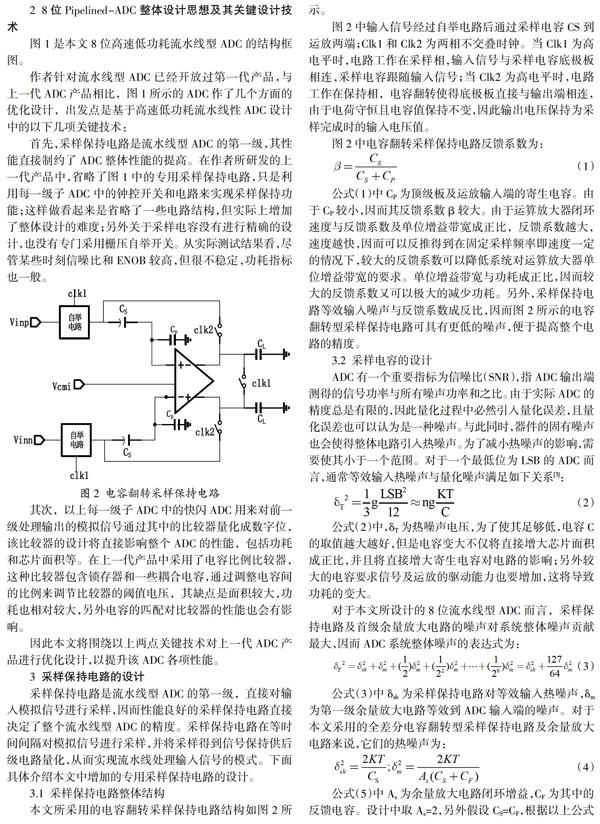

本文所采用的电容翻转采样保持电路结构如图2所示。

图2中输入信号经过自举电路后通过采样电容CS到运放两端;Clk1和Clk2为两相不交叠时钟。当Clk1为高电平时,电路工作在采样相,输入信号与采样电容底极板相连,采样电容跟随输入信号;当Clk2为高电平时,电路工作在保持相,电容翻转使得底极板直接与输出端相连,由于电荷守恒且电容值保持不变,因此输出电压保持为采样完成时的输入电压值。

公式(1)中CP为顶级板及运放输入端的寄生电容。由于CP较小,因而其反馈系数β较大。由于运算放大器闭环速度与反馈系数及单位增益带宽成正比,反馈系数越大,速度越快,因而可以反推得到在固定采样频率即速度一定的情况下,较大的反馈系数可以降低系统对运算放大器单位增益带宽的要求。单位增益带宽与功耗成正比,因而较大的反馈系数又可以极大的减少功耗。另外,采样保持电路等效输入噪声与反馈系数成反比,因而图2所示的电容翻转型采样保持电路可具有更低的噪声,便于提高整个电路的精度。

3.2 采样电容的设计

3.3 自举电路的设计

公式(5)中Vg为电源电压,Vthn为MOS管閾值电压,其导通电阻与输入电压Vin相关,采样电容将不能线性跟踪输入信号,因而将引起谐波失真。栅压自举采样开关原理为:通过选择合适电路结构使式中Vg-Vin在采样相恒保持不变,则其导通电阻可以与输入信号无关,从而减少了采样保持电路的非线性失真。

栅压自举采样开关结构如图3所示。

跟其他同类自举电路相比,本文中的自举电路只使用一个电容就可以实现栅压自举开关功能。当clk为高电平时,该栅压自举开关充分利用节点d的低电平使得M3导通,电源电压VDD没有任何损耗地加在C1上极板,下级板跟随地。节点a在采样阶段超过VDD,为了保证M3衬底始终反偏,应该接在最高电平上,方法是通过M1、M2两个管子实现。在保持阶段clk为低电平,M1打开,M3的衬底通过M1接到VDD,而采样阶段clk为高电平,M2打开使得M3衬底与节点a相连,如此保证了M3衬底始终反偏。

采用以上精简的自举电路对改善整个ADC的功耗和芯片面积指标有明显的作用。

4 每一级子ADC中动态比较器的设计

本文流水线型ADC的每一级子ADC中快闪ADC的功能是将前一级处理输出的模拟信号量化成数字位,实现这部分功能的是其中的动态比较器,因此动态比较器是每一级子ADC设计中最关键的部分。

比较器功耗的降低对整个ADC系统的低功耗设计有重要意义,因此本文采用结构简单的动态比较器来实现芯片面积减小和功耗优化。

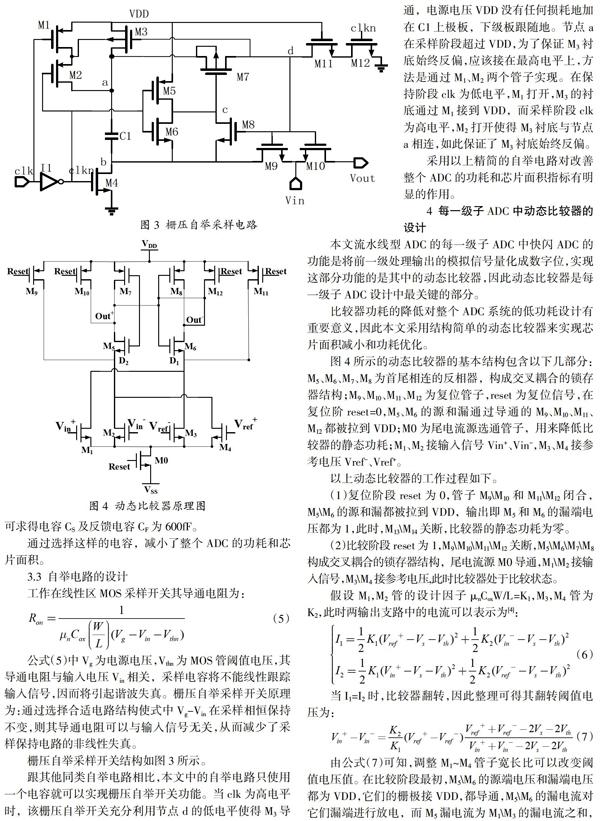

图4所示的动态比较器的基本结构包含以下几部分:M5、M6、M7、M8为首尾相连的反相器,构成交叉耦合的锁存器结构;M9、M10、M11、M12为复位管子,reset为复位信号,在复位阶reset=0,M5、M6的源和漏通过导通的M9、M10、M11、M12都被拉到VDD;M0为尾电流源选通管子,用来降低比较器的静态功耗;M1、M2接输入信号Vin+、Vin-,M3、M4接参考电压Vref-、Vref+。

以上动态比较器的工作过程如下。

(1)复位阶段reset为0,管子M9\M10和M11\M12闭合,M5\M6的源和漏都被拉到VDD,输出即M5和M6的漏端电压都为1,此时,M13\M14关断,比较器的静态功耗为零。

(2)比较阶段reset为1,M9\M10\M11\M12关断,M5\M6\M7\M8构成交叉耦合的锁存器结构,尾电流源M0导通,M1\M2接输入信号,M3\M4接参考电压,此时比较器处于比较状态。

由公式(7)可知,调整M1~M4管子宽长比可以改变阈值电压值。在比较阶段最初,M5\M6的源端电压和漏端电压都为VDD,它们的栅极接VDD,都导通,M5\M6的漏电流对它们漏端进行放电,而M5漏电流为M1\M3的漏电流之和,M6漏电流为M2\M4的漏电流之和,输入电压以及参考电压决定M1\M2\M3\M4各自的电流。假如M5\M6漏电流不同,则M5\M6的漏端放电速度也不同,由于锁存器M5\M6\M7\M8的增强作用,最终导致放电速度快的管子漏端电压为0,而放电速度慢的管子漏端电压为1。

对图4所示的动态比较器进行功能仿真,结果如图5所示。

5 ADC设计和实测结果

5.1 整体仿真结果及版图

以上ADC基于0.18μm工艺平台设计。对整个Pipeline ADC进行整体的瞬态仿真,仿真条件:电源AVDD=1.8V,采样频率Fs=80MHz,采样点数N=64,共模电压Vcm=900mV,正参考电压Vrefp=1.275V,负参考电压Vrefn=0.525V。输入信号频率Fin=36.25Mhz,振幅A=1.5V。在完成瞬态仿真后,再将理想DAC输出进行快速傅里叶变换,结果如图6所示。通过MATLAB软件处理数据计算得到,在输入信号频率为Fs=36.25Mhz时,信噪比SNR为49.9dB,有效位数ENOB接近8bits。

5.2 实际测试结果

以上ADC经过加工后实际测试的结果为:功耗电流18mA;在80MHz采样率,36.25MHz输入信号下,信噪比SNR可达到49.6dB,有效位数也可以稳定在7.98bits左右。这些指标的测试过程和结果都非常稳定。

6 结束语

本文介绍了一种8位、基于0.18μm工艺平台、采样率为80MHz的高速流水线性ADC的优化设计。在优化设计过程中,通过设计新颖的采样保持电路、合理选择电容和采用栅压自举开关,并选择合适的动态比较器电路结构,使得该ADC具有较小的功耗和芯片面积,从而使得本文中的ADC更加适合作为SOC中的IP使用。

参考文献:

[1]颜哲.14位流水线ADC中的关键电路设计[D].合肥:合肥工业大学,2010.

[2]栗成智.12/14bit高速流水线型A/D转换器的研究[D].杭州:浙江大学,2010.

[3]Piatak, Ivan, Morozov, Dmitry, Hauer, Johann. An inverter-based 6-bit pipelined ADC with low power consumption[C]. In: 2013 IEEE EUROCON. Zagreb, Croatia: IEEE Press, 2013: 1951-1954.

[4]Qin Li, Li Cai, Gang Wu. Digitlal-analog and analog-digital converters based on single-electron and MOS transistors[C]. IEEE Control and Automation, Xiamen, China, 2010:1562-1566.