基于FPGA多通道数据采集系统的设计

2018-11-08王增刚常蕾

王增刚,常蕾

(山西华澳商贸职业学院,山西晋中,030600)

0 引言

随着军事、工业、农业的不断发展,各种被检测的数据对象越来越多,并且对系统采集数据的精度与速度都提出了更高的要求,尤其对多路信号的采集系统的设计。传统的多通道模拟量数据采集存储的控制核心一般采用单片机、DSP,在分析和比较传统的数据采集模型后,系统采用FPGA作为核心控制器件[1]。

1 技术要求

同时对幅度0V~5V的32路模拟量信号进行采集、编帧和存储,采样字长16位,单通道采样率不超过25KHz存储容量不小于1Gbyte。

2 系统总体方案

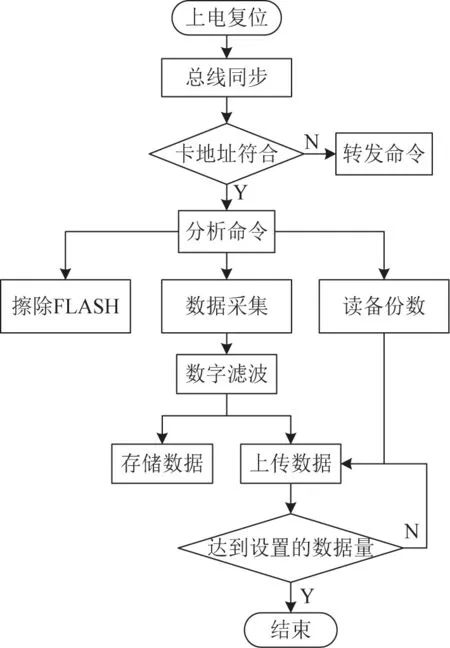

图1 系统结构图

系统实现方案如下图1所示, 32路输入模拟信号,16路为一组,输出的信号进过调理输入给AD7667,FPGA处理AD7667输出的数据,并将采集得到的数据存储至flash,同时也将数据上传至上位机实时监测。

3 系统电路设计

3.1 驱动与信号调理电路设计

信号调理电路如图2所示,为了使整个电路与外界隔离,本设计中使用了信号电压跟随器[2]。本系统被采集信号的幅值是0~5V, AD7667输入范围是0~2.5V,设计用了一对10kΩ的高精密电阻对输入模拟信号进行分压。

图2 AD7667驱动电路

AD7667的驱动放大器需满足以下条件:

(1)运放输出稳定数据采集所需时间必须小于AD7667的采样时间,保证转换精确。

(2)选用低噪声的运放,保证AD7667的信噪比。

信噪比降低程度公式:

式中, N为运放的噪声增益,本系统 N为1;eN为运放的等效电压噪声,f-3dB为滤波器的截止频率;

电路设计使用的AD8021的运放,具有110V/μs的压摆率,噪声为2.0nV/,当对其输入1V的阶跃信号时,输出稳定所需的时间为22ns,完全满足本设计稳定时间要求。

信号在输入AD7667前,设计了一个RC电路,目的是消除短时脉冲干扰,经过分析计算,为了确保采样阶段结束时采样电容充电至所需精度范围内,最终R取15Ω,C取2.7nF。

3.2 FPGA内部FIFO程序设计

在本设计中,传输的信号有AD7667的输出数据、flash与DS92LV18的控制时钟,为此本设计使用FPGA内部的双口RAM,并组成两个异步FIFO。内部FIFO任何时候不能被写满,否则数据将无法存储。32路的信号采样率都是50kHz的模拟信号,字长均为16bit,在软件编程中我们把采集得到数据再加上两字节的帧标志,所以系统传输FPGA内部为:(32×2+2)×25k=1.6MB, 由此可以计算出所以传输给双口RAM数据量为:1.6M/s × 200μs=330B ,由于本设计两个异步FIFO宽度为8b,深度为2048b,软件编程时间远大与数据存储时间。经过实际测试,设计的两个异步FIFO完全能够存储AD7667采集输出的数据。

4 软件设计

系统编程软件使用的Xilinx ISE7.1,程序流程图如图3,主要包括数据采集控制模块、、flash读写控制模块、下发命令识别与数据上传模块。

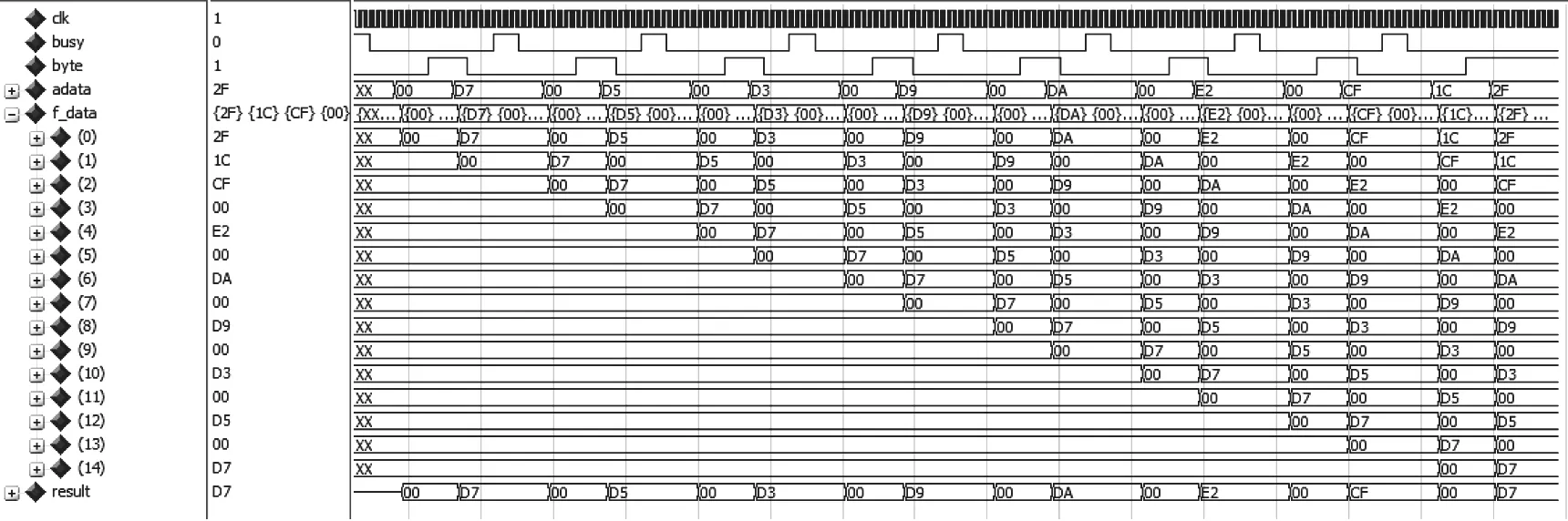

本系统使用了一种称为中值数绝对偏差发的滤波算法,具体流程就是采用一个移动窗口X0(G),X1(G),……,XN-1(G),利用前N个数据来确定下一个传输个数据的有效性。具体算法[3]为:

(1)先计算窗口序列X0(G),X1(G),……,XN-1(G)的中值K;

(2)计算序列|X0-K|,|X1(k)-K|,……,|Xm-1(k)-K|的中值d,令W=1.4826*d;

(3)令q=|XN(k)-K|,如果q 本设计N取7,A取3,其中窗口宽度N和门限L主要调整信号的特效,经过计算系统设计可采用A*W近似取4*d,算出的结果为实型,使用A*W的值可以起到门限作用,对信号进行调整,本设计由于AD7667转换后的数据份高、低两个8位,分两次进行传输,所以要分别对高、低8位使用本滤波软件算法,对该滤波算法使用Modelsim软件进行仿真,结果如下图所示。 图3 程序流程图 上位机软件是在LabWindows/CVI软件环境下编写的,该软件能为熟悉C语言的开发设计人员编写检测系统、自动测试环境、数据采集系统、过程监控系统等应用软件的开发提供了一个理想的开发环境。测试时用的是一个峰值为4V,频率为1kHz的余弦波,上位机软件对接收到的数字信号生成波形生成的波形如图5。 从上图可以看出,数据经过系统软件形成的波形,生成的波形频率恒定,幅值准确,能很好的还原了测试信号。 图4 滤波算法仿真结果 本系统具有同时对32路模拟信号存储与上传至上位机的功能,信号采集、存储的数据量可通过上位机软件进行设置。测试结果表明,系统采集的数据没有丢帧、误帧,系统能正常工作,满足技术要求。 图5 采集数据生成的波形

5 测试结果

6 结束语