用逻辑简化单片机上的复杂功能

2018-10-30ManuVenkategowda

Manu Venkategowda

摘要:解释了可配置逻辑单元如何简化单片机上复杂功能的实现。

關键词:MCU;可配置;逻辑;PLD

D01:

10.3969/j.issn.1005-5517.2018.8.019

有时,简单的东西也大有益处。大多数嵌入式工程师需要通过各种信号或逻辑来满足最终应用需求。他们依靠设计复杂的电路板逻辑来满足这些需求。但是如果通过一种简单的方法便可以做一些复杂的事情会怎么样呢?一些单片机具有灵活的外设,可以执行复杂应用所需的功能。

这就是可配置逻辑单元(CLC)的用武之地。CLC外设已添加到Microchip PlC@单片机(MCU)的外设集中,允许用户设计一个可与MCU连接的简单功能。该CLC外设允许用户指定信号组合作为逻辑功能的输入,并支持使用逻辑输出控制其他外设和IO引脚,可帮助用户灵活设计所选功能。

为了简单起见,Microchip的MPLAB@代码配置器(MCC)支持CLC。因此,设计人员只需拖放逻辑门便可连接输入和输出(GUI格式),并且通过单击按钮便可生成C代码,从而大大简化了CLC模块的实现。

独立于内核的外设( CIP)在处理任务时无需额外的代码或CPU监管来维持运行。CLC是这样一种CIP:它简化了复杂控制系统的实现,同时为开发人员提供了充足的设计灵活性,可通过卸载CPU负荷提高单片机的性能。继续阅读以了解CLC如何用于在应用中实现信号相位检测、互补波形生成或多参数监控。凭借各种输入、触发和输出,CLC具有无限的可能性。

1 概述

CLC是用户可配置的外设,类似于可编程逻辑器件(PLD),但集成在单片机中。可以选择内部和外部输入作为CLC的输入。CLC接收来自其他外设或输入引脚的输入。之后,它会执行预期的逻辑操作,并提供可用于控制其他外设或其他lO引脚的输出。

CLC可以接收信号,例如内部时钟信号、其他外设的输出以及定时器输入等外设事件。可以通过信号门控级将所选择的输入信号指向所需的逻辑功能。

CLC支持各种逻辑功能,如AND、OR、NOT、XOR、NAND、NOR和XNOR。在CLC中,数据门控级的输出是逻辑功能选择级的输入。输出极性级是CLC的最后一级,可以选择所需的极性。

CLC可用作独立外设来实现顺序和组合逻辑功能,从而促进快速事件触发和响应。它还可以与其他外设一起使用,通过促进硬件中复杂功能的自定义实现来帮助扩展外设功能。

作为独立于内核的外设,CLC通过将许多简单的逻辑事件响应从CPU卸载到外设,有效地降低了应用的CPU带宽需求。它还降低了闪存和RAM要求,因为不需要软件算法。

与软件中实现的逻辑功能相比,硬件中实现的逻辑功能具有更快的事件响应。此外,CLC无需任何外部组件即可支持更高级别的集成,从而减小了整体PCB尺寸。

2 相位检测器

CLC的多功能特性和简便性扩展了PIC@ MCU的设计能力。证明CLC能力的一个很好的例子是相位检测器。相位检测器可用于许多应用,包括距离测量。它的工作原理是,当连续的RF波向目标发射时,到目标的距离与发射波和接收波之间的相移成比例。CLC可用于测量相同频率的两个信号之间的相位差。发射和接收的波用作CLC的输入,并且CLC输出处的两个信号之间的相位差可用于计算源和目标之间的距离。

在使用CLC的相位检测器实现中,CLC中的AND-OR逻辑功能可用于实现XOR功能以测量相位差的大小,D型触发器(D-FF)逻辑功能有助于获得信号的超前和滞后信息。除了方波之外,还可以测量其他类型模拟信号(例如正弦波)之间的相位。图1描绘了使用CLC的相位检测器的配置。

将相位差待测的源信号作为输入馈送到两个比较器,这两个比较器被配置为过零检测器(ZCD)。ZCD将输入模拟信号转换为相同频率的方波。如果源信号是方波,则不需要ZCD。方波作为输入从内部连接到多个CLC模块。

CLC1和输入捕捉(IC)外设用于确定相位差的大小。CLC1配置为AND-OR逻辑功能,从中可得到XOR功能。CLC1的经XOR操作的输出作为源信号从外部连接到IC。凭借经XOR操作的输出的脉冲宽度,可得出两个波之间的相位差的大小,该脉冲宽度由IC测量。如果CLC1输出不产生信号,则源信号同相。

为了确定两个输入波形的相位超前和滞后信息,CLC配置为D-FF模式,其中一个方波使用D输入,另一个用作时钟。CLC2的高电平或低电平输出用于确定D输入的相位超前还是滞后于时钟输入。测量相同频率的两个信号之间的相位角在许多应用中都十分有用,包括计量、数字电源系统、通信和医疗仪器。

3 互补波形发生器

使用CLC的另一种方法是在互补波形发生器( CWG)中。CWG从其输入源产生带有死区控制的互补波形。在两个信号之间插入死区时间,以防止各种电源应用中的直通电流。

该应用说明了如何使用CLC外设的边沿检测和中断功能,以单个捕捉/比较/PWM (SCCP)模块作为输入源生成互补波形。

通常,电机控制等应用需要多个互补波形发生器来控制其功能。多重捕捉/比较/PWM (MCCP)模块可通过控制其输出端的死区来产生具有非重叠信号的互补波形。但是,如果应用需要的MCCP实例多于器件中可用的实例,则可以将SCCP与CLC结合使用。

具有SCCP的CLC外设可用于生成具有所需死区的互补波形,因为SCCP本身不能生成非重叠信号。

可以为边沿对齐和中心对齐的SCCP输出添加死区。图2所示为在边沿对齐模式下控制SCCP输出死区的CLC1、CLC2和CLC3配置。

例如,可以通过输出产生互补波形的MCCP外设来驱动全桥电机驱动器电路。然而,如果要驱动多个这样的全桥电机驱动器电路,并且器件上可用的MCCP外设的数量不足,则可以将SCCP与CLC结合使用。

4 多参数监控

通常,应用需要同时监控不同的参数,例如温度、压力和湿度。如果这些参数开始越过上限或下限阈值,则可以采取必要的措施来避免灾难性后果。

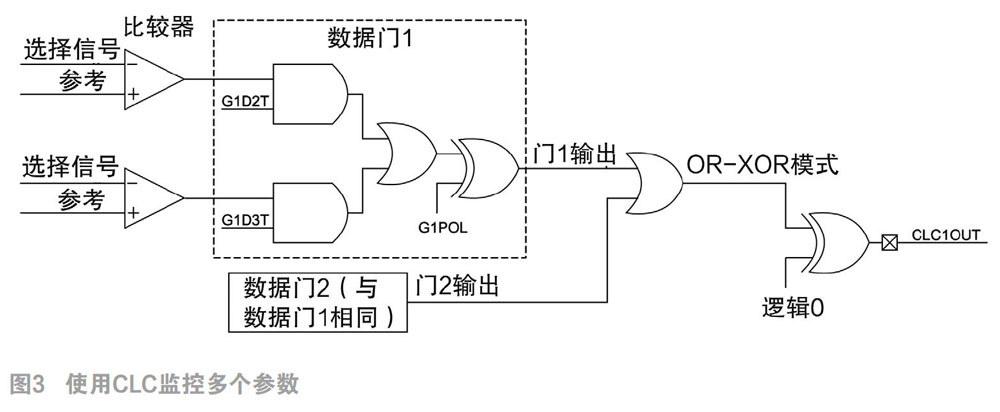

多个比较器可用作CLC的源输入。在单片机中,比较器可用于仅监控一个参数。可以使用CLC组合多个比较器的输出,以监控多个参数。

当监控的任何或所有参数超过一定限值时,可以采取必要的措施。图3所示为用于监控两个不同参数的CLC配置。

在实践中,该应用用于监控工业设备中的温度和压力,以便在任一参数超过预设阈值时关闭设备。它还可用于监控离线不间断电源中的电压大小。

5 结论

通过在外设集中添加可配置逻辑单元,用户可以在PIC单片机中集成简单的板载逻辑设计。组合不同外设的输出增强了现有外设的功能,从而扩展了外设可以实现的应用的范围。

由于与软件中实现的逻辑功能相比,硬件中实现的逻辑功能具有更快的事件响应,因此CLC有助于提高整个系统的速度。它还可提供更高级别的集成,而无需外部逻辑门来实现逻辑功能,从而减少了所需部件的数量并缩小了PCB的整体尺寸。CLC还有助于使用不同的逻辑门组合各种输入源信号以产生完全不同的信号。 所有这些灵活的输入和输出以及逻辑功能都可以通过基于GUI的工具轻松实现,该工具称为MPLAB代码配置器(MCC),可为您的应用生成易读的C代码。

参考文献:

[1]Venkategowda M使用CLC扩展PIC MCU功能的应用笔记[R/OL].http://wwl.microchip.com/downloads/en/AppNotes/00002133a.pdf