基于ZYNQ的高速数据中心接口单元设计*

2018-10-22吕俊杰

吕俊杰,武 杰

(1.中国科学技术大学 近代物理系,安徽 合肥 230026; 2.中国科学技术大学 核探测技术与核电子学国家重点实验室,安徽 合肥 230026)

0 引言

大规模数据采集系统中数据中心是数据汇集的重要节点,由于需要进行大量的数据存储和分析工作,一般使用高性能计算机作为数据中心[1]。

基于硬件的可靠传输协议HRDTP(Hardware Reliable Data Transmission Protocol)由FPGA(Field Programmable GateArray)实现,在数据采集系统中广泛应用[2-3],该协议包括ACK(Acknowledgement)回应与超时重发机制,命令、回应、确认机制等,具有针对性强、结构简单、适应底层硬件等特点,相比传统的通信协议更适用于数据采集系统,效率更高。基于硬件的可靠传输协议与计算机通用的可靠数据传输协议(TCP/IP协议等)无法直接通信。在数据采集系统中数据节点间通信使用基于硬件的可靠传输协议时,为了使数据中心和数据节点通信,需要一特定外设,即数据中心接口单元。

数据中心接口单元像是一块外置网卡,实现了基于硬件的可靠传输协议到标准的TCP/IP协议的通信。目前常见的数据中心接口实现方法有:(1)基于PCI-E接口的插卡式设计[3],使用该设计数据中心必须选用台式机,便携性很差,在很多数据采集的实际环境中无法使用;(2)应用在LHAASO WCDA中,基于FPGA嵌入式系统的设计,该数据接口缺乏对短数据帧合并打包的处理,经测试达到237 Mb/s的数据率[4]。本文基于FPGA和ARM处理器,设计了一种数据中心接口单元。该接口单元相比第一种设计在便携性和通用性上有了极大的提升,因为其使用标准的千兆以太网接口,可以配合各种计算机(包括笔记本电脑)使用,且体积小便于携带,功耗低便于供电;相比第二种设计,由于增加了数据帧合并打包功能,数据率达到了330 Mb/s,有39%的提升。

1 设计与实现

数据中心接口单元作为连接上层管理软件和下层数据传输系统的中间桥梁,需要考虑与数据节点接口和上方与数据中心接口两方面的接口选择。数据中心一般距离数据节点较远,同时需要满足百兆量级的数据率要求,所以数据中心接口单元与数据节点的高速链路选择千兆以太网。数据中心通常选用高性能的计算机,结合数据率的要求,数据中心接口单元与数据中心的通信接口也为千兆以太网。

Xilinx ZYNQ-7000系列全可编程SoC(System on Chip)系列芯片的硬件部分包括一个主频高达667 MHz的双核ARM Cortex-A9处理器子系统PS(Processing System)和一个丰富的内存、配置和互联接口,在FPGA逻辑部分PL(Progarmmable Logic)保留其他传统FPGA所具备的优势。FPGA通过多口高性能接口接到PS端,实现了PL与PS间的高带宽通信[5]。

1.1 数据中心接口单元硬件设计

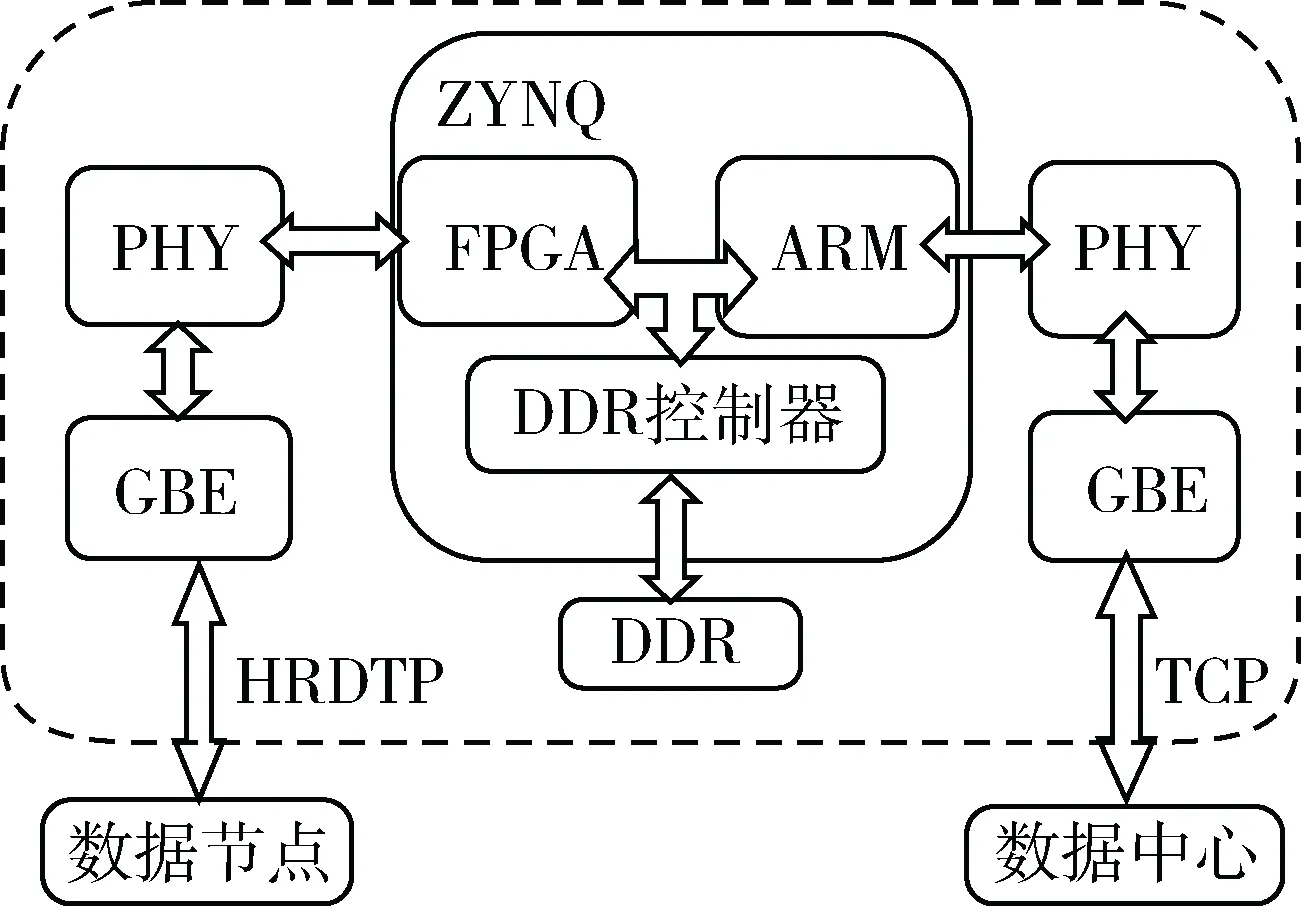

数据中心接口单元的PL端拓展了一块千兆以太网PHY(Physical Layer)芯片,以实现与数据节点之间的数据传输,数据的可靠性通过HRDTP来保证。数据中心接口单元与数据中心之间的通信通过千兆以太网[6]实现,数据的可靠性通过TCP/IP协议来保证。数据中心接口单元的结构如图1所示。

图1 数据中心接口单元结构

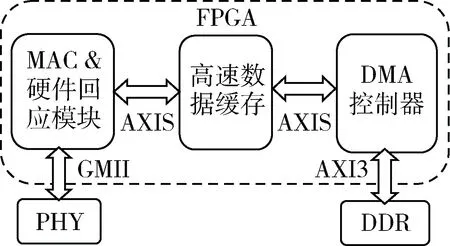

系统的FPGA固件包含了MAC控制器及硬件回应模块、数据高速缓冲模块及DMA控制器,其结构如图2所示。

图2 数据中心接口单元FPGA结构

MAC控制器负责与千兆以太网PHY间的通信;硬件回应模块按照基于硬件的可靠协议完成了对帧类型的分拣、错误帧的处理、数据帧的排序及回应ACK;数据高速缓冲模块为DMA控制器提供数据缓冲,并将n个短数据帧合并成长数据帧;DMA控制器负责DMA数据传输,可以有两种模式选择,由驱动进行配置和启动。

1.2 数据中心接口单元软件设计

数据中心接口单元的软件设计如图3所示。PS部分的ARM双核运行Linux3.15.0操作系统。驱动运行在内核态,应用程序运行在用户态。

图3 数据中心接口单元软件设计

驱动是连接数据中心接口模块(FPGA)和上层软件的桥梁,驱动为用户程序提供了对数据中心接口模块基本的读(Read)、写(Write)和I/O操作(I/O Control)。驱动代码在操作系统的内核态执行。驱动中对设备的读写与数据中心接口模块的DMA过程对应。为满足上行较高的数据率,驱动的读操作对应DMA的Scatter/Gather模式,而写操作则对应Simple DMA模式。

读操作采用了阻塞I/O的方式,一次DMA完成后驱动会收到来自数据中心接口模块的中断信号,在中断处理函数中会唤醒Read函数中的休眠,Read函数把数据由内核空间拷贝到用户空间,如果没有数据可以拷贝,Read函数将会进入休眠模式。在中断处理函数清空中断信号后,准备接受下一次中断的到来。

写操作首先将用户空间传递来的数据拷贝至内核空间对应的写DMA缓冲区,然后将写缓冲区对应的物理地址和长度信息写入DMA控制器对应的I/O地址,数据中心接口模块开始接收DMA操作。

应用程序用TCP/IP协议与PC进行数据交互,利用驱动提供的读、写和I/O操作的接口与数据中心接口单元的PL部分进行交互,具有数据传输、帧解析、命令帧下发等功能。

1.3 数据帧合并打包的实现

数据帧的合并打包通过驱动和FPGA协同完成。

驱动部分:申请大小为LB的DMA缓冲区,其中L为基于硬件可靠传输协议中定长数据帧长度的n倍(n的值可以在一定范围控制),为用户空间TCP/IP协议要处理的数据包的长度;将申请到DMA缓冲区的地址和长度L写入指定寄存器。

FPGA部分:当接收到数据节点传来的数据帧时,根据指定寄存器中驱动写入的DMA缓冲区地址和长度将n个定长数据帧按解析后帧头的帧序号顺序写入DMA缓冲区,并发送一次中断,驱动收到中断,将合并打包后长度为L的长数据帧发送到用户空间。

大块的DMA缓冲区起到以下作用:(1)将短数据帧打包合并,减少上层TCP协议栈处理大量短数据帧对CPU的损耗;(2)数据帧按帧序号进行排序;(3)大大减少DMA中断次数。

2 性能测试

千兆以太网数据源使用思博伦公司生产的网络数据分析仪Spirent TestCenter C1[7],该网络分析仪有 4个10/100/1 000 BASE-T端口和精度极高的内部硬件时戳。配合Windows端软件Spirent TestCenter Application可以生成512个发送和511个可追踪接收流,且帧长度60~16 004 B内可变,发送速率每3.43 s一个包到101%线速率间可变,接收端可以统计帧CRC、嵌入式CRC和PRBS位错误。

数据中心选用Think Pad E450笔记本,搭载Intel酷睿i5处理器,Windows 7操作系统。数据中心接口模块与数据源、数据中心之间都通过长3 m的CAT-5e超五类网线连接。

千兆以太网上的实际数据传输速率根据以太网标准,除去前导符与帧间隙,使用基于硬件的可靠传输协议的定长数据帧进行测试。其中定长数据帧有效长度为796 B,冗余信息包括8 B前导符和12 B帧间隔,共计20 B。

设实际数据率为Rreal,有效数据率为Rvalid,有效数据长度为lvalid,故:

(1)

所以千兆以太网有效数据率最高为:

(2)

帧速率为:

975.49 Mb/s÷(796×8 bit)=153 186 f/s

(3)

即在FPGA不对数据帧进行打包的情况下驱动要响应每秒15万多次的中断。

(1)测试数据中心接口单元和数据节点之间基于硬件可靠传输协议的数据传输。数据源在测试中模拟数据节点。测试数据率可以使用网络数据源发帧并统计丢帧数。数据中心接口单元性能测试连接图如图4所示。

图4 数据中心接口单元性能测试连接图

在1 000 Mb/s的线速率下(有效数据率为975.49 Mb/s),数据源发送了54 273 312个帧,FPGA和驱动也接收到同样数目的帧。由以上测试数据可以得出,数据中心接口单元可以在基于硬件的可靠传输协议下接收975.49 Mb/s数据率的数据,并通过驱动将数据可靠地送达系统上层用户空间。

(2)测试数据中心接口单元和数据中心间基于TCP/IP协议的数据传输,可以通过网络性能测试工具IPERF测试不同帧长度下的数据率。

如图5所示,数据中心接口单元到数据中心之间的TCP/IP数据传输速率最高可达534 Mb/s,没有完全利用千兆以太网带宽,这是由于处理器的性能有限,TCP/IP协议对报文的处理占用了大量的CPU资源。

图5 数据中心接口单元到数据中心的有效数据率

(3)测试数据节点发送数据帧经由数据中心接口单元传输到数据中心的可靠数据率。测试中数据源模拟数据节点;数据中心运行数据中心主控程序,统计并存储数据帧;数据中心接口单元可以调整对定长数据帧的打包(将n个定长数据帧合并成长数据帧,调整n的值),从而控制和数据中心之间基于TCP/IP协议传输数据帧的长度。

如图6所示,数据中心接口单元在实际数据传输中可达330 Mb/s的可靠数据率。由图5和图6可以明显看出数据传输速率与帧长度有着较大的关系。由于协议栈需要对每个报文进行处理,处理时间与报文长度无关,在同样的数据量下,当传输报文长度变低时,协议栈报文处理频率会相应增加,数据率相较长报文时明显下降[8]。所以为了提高数据传输速率,对数据帧进行合并打包是非常必要的。

图6 数据源经由数据中心接口单元到数据中心的有效数据率

测试结果表明,单独测试数据中心接口单元两端千兆以太网接口的数据率分别达到975.49 Mb/s和534 Mb/s,然而最终数据帧由数据源经过两个千兆以太网接口可靠地传输到数据中心的数据率最高只达到330 Mb/s,较较低的534 Mb/s仍有差距。经过分析,这部分数据率的下降是由于:(1)DMA传输的过程要涉及高速缓存一致性(cache coherence)的问题,要保持高速缓存和内存的一致性需要一些操作,在数据传输过程中会消耗一部分时间,导致数据率的下降;(2)数据由内核态到用户态的拷贝消耗一部分时间,导致数据率的下降。

3 结论

本文基于Xilinx ZYNQ芯片,通过软硬件协同设计,实现了用于大规模数据采集系统的可靠数据中心接口模块。在大规模数据采集系统中,数据节点之间数据可靠性是通过基于硬件的可靠传输协议实现的,该数据中心接口模块是基于硬件的可靠传输协议和传统TCP/IP协议之间的桥梁,可以使数据中心(PC)能够用传统的TCP/IP协议接收数据节点传来的采集数据,而且保证了数据在高数据率下的可靠性。该数据中心接口模块各项参数测试达标后,在实际的数据采集项目中进行了应用,稳定地完成了三次野外数据采集试验。

数据中心接口模块和数据节点之间的千兆以太网带宽占用率几乎达到了理想的100%,然而数据中心接口模块和数据中心之间的千兆以太网带宽占用率还有提升的空间,未来可通过提升PS部分硬件性能或者优化软件和协议栈来提升。