基于JESD204B的高速串行数据收发接口设计

2018-10-18徐凤萍龚至诚

徐凤萍,龚至诚,王 巍

(1.江苏自动化研究所,江苏 连云港 222061;2.江苏科技大学电子信息学院,江苏 镇江 212003)

JESD204B是一种新型的基于高速SERDES的AD/DA数据收发传输接口,而高速AD/DA数据收发传输接口是集成电路当中最关键的设计实现环节,其涵盖了模数转换(ADC,Analog-to-Digital Converter)和数模转换(Digital-to-Analog Converter,DAC)[1]。在此之前,绝大多数高速AD/DA转换数据收发接口采用LVDS接口,目前随着数字信号处理方法不断发展以及科技的持续进步,对集成电路传输及转换的速度和带宽要求也越来越高,以往的普通转换模块已经不能满足需求,这样就促进了高速ADC/DAC等集成电路在高速传输技术方面的急速发展[2]。

以往采样数据的传输方式在传统用法上多采用如LVDS传输等并行方式,但是并行方式容易出现时钟同步困难、串行干扰大等问题,使信号容易受到干扰。同时并行传输方式会产生PCB板设计繁琐、层数增多、花费高等众多难题。本文在JESD204B的基础上,对高速串行数据收发接口的设计方法和实现途径进行了研究,通过在Xilinx公司的Virtex-7 系列FPGA内集成,完成基于JESD204B协议的高速SERDES的AD/DA数据收发传输接口设计与集成实现,并完成信息的传输验证及相关试验。

1 JESD204B协议的优势

数据转换器与FPGA与的接口电平标准最常见的有两种,一种是互补金属氧化物半导体(简称CMOS),另一种是低电压差分信号(简称LVDS)。上述两种类型的区别主要在于CMOS的瞬态电流随信息转换率的升高而逐渐变大,而LVDS的电流则比较稳定,可是因为LVDS对应的最高支持接口速率相对目前的应用需求也是相对较低的,最高只有2 Gb/s左右[3]。随着相关技术的进步,对相关转换器传输率、低功耗、高带宽等层面的要求逐渐提高,对应的传统的CMOS/LVDS两种接口电平方式逐渐无法满足应用需求,特别是在转换速度、数据带宽、分辨率、功耗等方面无法满足高速AD/DA的发展与应用的需求。

针对高带宽、高速率、低功耗需求的,JESD204B传输协议提出了一种高效地基于高速串行数据接口的解决方案,JESD204B协议的主要技术优势在于:简化系统设计复杂度,设计使用上相对精简,PCB布局更简洁,减少PCB上的引脚数量,将多引脚低速的并行接口方式变更为少量引脚的高速串行接口方式,可实现相对更小体积的IC封装及电路板布局,节省了硬件成本。由于具备以上优点,使得JESD204B协议非常适用于高速传输应用需求,例如4G、雷达信号、光电信号、军用视频传输等。

目前,主流半导体厂商基本上已经完成了基于JESD204B的高速数据转换器产品的研制,并提供芯片级产品,因此针对高速串行传输的接口设计也很必要[4]。本文利用FPGA的硬件可编程、运行速度快、稳定可靠、高速收发器支持JESD204B协议的特点,将FPGA与ADC/DAC结合使用,构造出的系统应用方案见图1。

图1 FPGA与DAC/ADC实现数据传输应用方案示意图

2 JESD204B协议接口组成

JESD204B协议从组成上主要由4部分组成,即物理层、链路层、数据传输层以及应用层等,对应的架构组成具体如图2所展示。

图2 JESD204B 协议组成示意图

其中JESD204B的物理层主要负责完成串行高速数据的接收发送,以及串行数据与并行数据的转换,实现数据包的缓冲、数据包的调度与仲裁、数据包的发送与接收、差错检测等功能,物理层传输数据是按照比特流的方式进行的[5]。在本文设计得到的高速串行收发接口上,利用FPGA的transceiver来进行上述协议的物理层操作。

JESD204B链路层主要完成对采用数据的8B/10B解码与编码以及后续链路操作,同步数据的字节编码等步骤都是借助链路层相关的发送端实现的;可是信息同步的有关指令以及还原操作等均是借助链路层相关的接收端实现的[6]。

JESD204B的传输层完成发送及接收数据的调整编制等功能。数据在发送时需要按照用户的格式需求进行打包处理,通常需要对数据进行尾码和控制位的增加;数据在接收端时需要按照用户的格式需求进行尾码和控制位的删除,将数据恢复出来完成传输。

3 设计与实现

3.1 总体设计方案

本文的FPGA芯片选用了Xilinx推出的FPGA-XC7VX1140T,在该硬件芯片的基础上进行设计与实现,XC7VX1140T具备96组的GTH 高速数据收发器,该GTH 高速数据收发器所能够提供的最大线上速度为13.1 Gb/s,而该协议对应的串行数据传输速率的最大为12.5 Gb/s,没有超出芯片对应的最大上限,故而能够满足技术需求[7]。

在设计之初,根据预定的最高传输速率,来确定时钟频率。本文设定数据采样频率等于600 MS/s,由于本文设计采样信息均是16位,因此本文设定的线上速率等于(600 M×16) b/s,而且信息通信过程中借助8b/10b方式完成编码操作,所以对应的设计速率满足12 Gb/s要求,没有超过协议的最高速率。实际使用时,为了平衡样本采集率和线上速度,在高8和低8位的2个通道上拆开数据后将其传送,这样就可使每个通道的速度均下降等于6 Gb/s,不到协议最高速度的50%,可以满足数据的采样率要求[8]。

依据时钟主频core clk=line rate/40的相对关系,可计算出系统的时钟频率满足150 Mhz,为了保证相关信号处于平稳状态,采用外部信号源,提供600 MHz频率的差分信号,通过4分频的时钟芯片得到150 Mhz差分时钟源信号,然后提供给FPGA使用。

在实施链路设计时,主要涉及下面五个重要参数:

L:链路中通道数 (预设成2);

F:帧中的字节个数 (预设为1);

S:转换器的任意帧变换样本的数量(预设为1);

K:多帧中的帧数(预设为32);

M:全部数据转换器总量(预置成1)。

本文依据前面论述的样本采集率及时钟频率的取值,在这里把链路的各项参数数值均进行了预设。

本文在传输数据方面采用两个通道将数据分高八位和低八位分开传输的方式,这样每个通道都可在150 MHz的时钟频率下工作,完成每个时钟周期内4个点的信息传输,通道带宽可保证32位,可以符合系统样本采集率的需要[9]。

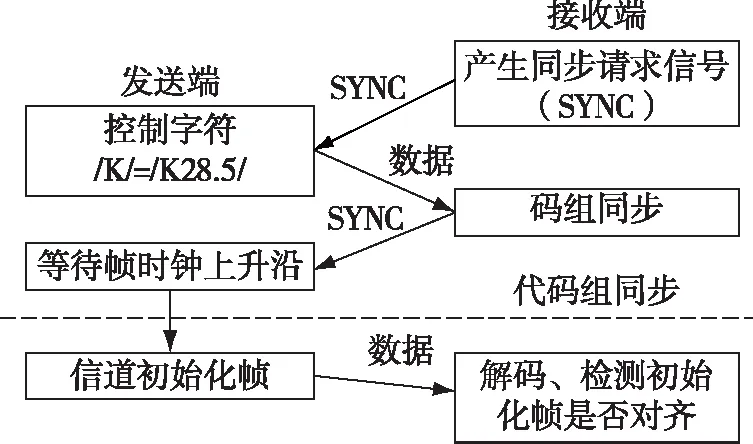

3.2 传输数据同步实现机制

数据传输时,无论发送端还是接收端,都要求通道间实现严格的同步协调,这一点很重要,在发送端和接收端上都需要做到严格的同步进而确保数据传输正确性。在JESD204B协议下,设计了在传输的不同阶段使用自定义的不同数据帧结构来实现同步机制。在JESD204B的数据链路层就利用8b/10b方式获取后的-K码来编制实现同步机制并构造数据帧[10]。实际进行数据传输之前,链路上还要完成代码组同步和初始化帧同步的过程,数据同步流程如图3所示。

图3 同步过程示意图

主要步骤包括:

1)接收端将SYNC信号置低,向发送端发出同步请求指令;

2)发送端收到传递过来的同步请求指令信息之后,马上给对应的接收端发出相关的控制字符命令,完成对应的同步操作;

3)接收端持续获取到至少四个/K28.5/控制指令后,将SYNC位置高,结束该过程。此时同步已经实现,等待本地帧时钟开始向上沿变化后再开始信道数据帧的同步实施。

代码组、初始化帧架构对应的同步过程相关时序关系具体如图4所展示。

图4 代码组、初始化帧架构以及相关同步过程时序图

其中,/K/字符用于首先进行的代码组同步;/R/字符表示采样信息多帧的同步初始化过程启动;/A/字符表示采样信息多帧的同步初始化过程的终止;/Q/字符表示接收端配置的信息[11]。由图4可见,利用8b/10b结合特殊控制字可以顺利完成同步,同时也可满足监控、故障检测的技术需求。各字符定义如下:

/K/=/K28.5/;

/R/=/K28.0/;

/A/=/K28.3/;

/Q/=/K28.4/。

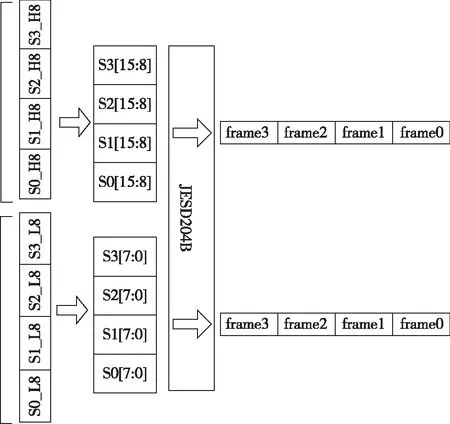

3.3 数据传输方案

在设计中兼顾数据了采样率和串行线上速率两个要素,在具体实现中设计了如图5所示的高密度数据传输方式:在发送端利用2个独立的通道分开进行样本采集信息的高8位及低8位的同步传送。

图5 高密度信息传输方案示意图

4 实验测试结果分析

4.1 设计框架图

具体实验验证时,通过采用FPGA自收发环路来测试验证数据传送接口的功能性能,本地时钟频率和收发器时钟都为150 MHz,将FPGA对应的发送端与接收端分别使用两对GTH接高速串行收发器,取样数据从发送端发出去后,通过0.01 uf的隔直电容后接入接收端,此时,线上的高速数据传输速率达到6 Gb/s,本文设计的电路板为8层结构。实验环境设计如图6所示。

图6 试验检测电路模块架构图

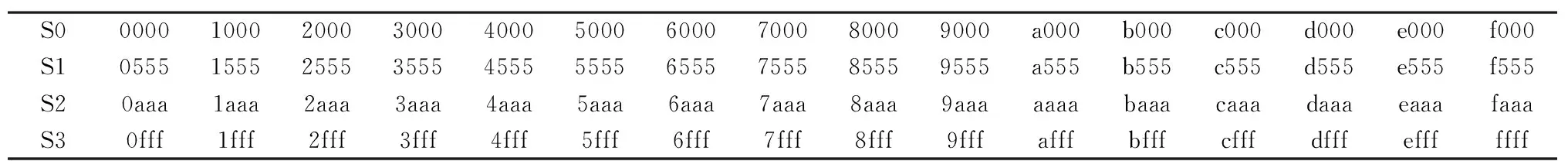

4.2 测试结果

实验中使用AXI-LITE来完成信息收发接口上的各种链路参数的设置,设置数据打包封装形式、通路、同步操作方式等各种参数,保证数据传输链路的正确建立。在试验过程汇总,为了确保传输的精准性以及满足有关同步要求,本文使用递增码作为对应的检测码,以便于在实验中总结错误,实验采用的测试码见表1。

表1 测试码数据表

实验中使用了两个lane通道来传输采用数据,每个通道均为32 bit位宽,分别传输数据高8位和低8位。接收端收到的传输信息为64位位宽,该传输信息中集成了4个采样信息。因此,对把FPGA接收端口获取的数据进行划分后可分为4路数据,获取到4路数据的图像。实测后发现接收端收到的信息与发送端传送的信息可以对应,信息没有错误,充分说明了发送和接收均无误,证明了实验搭建的测试电路的两个通道之间是完全同步的。

5 结束语

在串行接口速率不断提高的技术发展下,ADC/DAC的技术也将向着高速串行接口传输的方向发展。本篇文章借助JESD204B协议组件,实现高速的串行状态数据接口的设计,以FPAG为基础实现了有关试验电路的创建,检测了数据高速收发接口功能,证明了该数据接口在设计上的正确。本文设计的高速串行收发接口可结合DAC/ADC进行应用,有显著的实际意义。