一种高稳定度发射接收同步系统的设计方法

2018-10-17谭博

谭博

(第七一五研究所,杭州,310023)

水声通信系统中,水声信号的发射声波与接收回波时延直接影响测距精度。其中传播时延主要包括发射抖动误差、信号传播路径时延、接收处理时延,其中接收处理时延主要由前置放大电路、滤波电路的相位不一致性以及模数转换电路的采样偏差构成。通常情况下,声呐前置预处理设备会明确规定接收通道间的相位一致性要求[1]。本文重点从发送端与接收端描述声信号发射控制与声信号采集控制的同步设计方案与实现,既满足接收通道间相位一致性要求,又将发射与接收同步精度控制在亚微秒级。

1 系统设计

通常声呐系统设计中,发射控制信号与采集控制信号为非同源控制,当发射控制信号有效时,发射机开始发射信号,但此时各分布式采集节点的采集起始时刻按照接收同步进行控制,而在整理各采集节点数据时,根据发射控制信号添加发射起始标志,这样在声信号接收处理过程中,信号采集的起始时刻相对于声信号的发射起始时刻存在较大的抖动误差,一般在毫秒级范围内。本文将发射控制信号与采集时钟设计为同步工作模式,如图1 所示。

图1 收发同步系统架构

图1中,控制中心主要实现产生发射控制信号与采集时钟同步信号,两种信号的边沿同步,同时接收各个采集节点的数据信号。采集节点同时接收发射控制信号和采集时钟同步信号。发射控制信号用于指示发射开始标志位,用于采集节点对千兆以太网包数据进行标记。采集时钟同步信号用于同步各个采集节点的模数转换控制时钟信号,保证各个采集节点采样过程的同步性。发射系统主要是根据发射控制信号来产生发射信号,发射控制信号用于控制发射系统的发射信号起始点。

该设计方法将发射和接收采用同源控制,其优势在于将各个采集节点、发射系统与控制中心的同步控制设计成一个精准同步系统,通过采集同步时钟链路使得采集节点的工作时钟与控制中心的工作时钟同步,同时控制发射机的发射控制信号与控制中心时钟同步,进而可以严格控制发射起始时刻与采集起始时刻的同步关系。

2 收发同步设计

2.1 收发同步原理

收发同步设计要达到高稳定度、高精度,其原理如图1所示。在发送端,发射同步信号和采集同步信号同源同时刻对齐发送;在接收端,利用本地高频时钟采样同步信号,高频时钟的周期控制在20 ns内,使其收发同步精度为亚微秒级。本设计中,发送端发射同步信号和采集同步信号严格对齐发送;接收端分为两部分,一部分是采集节点接收,另一部分是发射系统接收。采集节点接收过程中物理链路时间抖动约20 ns,采样采集同步信号的高频时钟频率307.2 MHz,采样发射同步信号即用千兆以太网打包标记的高频时钟频率76.8 MHz;采集节点接收同步信号过程精度约40 ns,而发射系统接收主频时钟频率为100 MHz,在采样发射同步信号时执行时间约 32个时钟周期,物理链路时间抖动约20 ns,即发射系统接收同步信号过程精度约340 ns;因此理论上收发同步精度可控在380 ns。

2.2 发送端设计

发送端是以FPGA为核心芯片,主要实现节点的采集同步时钟产生和发射控制信号的产生,由控制中心板实现该功能。

同步时钟的产生原理如图2所示,控制中心在系统主时钟下进行工作,按照一定的帧格式如BYTE1、BYTE2、BYTE3、BYTE4循环产生串行比特流,然后由RS485接口发送至各个采集节点,每个字节设计为8位,包含1位起始位、6位数据位、1位停止位,波特率设计为800 kbps,字节速率为100 kbps,当每个字节发送结束后,产生字节发送完成标志信号Tx_done,其周期为10 μs。

当控制中心收到上位机下发的发射使能信号FS_en为高电平时,开始根据发射周期T产生发射控制信号FS_ctrl,发射控制信号的高电平固定为1 ms,周期由T值决定,发射周期T按照一定的周期进行更新。由于要求T的误差精度≤10 μs,使用Tx_done信号驱动产生 FS_ctrl,既可保证信号FS_ctrl的误差≤10 μs,又可使 FS_ctrl信号的上升沿与Tx_done的边沿对齐,采集同步时钟和发射控制信号均通过RS485接口发送至各个采集节点。对发送端进行功能仿真,仿真结果如图3所示。

图2 发送端时钟产生原理

图3 发送端功能仿真结果

图3(a)中FS_ctrl信号根据发射周期trans_T值进行产生,高电平固定;图3(b)为(a)的放大图,Tx_done为字节发送数据TX_data的结束标志,而且TX_data为循环发送数据;图3(c)为(b)的放大图,可看出FS_ctrl的边沿与Tx_done信号边沿对齐。

2.3 接收端设计

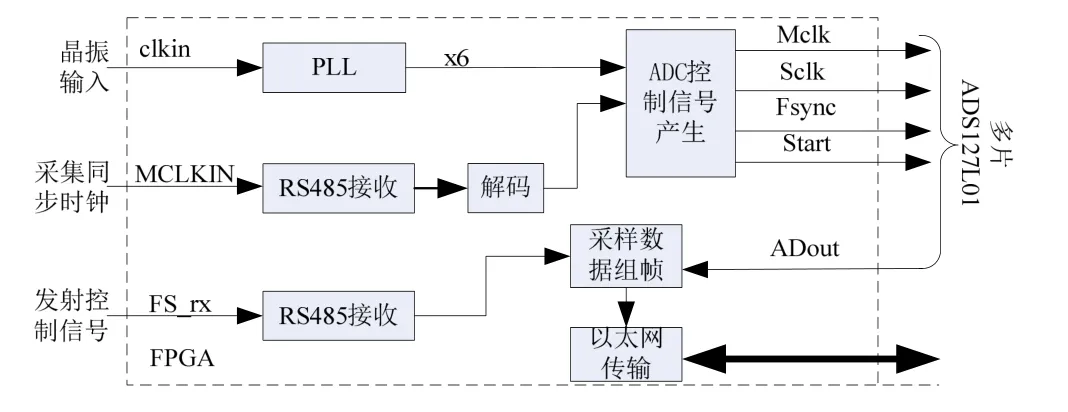

接收端采集节点模块是以FPGA为核心芯片,控制 ADC芯片完成接收声数据的模数转换,通常情况下,单个采集节点模块完成多路声信号的模数转换,实现方案如图4所示。

图4 采集节点实现框图

在采集模块中,首先接收主控中心下发的采集同步时钟信号和发射控制信号。FPGA作为主控芯片,在本地晶振时钟的驱动下,进行6倍频,使用倍频后的高频时钟作为FPGA工作主时钟,对接收的采集同步时钟进行解码。按照发送帧格式解析数据,当接收数据为BYTE1和BYTE3时,产生高电平;当接收数据为BYTE2和BYTE4时,产生低电平。这样可恢复出频率为50 kHz的时钟,而且恢复时钟的上升沿和下降沿均与发送端的Tx_done信号边沿对齐。在主时钟驱动下,通过分频产生 ADC控制信号,恢复时钟的边沿作为分频器计数器的清零信号,这样可保证不同采集节点的 ADC控制信号同步,误差为一个高频时钟周期。将多片 ADC采集输出数据按照 UDP协议格式进行以太网包组帧,当接收端检测到发射控制信号的上升沿时,在当前以太网包中添加指标标识 0xAA,用于标识当前以太网包对应数据为发射开始时刻数据,为后续延时测量计算提供初始时刻。

为满足高频声呐采样率的要求,选用 TI公司的Σ-Δ型 ADC-ADS127L01[2],该款 ADC最高采样率可达512 kbps。本文设计采样率为300 kbps,工作在HR模式,采用Frame_Sync Slave控制模式,取OSR=32,取WB1滤波,电路设计如图5所示。

根据芯片数据手册,工作在Frame_Sync Slave模式下,ADS127L01时序控制要求如图6所示,在采样率为300 kbps情况下,MCLK与SCLK频率为9.6 MHz,Fsync频率为300 kHz。

图6 ADS127L01控制时序要求

选取本地晶振频率为51.2 MHz,经过6倍频后为 307.2 MHz,然后再分别进行 32分频得到 9.6 MHz时钟和1 024分频得到300 kHz时钟。由于接收恢复时钟边沿变化频率为100 kHz,在每个分频清零周期内主时钟计数3 072次,即在每个清零周期内 ADC完成三次采样过程,而且采样的起始时刻与Tx_done信号对齐,即与发射控制信号的起始时刻对齐,从而实现采集起始时刻与发射起始时刻同步。

3 实测结果

发射系统在发射控制信号的控制下产生一个固定频率的调制波,各个采集节点通过千兆以太网将采集数据发送至控制中心,然后由控制中心发送至上位机处理平台。使用数据采集软件保存20 s的数据,然后使用LABVIEW软件进行波形分析与计算,将数据包中含有0xAA的数据包作为分析的起始时刻,分别计算各个采集通道采集到的调制波起始时刻相对于分析起始时刻的延时量,计算延时量最大值与最小值的差即为发射同步与采集同步误差精度。经过多次测试试验,在采样率为300 kbps条件下,消除各环节的固定时延,发射与接收采集同步起伏误差为400 ns。

4 结论

该同步设计方案经过样机研制验证,使用过程中同步精度稳定可靠,满足指标要求。发射启动和接收采集通过控制中心同源同步控制,相比原有非同源控制,同步起伏误差由毫秒级缩减至400 ns内,相应测距精度由米级提高至厘米级,可应用于高精度测距声呐、成像声呐系统。同时,该同步系统具有较强的抗干扰能力。首先,同步时钟不是采用单频信号传输,而是采用基于UART串口协议;其次,同步信号是周期性校准,即使某些时刻受到干扰,也不会影响整个同步系统。