一种半实物雷达仿真测试系统的设计与实现

2018-10-12于艺伟邱军海刘恒燕

于艺伟,邱军海,刘恒燕,宋 杰

(1.海军航空大学,山东烟台264001;2.烟台工程职业技术学院,山东烟台264000)

半实物雷达仿真测试系统是研发平台分布交互式仿真试验系统的重要组成部分,是半实物雷达系统不可或缺的部分,可对不同软硬件设备产生的试验数据进行统一的采集、转换、传输、交互与管理,支持全数字和半实物的实时/非实时仿真试验应用[1-3]。本文针对某半实物雷达仿真测试系统项目的具体需求,对射频信号发生、试验数据采集、数据回放等模块进行了详细设计,最终完成了各个模块的开发与集成。

1 设计方案

1.1 需求分析

某半实物雷达仿真测试系统中的射频信号发生模块包含S和X 2个工作频段,需要通过射频信号远程控制设备进行控制,试验数据经过采集处理到计算机中进行数据格式转换、存储和试验数据处理。

该项目中,半实物雷达仿真测试应用模式有2种:一是接收半实物雷达发射机产生的射频信号,实现下变频至中频信号,数据采集卡完成对中频信号的采集以及数据传送、保存和显示,然后经过数据分析处理、通过数据回放卡和上变频模块最终送至半实物雷达接收机;二是数据采集卡支持对半实物待测设备的中频输出采集以及数据传送、保存及显示,后经过数据分析处理、通过数据回放卡和上变频模块最终送至半实物待测设备[4-9]。

1.2 总体架构

该系统的总体架构如图1所示。主要包括3个基本模块:射频模拟模块、数据采集模块以及数据回放模块[10]。

图1 半实物雷达仿真测试系统总体架构图Fig.1 Overall architecture of the simulation-test system in semi-physical radar

根据上述架构,针对半实物待测设备提出2种测试方案。

方案一:射频模块对半实物雷达发射机产生的射频信号进行下变频至中频信号;数据采集卡完成对中频信号的直接中频采样,并通过计算机PCI总线将中频信号传输到PC机中进行数字下变频处理,生成基带信号,并保存采集数据文件;PC机完成对基带信号的事后分析,根据算法重新生成基带信号,通过计算机PCI总线将基带信号传输到数据回放卡上,完成对基带信号的数字上变频和数据回放,生成中频信号;射频模块再对中频信号进行上变频至射频信号,最后送半实物雷达接收机,从而构成一个完整的射频测试回路。

方案二:数据采集卡直接对半实物待测设备的中频输出进行采集,并通过计算机PCI总线将中频信号传输到PC机中,并在PC机中进行数字下变频处理,生成基带信号,并保存采集数据文件;输出的基带信号经过分析处理后到数据回放卡,经数字上变频和D/A后直接接到半实物待测设备的中频输入,从而构成一个完整的中频测试回路。

2 各模块具体设计方案

2.1 射频模拟模块

2.1.1 主要功能指标

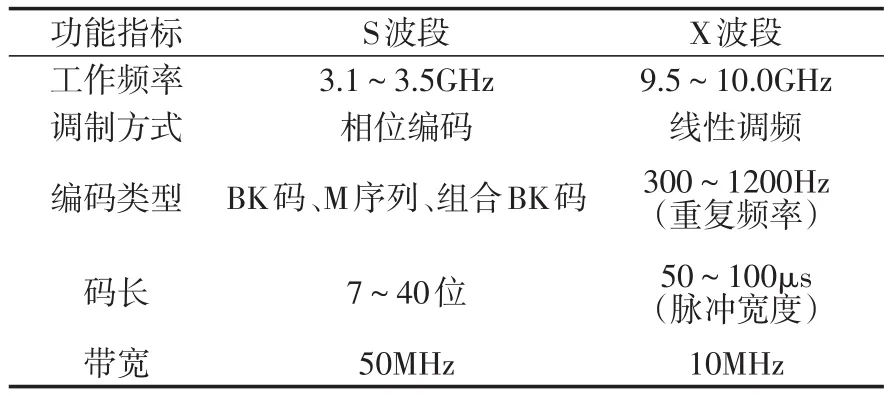

射频模拟模块共分为2个波段:S波段和X波段,主要完成这2个波段的射频信号的上变频和下变频。每个波段可完成的功能指标如表1所示。

2.1.2 射频模拟模块组成

射频模拟模块能完成在2个波段(S波段和X波段)内产生相应的本振信号;对半实物雷达发射机产生的射频信号进行下变频至中频信号;对中频信号进行上变频至射频信号送半实物雷达接收机。针对不同波段,射频模拟模块要单独设计,即2部不同波段的半实物雷达要配2套射频模拟模块。

表1 不同波段工作指标Tab.1 Indicators for Different Band

2.1.3 射频模拟模块具体设计

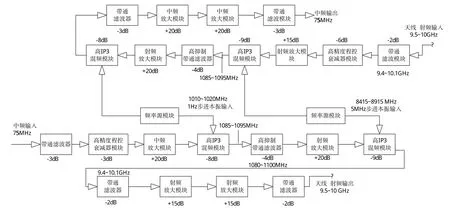

射频模拟模块主要包括频率源、下变频组件和上变频组件。

下变频组件由射频预选滤波器、衰减器、低噪声放大器、一次变频器,带通滤波器、射频放大器、二次变频器、中频带通滤波器、中频放大器等组成。

上变频组件由中频带通滤波器、衰减器、中频放大器、一次变频器,带通滤波器、射频放大器、二次变频器、射频滤波器、射频放大器等组成,如图2所示。

图2 变频组件组成原理框图Fig.2 Functional block diagram of frequency-conversion component

下变频时,信号经天线首先经过射频预选滤波器(射频预选滤波器为第一级射频带通滤波模块,如X波段射频输入范围为9.5~10.0GHz,则带通滤波模块的通带可设计为9.4~10.1GHz,比射频输入范围略大一些)对输入信号进行选择;再经过衰减器,如果输入信号较大则进行衰减,如果输入信号较小,信号不衰减。衰减器之后对信号进行低噪声放大,放大之后进行一次混频,得到第一中频信号,经过带通滤波后进行射频放大。第一中频经过放大后进行二次混频,得到第二中频(即输出中频频率),经过中频带通滤波器、中频放大器、中频带通滤波器后输出。

上变频时,中频信号首先经过中频预选滤波器对输入信号进行选择;再经过衰减器,如果输入信号较大,信号进行衰减,如果输入信号较小,信号不衰减。衰减器之后对信号进行中频放大,放大之后进行一次混频,得到第二中频信号,经过带通滤波后进行射频放大。第二中频经过放大后进行二次混频,得到射频信号(即输出射频频率),经过射频带通滤波器、射频放大器、射频带通滤波器后输出。

2.2 数据采集模块

2.2.1 数据采集模块设计方案

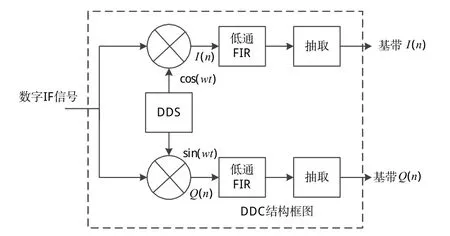

试验数据采集处理设备以工控机作为采集主控设备,试验数据的采集由自行研制的试验数据采集卡来完成。试验数据采集卡采集中频信号的同时,还要完成数字下变频的任务,此任务由数据采集卡上的FPGA芯片完成,数字下变频的FPGA实现原理结构框图如图3所示。

图3 数字下变频的FPGA实现原理图Fig.3 Schematic diagram of FPGArealization of digital down conversion

数字下变频是将采样信号从较高频带搬移到较低频带,如果数据率较大,还要进行抽取,以降低采样速率。数字下变频主要由数字振荡器、数字混频器和抽取滤波3部分组成。在FPGA中,数字振荡器由直接频率合成器(DDS)实现,混频器由乘法器实现,滤波则由FIR数字滤波器实现[11-14]。

2.2.2 数据采集模块硬件设计

数据采集卡实际硬件结构如图4所示。基于PCI总线的试验数据采集卡工作最高频率为105 MHz,基本满足大多数试验数据的采集,可根据实际需要重新配置FPGA来对A/D的采样时钟进行设置。

FPGA任务划分:根据PC机通过PCI总线发送的采集参数(包括采样率设置、数据来源、触发方式、触发抽取方式、采样波门参数、数据存储方式以及采集起始命令等)来完成对雷达视频信号的波门控制,将采集数据配置为16 bit,并将每次触发后采集的数据添加24个16 bit的头信息,然后交替送入FIFOA和FIFOB。

图4 数据采集卡硬件结构框图Fig.4 Hardware structure of data acquisition card

CPLD任务划分:响应PCI桥(AMCC5935)的ADDON端信号,实现AMCC5935的FIFO、Passthru以及MailBox传输。其中,FIFO传输用于以DMA方式传送大批量的数据(本采集设备单次DMA传输512KB);Passthru传输用于接收来自PCI总线的命令,对单个数据(或极小批量)进行读取;MailBox传输主要用于向PCI总线发送中断信号。当PCI启动DMA传输时,AMCC5935内ADDON至PCI的FIFO内数据会减少,CPLD负责将图4中FIFOA和FIFOB的数据实时传送到AMCC5935的ADDON至PCI的FIFO,保证DMA传输的正常;当PCI启动Passthru传输时,CPLD接收来自AMCC5935的命令字,并响应;当板卡有事件产生时,负责向AMCC5935产生中断。

2.2.3 数据采集模块软件设计

数据采集模块软件完成对采集到的中频数据的数字下变频处理,生成基带信号,进行格式转换,并保存采集数据文件。应用程序通过驱动程序与数据采集卡通讯,向PCI采集卡传送各种命令字,并接收采集卡的数据。

操作系统采用微软的Windows操作系统,编程语言选用VC。数据采集模块所有的操作基本上由软件来控制,软件界面由数据库、参数设置、数据采集、数据分析、帮助等构成。

2.3 数据回放模块

2.3.1 数据回放模块设计方案

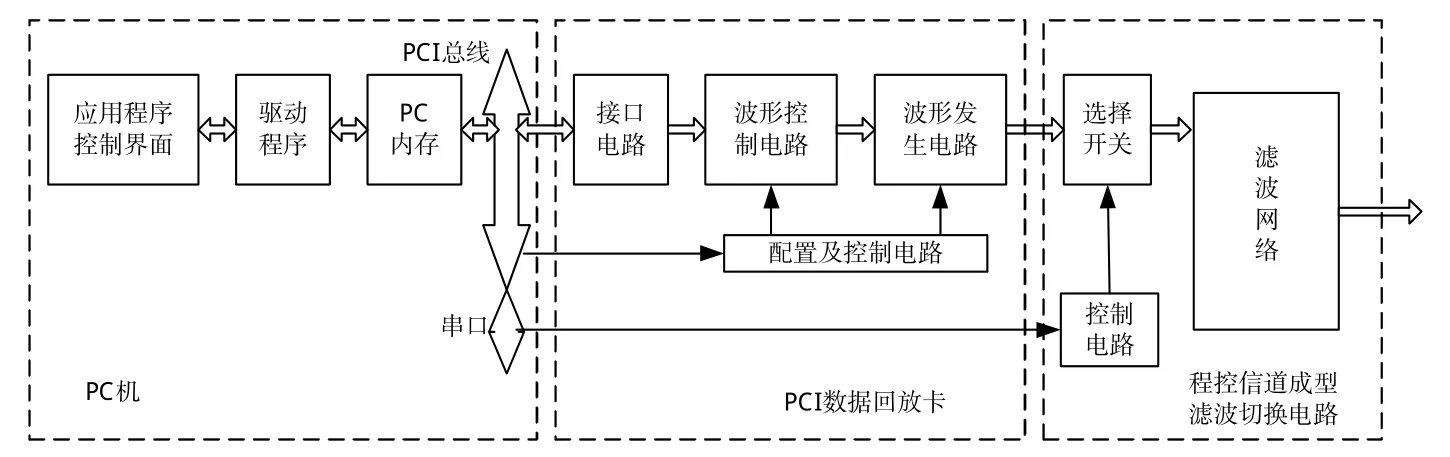

数据回放模块组成框图如图5所示。硬件部分包括数据回放卡和程控信道成型滤波切换电路,分别完成波形形成和模拟滤波功能[15-17]。软件部分包括应用程序控制和驱动程序,应用程序负责与用户交互,驱动程序主要完成顶层应用程序与底层硬件之间的控制与数据接口,应用程序将回放数据和控制命令通过驱动程序传送给硬件。

图5 数据回放模块组成框图Fig.5 Block diagram of data playback module

模块工作流程:本系统具备数据回放及信号模拟产生两大功能。应用程序根据用户的要求,如是数据回放则将待回放数据连续从存储介质中以分块方式连续读出,驱动程序以乒乓方式将计算机存储的实际数据(由数据采集系统采集而来的数据文件)连续不断地装入内存,然后通过PCI总线以DMA方式循环不断地将内存中的数据送入PCI数据回放卡的存储电路,经波形形成电路后送入后一级滤波电路;若选择信号模拟产生,则按照用户要求,将信号参数设置在数据回放卡中,硬件电路按照设置参数实时产生雷达信号波形。

2.3.2 数据回放模块硬件设计

数据回放模块的硬件设计采用FPGA+DSP+DUC+DA结构[19-20],与上位机采用PCI总线接口。FPGA主要完成时钟管理、逻辑控制、数据传输、内插滤波等功能;DSP主要完成PCI接口模块、中断管理、数据传输等功能,并提供数据缓存。其硬件设计框图如图6所示。

图6 数据回放模块硬件设计框图Fig.6 Block diagram of hardware design of data playback module

其中,DUC和D/A部分采用ADI公司的AD9957芯片,它集成了数字上变频和DAC,采样率为1GS/s,功耗比其他直接频率合成器减小50%以上,能产生中频为400 MHz的调制信号,且无杂散动态范围高达80dB。它有3种工作模式:正交调制模式、内插DAC模式和单音模式。当它工作在正交调制模式时,IQ两路分时复用一个18bit的并行数据输入口,一个I数据跟着一个Q数据,不断重复。

FPGA选用Xilinx公司Virtex-5 LX系列的XC5VLX50,该芯片支持2级速度,最大为550Mb/s,工业级耐温(-40℃~85℃),基本满足应用方案,是一个高性价比的解决方案。

DSP选用TI的TMSC6416T,其DSP内核主频高达1 GHz,在外部接口方面,它具有64个EDMA通道,每个通道都对应一个专用同步触发事件,使得EDMA可以被外设来的中断、外部硬件中断、其他EDMA传输完成的中断等事件触发,开始进行数据的搬移。此外,在TMS320C6416中,增加了一个PCI接口,使得DSP很容易通过PCI接口无缝连接到一个具有PCI功能的外部主CPU上。

2.3.3 数据回放模块软件设计

软件设计主要包括应用程序和驱动程序的设计。驱动程序的作用是完成应用程序与回放卡之间高速、可靠的数据传输任务。驱动程序编写成标准的WDM驱动程序,对系统中所需系统资源(如内存映射、中断申请、DMA内存)进行申请和管理。PCI数据回放卡驱动程序完成以下功能:向数据回放卡基址寄存器发送工作方式控制字、中断响应和DMA传输。驱动程序在系统内存空间中申请了DMA传输所需要的公共缓冲区(Buffer),DSP启动突发传输与这个Buffer进行直接数据传输。为了达到突发传输之间不相互干扰,Buffer以乒乓方式进行操作,就是每次中断以后板卡与另半个Buffer进行突发传输,同时刚才传输的Buffer与应用程序之间进行数据交换。

应用程序的主要功能包括:初始化参数设置、DDS配置、回放控制、数据传输等。应用程序面向用户,其作用是把硬盘中的数据写到内存中然后送给驱动,同时完成对回放卡及滤波网络的配置。

3 实验测试

3.1 射频模拟模块测试

如图7所示,主要测试射频模拟模块在S波段和X波段的上、下变频功能。上变频模块测试包含:上变频功能、增益、可控衰减、输出射频信号频点、上变频带宽等测试。下变频模块测试包含:下变频功能、增益、可控衰减、输出中频信号频点、下变频带宽等测试。X波段上变频的典型频谱测试结果(输出10.0 GHz)如图8所示。

3.2 数据采集模块测试

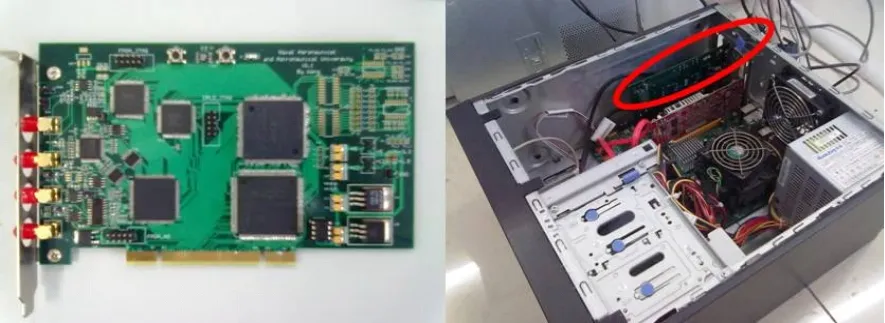

如图9所示,数据采集模块以PC工控机作为采集主控设备,模/数转换模块、高速数字I/O模块集成在一块高速数据采集PCI卡上。主要包含如下测试:数据采集数据波形实时显示功能、数据采集数据波形存储功能、数据采集卡采样率、数据采集卡FIFO存储深度、中频信号数字下变频功能基带信号格式转换功能、基带信号数据文件存储功能等测试。

图9 数据采集模块测试实物连接图Fig.9 Photograph of data acquisition module

3.3 数据回放模块测试

如图10所示,数据回放模块主要完成对基带信号的数字上变频和数据回放,生成中频信号功能。数据回放模块测试主要包含:IQ基带文件生成、点频信号数字上变频、中频载频频点、中频信号带宽、对射频信号发生模块进行远程动态控制等测试。

图10 数据回放模块测试实物连接图Fig.10 Photograph of data replay module

4 结束语

本文基于半实物雷达系统的测试需求,对半实物雷达仿真测试系统的多个模块进行设计。实现了对射频信号发生、试验数据采集、数据回放等模块的开发与集成,最终实现了半实物雷达仿真测试系统的设计。