利用KFM研究浮栅结构存储特性的实验设计

2018-10-11刘小花

许 杰, 刘小花, 徐 骏

(1. 南京邮电大学 电子与光学工程学院, 江苏 南京 210023;2. 南京大学 电子科学与工程学院, 江苏 南京 210093)

浮栅存储器是一种重要的微电子器件,已得到广泛应用[1]。浮栅存储单元是在传统的金属-氧化物-半导体(MOS)晶体管的氧化层中嵌入浮栅制备而成,浮栅多采用多晶硅或氮化硅材料制成,通过栅极电压的编程操作,沟道电荷能够隧穿进入浮栅并被存储起来,由此改变器件的阈值电压,实现存储功能。由于浮栅中的存储电荷不受器件断电影响,因此浮栅存储器是一种非易失性存储器[2]。在微电子专业的本科教学中,为了使学生了解学科发展动态,加深对浮栅存储器件的认识,设计和开展了相应的探究性实验教学,提高学生的创新意识与实践能力[3]。近年来,随着扫描探针显微技术的发展,开尔文力显微镜(KFM)被开发出来,能够在微观尺度探测材料表面电荷的存储和输运过程[4-5]。KFM测试具有无损伤探测、操作简便、环境友好、信号灵敏度高等优点,适合本科阶段实验教学的需要[6]。本实验设计利用KFM研究浮栅结构的电荷存储特性,并根据半导体器件物理知识定量计算注入电荷面密度,锻炼学生理论与实践相结合的能力。

1 实验原理

浮栅存储器工作时,电荷在栅压作用下注入并保持在浮栅介质中,而存储的电荷也会逐渐通过隧穿氧化层泄漏至衬底沟道,导致存储的失效[7]。浮栅电荷的保持时间越长,存储器的可靠性越好。KFM显微探测技术基于开尔文方法,通过纳米级的导电探针针尖探测试样表面的电势分布。利用KFM可实现在微观尺度下观察电荷在浮栅结构中的注入与保持特性[6]。最后,根据半导体器件物理知识,通过求解静电场泊松方程,可以获知KFM信号与电荷存储密度之间的定量关系。

2 实验

2.1 实验仪器与试样准备

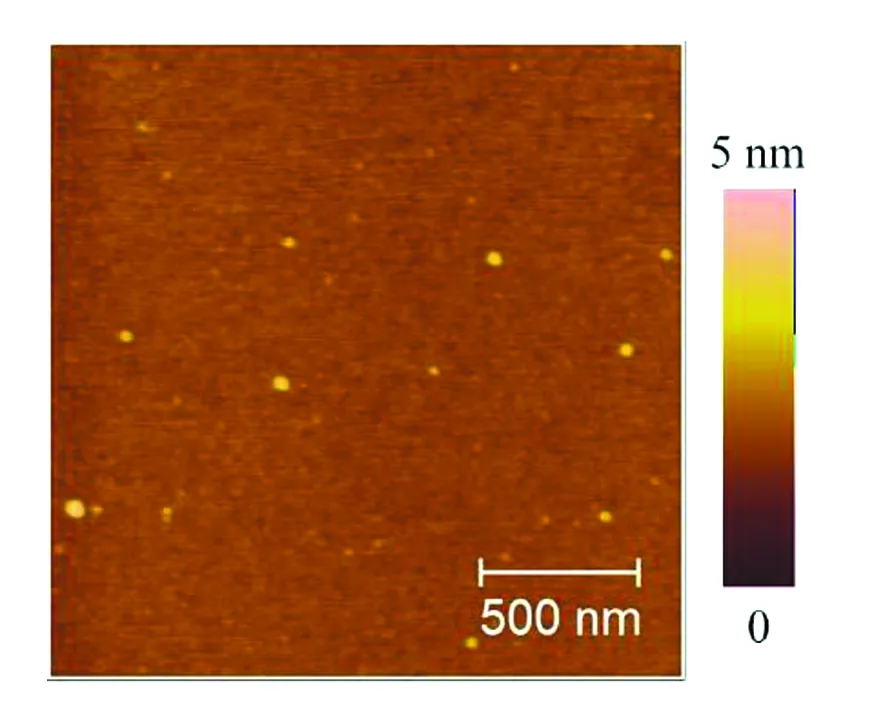

本实验中,KFM采用布鲁克公司Nanoscope 3D型号多模式原子力显微镜系统,导电探针选用布鲁克公司SCM-PIT型号。浮栅结构试样结构为氮化硅/氧化硅/p型硅衬底(Si3N4/SiO2/p-Si,衬底电阻率约为1 Ω·cm),其中氧化硅厚度约为3 nm,采用常规干氧氧化工艺制备,氮化硅厚度约为6 nm,采用等离子体增强化学气相沉积设备淀积制备,试样与样品托盘间采用导电银浆粘连。本实验试样的表面形貌如图1所示,其均方根粗糙度仅为0.3 nm,说明试样准备情况良好,薄膜生长和淀积较均匀。由于后续实验为无损操作,因此样品可以重复使用。另外,氧化工艺和氮化硅薄膜淀积工艺是微电子工艺实验课程的主要内容[8-9],其工艺方法成熟。因此,本实验可作为微电子工艺实验课程的后续内容进行教学安排。学生在进行实验操作前,要了解浮栅存储器的工作原理和KFM测试原理。

图1 浮栅结构试样的表面形貌图

2.2 浮栅结构的电荷注入

在进行KFM测试前,需要对浮栅结构试样进行电荷注入操作。本实验利用KFM探针在原位进行电荷注入操作。在电荷注入过程中,探针工作在特殊的轻敲模式下,反馈控制设定为“TM Deflection”=1.0(通常反馈控制设定“AmplitudeSetpoint”选项),使探针振幅最小化并维持在排斥力区间[10]。同时,通过控制回路对导电探针施加-3 V偏压,线扫描速率为1 Hz,扫描范围为边长500nm的正方形区域。在电荷注入的操作过程中,学生可自主改变探针偏压的极性和大小、扫描速率和范围等参数,探究影响电荷注入特性的各种因素。

2.3 浮栅结构电荷存储的KFM测试

在电荷注入操作后,对试样进行KFM测试,研究其电荷存储情况。采用两步交错式扫描进行KFM测试[10]:第一步,在常规轻敲模式下,探测试样的表面形貌;第二步,如图2所示,探针在形貌扫描的基础上向上抬起一定距离d(本实验中d=50 nm),此时KFM反馈系统对探针施加一直流偏压VDC和交流电压VAC,其中VAC为调制信号(实验中调制频率设置为探针的固有频率,幅值设置为1 V),而VDC为反馈信号,反馈系统通过调节VDC使探针振动停止,最后输出VDC作为KFM信号。理论上,KFM信号等于探针与样品的接触电势差,由于导电探针为等势体,因此该信号反映了样品表面的电势分布信息[5-6]。通过测试浮栅结构试样的表面电势随时间的变化,就能够获知存储电荷随时间的变化情况。

图2 利用KFM研究浮栅结构电荷注入特性的测试示意图

3 结果与讨论

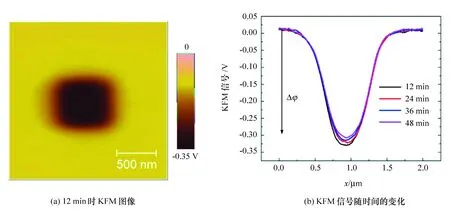

KFM测试时探针线扫描速率设定为1.5 Hz,因此每幅完整图像的扫描需要耗时12 min。图3(a)为浮栅结构试样在电荷注入操作后立即进行KFM测试的结果,图像中心区域为电荷注入区。结果显示,电荷注入区域的KFM信号降低,也即试样表面电势降低,这说明探针在-3 V偏压注入操作时向浮栅结构注入了电子。图3(b)为KFM图像信号(横截面)随时间的变化情况,从中可以获知:(1)电荷注入区域的KFM信号不随时间发生横向扩散,表明存储在氮化硅浮栅中的电荷并不发生横向的移动,这证明氮化硅介质具有横向绝缘的性质;(2)电荷注入区域的KFM信号强度随时间减弱,从12 min时的-0.328 V变为48 min时的-0.306 V,由于电荷横向扩散受限,因此KFM信号的变化表明存储电荷能够在纵向通过隧穿氧化层泄漏至衬底。这些特点与基于氮化硅浮栅的多晶硅/控制氧化层/氮化硅/隧穿氧化层/硅衬底(SONOS)存储器的设计理念和工作特点相吻合[11],验证了实验结果的可靠性。

图3 浮栅结构电荷注入后的KFM测试图像

为了进一步定量地研究电荷的存储特性,下面根据半导体器件物理知识建立KFM信号与存储电荷之间的定量关系。假设浮栅结构中注入的电荷均匀地分布在氮化硅层中,则存储电荷引起的表面电势变化Δφ(即KFM信号的变化量,见图3(b)中的标注)可以分解为浮栅分压Vf和衬底分压VS两部分,即

Δφ=Vf+Vs

(1)

浮栅分压可用平板电容公式计算[2,12]:

(2)

其中,σ为存储电荷面密度,dn和dox分别为氮化硅和氧化硅厚度,εn和εox分别为氮化硅和氧化硅介电常数。

硅衬底中的镜像电荷将产生额外的电压,这部分电压可采用静电场泊松方程描述如下[12-13]:

(3)

其中:σim=-σ,为衬底镜像电荷面密度;εSi为硅介电常数;β=q/kBT,为热电压倒数(q为单位电荷量,kB为玻尔兹曼常数,T为室温);np0和pp0分别为硅衬底中电子和空穴的平衡态载流子浓度(可根据衬底电阻率查表得知);LD=(εSi/qpp0β)1/2,为衬底载流子的德拜长度。式中负号和正号的确定与Vs的正负相关,当且仅当Vs<0时取负号,而当Vs>0时取正号。由此,式(1)—式(3)即建立了KFM信号与浮栅结构存储电荷之间的定量关系。

通过数值计算,可以获得Vf、Vs和Δφ随浮栅结构存储电荷面密度σ之间的定量关系,结果如图4所示,表明空穴存储(正电荷)将导致KFM信号的提升,而电子存储(负电荷)导致KFM信号的降低,并且具有一定的非线性关系。根据Δφ-σ曲线和图3(b),可查知试样在12 min时存储电荷面密度约为9.25×1011cm-2,而在48 min时减小为8.41×1011cm-2,即存储电荷数量衰减了约9.08%。作为探究性实验,学生可自主选择电荷注入时探针偏压及扫描速率等参数,研究不同条件下浮栅结构的电荷存储特性,锻炼学生的创新和实践能力。

图4 浮栅结构试样中存储电荷面密度与KFM信号之间的关系

4 结语

浮栅存储器作为一种可靠的非易失性存储器,在微电子领域应用广泛。本实验利用KFM显微探测技术,在微观尺度下展示了基于氮化硅材料的浮栅结构的电荷存储特性,通过观察KFM信号随时间的变化情况,推断出存储电荷不发生横向移动,但会通过隧穿氧化层发生纵向泄漏,这与氮化硅材料的存储特点相吻合。此外,根据半导体器件物理知识,通过求解静电场泊松方程,计算出了KFM信号与存储电荷面密度之间的定量关系,计算出的存储电荷面密度达到1011cm-2量级。学生可进一步改变电荷注入条件进行探究性实验,系统研究影响浮栅结构存储特性的因素。本实验有助于加深学生对浮栅存储器的理解,激发学生的学习兴趣,锻炼学生利用半导体理论知识解决实际问题的能力,具有良好的教学效果。