基于AD9854的信号源设计∗

2018-09-27王浩军

王浩军

(中国空空导弹研究院 洛阳 471009)

1 引言

在现代通信系统、电子对抗及各种电子测量技术中,一个高精度、频率可调的信号源是很多电子设备和系统实现高性能的关键。直接数字合成技术(Direct Digital Synthesis,DDS)将数字处理技术引入信号合成领域,单片集成的DDS产品是一种可代替锁相环的快速频率合成器件。由于DDS具有超宽的相对带宽,超高的捷变速度,超细的分辨率,以及相位的连续性,可以输出宽带的正交信号,可编程等优点,DDS技术得到了飞速发展。

2 DDS工作原理

2.1 DDS技术

DDS技术是根据奈奎斯特取样定律,从连续信号的相位ϕ出发,将一个正弦信号取样、编码、量化,形成一个正弦函数表,存在EPROM中。合成时,通过改变相位累加器的频率字来改变相位增量。相位增量的不同将导致一个周期内的取样点数的不同。在时钟频率即采样频率不变的情况下,通过相位的改变来实现频率的改变。

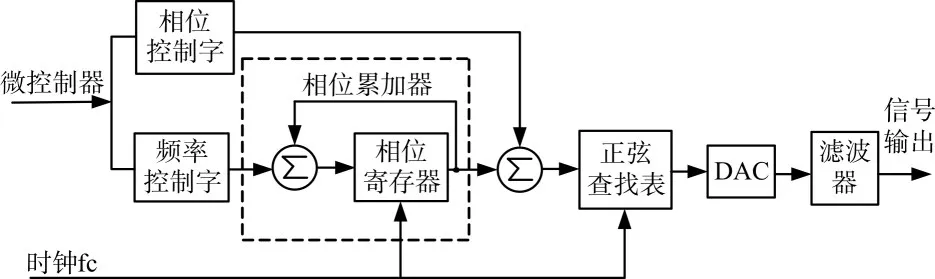

图1 DDS工作原理框图

图1是DDS的基本原理图。DDS系统的核心是相位累加器,它由一个N位的加法器和一个N位相位寄存器组成。每来一个时钟fc,相位寄存器以步长M增加,与频率控制字相加。相位寄存器的输出与相位控制字相加,然后输入到正弦查询表上。正弦查询表本身是一个存储器,用于存放以相位序列码为地址,该地址存放相位序列码所对应的幅度序列码。相位累加器的字长越大,存储量就越大。为了解决存储量问题,正弦查询表中只存储1∕4周期正弦波数字幅度信息,其余3∕4的数据量通过求补电路来完成。每个地址对应正弦波1∕4周期范围的一个相位点。数∕模转换器(DAC)将幅度序列码转换成阶梯波。滤波器将阶梯波转换为正弦波。时钟用来控制采样的时间间隔,DDS频率分辨力取决于相位累加器的字长和时钟频率。

2.2 AD9854芯片结构及工作模式

AD9854是美国AD公司采用先进的DDS工艺生产的一种高度集成芯片。它内部集成了48位频率累加器、48位相位累加器、正余弦波形表、两个12位高速、高性能正交DAC以及调制和控制电路,能够在单片上完成频率调制、相位调制、幅度调制和IQ正交调制等多种功能。当输入一个准确的参考频率,AD9854就产生一个高稳定的频率、相位、幅度可编程调制的正弦和余弦输出。AD9854的高速DDS内核具有48位频率分辨力,如果系统时钟为300MHz,则可分辨最小频率为1μHz。相位截断到17位保证了很好的无杂散动态范围(SFDR)指标。同时,AD9854内部含有可编程的4~20倍参考时钟乘法器电路,能够从一个很低的外部参考时钟频率产生一个内部的300M系统时钟,其内部时钟速度最大可达300MHz。直接的300M时钟也可以单端或差分输入。AD9854允许输出的最高频率为150MHz,而数字调制输出频率可达100MHz。

AD9854有五种可编程的工作模式,分别为Single-Tone(Mode 000)、FSK(Mode 001)、Ramped FSK(Mode 010)、Chirp(Mode 011)和 BPSK(Mode 100),模式选择可在控制寄存器里进行修改。这五种模式中,Single-Tone(单频)模式是最灵活的一种,也是主复位时被确定的默认模式。用户复位后的默认值设置芯片输出0Hz,0相位信号,在I、Q通道输出的是直流信号。当对频率寄存器编程时,输入频率控制字K后,芯片的输出信号从直流跃变到用户定义输出频率。频率控制字K与输出信号的关系为

式中,N为相位累加器的位数(本器件48位),fc为时钟频率。

通过该模式可以根据需要任意设定输出信号的频率、幅度和相位等特性。

第二种模式是无斜率FSK(模式001),输出的DDS频率是一个选择存放在频率寄存器1和2的频率控制字K的函数,输出取决于29脚逻辑电平的高低。第三种模式是斜率FSK(模式010),输出频率从F1到F2不是直接变化,而是通过扫频和斜率形成。第四种模式是脉冲调频(模式011),频率可以是线性或非线性变化输出。第五种模式是数字调相BPSK,

3 系统设计

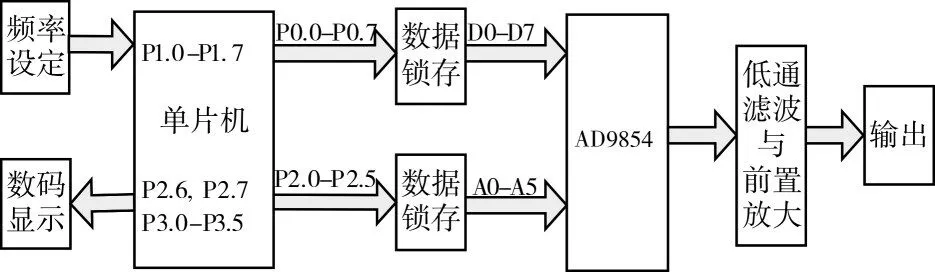

本文设计的信号源采用DDS技术,结合单片机控制,实现正弦波、方波、三角波、点频、扫频、跳频等功能。系统组成结构如图2所示,主要包括单片机控制模块、显示模块、数字合成模块、滤波与放大模块。

图2 系统组成框图

3.1 信号的产生及控制

系统采用的单片机是Atmel公司的AT89C51,它的19脚接外部20MHz晶振产生的时钟,同时也作为AD9854的输入时钟,再经过内部时钟乘法器15倍频得到300MHz的系统时钟。本设计采用AD9854的单频模式,将 S∕P SELECT(Pin 70)引脚接高电平,选择100MHz8位并行传输模式。AT89C51的P0.0至P0.7端口与AD9854的D0至D7端口相连传输数据信息,P2.0至P2.5端口端口与A0至A5端口相连传输寄存器地址信息,P3.6、P3.7分别与WR、RD两个引脚相连控制读写操作,由这三个部分共同组成并行传输控制。

3.2 输出频率、幅度与相位控制

AD9854内置一个地址范围为00H~27H的寄存器表,分成11组,有7组寄存器存放关于输出信号频率、幅度、相位的数据。寄存器表中00H,01H和02H,03H单元分别为相位寄存器1和相位寄存器2,存放14位的相位控制字1和相位控制字2。单频工作时,将14位相位控制字分2个时钟周期写入相位寄存器1,再更新脉冲,信号就以新的相位输出。

寄存器表中04H~09H和0AH~0FH单元分别为频率寄存器1和频率寄存器2,存放48位的频率控制字1和频率控制字2。单频工作时,将48位频率控制字分6个时钟周期写入频率寄存器1,再更新脉冲,信号就以新的频率输出。

寄存器表中21H,22H和23H,24H单元别为正弦幅度寄存器和余弦幅度寄存器,存放12位的幅度控制字1和幅度控制字2。单频工作时,将12位幅度控制字分2个时钟周期写入幅度寄存器1,再更新脉冲,信号就以新的幅度输出。

3.3 部分电路原理图

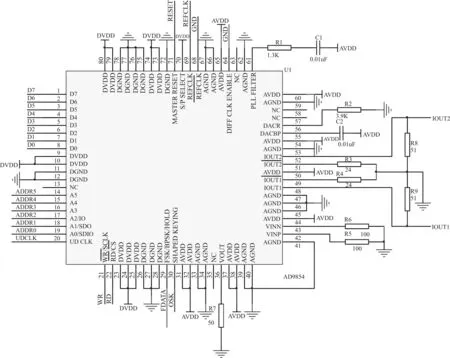

AD9854芯片的电路图如图3所示,模拟电和数字电分别供电,避免干扰。参考时钟采用单端输入,输出信号是两路正交输出。

由于DDS输出的时钟信号和元器件自身存在的噪声干扰,需要对DDS的输出信号进行低通滤波,截止频率120MHz,低通滤波器电路如图4所示。

图3 AD9854电路原理图

图4 低通滤波器电路原理图

4 结语

用AD9854实现DDS信号源,可以产生高精密的正弦波、三角波、方波,还能输出ASK、ASK、PSK等调制波型。能够更加突出DDS信号源的高频率分辨率、更快的频率转换速度(ns级)、输出频谱纯等特点,能够广泛地应用于雷达、通信等电子信息领域。