一种应用于2.4 GHz系统的F类功率放大器

2018-09-12周正轩黄瀚熙刘雁朋章国豪刘祖华

周正轩 黄瀚熙 刘雁朋 章国豪 刘祖华

摘 要: 基于0.5 μm GaAs PHEMT工艺,设计一款能应用于2.4 GHz ISM频段的WLAN 802.11b/g协议功率放大器。输出级采用负载线匹配的设计方法,并嵌入了对奇次谐波回收,偶次谐波抑制的网络,使之工作在F类,整机获得了较高附加效率。提出一种匹配计算方法与电路结构,兼顾输出功率和效率最大化,可对功率输出级进行优化匹配设计。该功放工作电压为5 V,仿真结果表明:在2.4 GHz频段内,1 dB压缩点时的输出功率为31.7 dBm,输出效率为51.8%,功率增益大于35 dB,对高阶偶次谐波抑制大于47 dB,对低阶奇次谐波进行了回收,获得了高效率。

关键词: PHEMT工艺; F类; 功率放大器; 负载线匹配; 谐波抑制; 功率增益

中图分类号: TN722.7+5?34 文献标识码: A 文章编号: 1004?373X(2018)18?0037?04

An F class power amplifier applied to 2.4 GHz system

ZHOU Zhengxuan, HUANG Hanxi, LIU Yanpeng, ZHANG Guohao, LIU Zuhua

(School of Information Engineering, Guangdong University of Technology, Guangzhou 510006, China)

Abstract: A power amplifier applying the 2.4 GHz ISM frequency band and WLAN 802.11b/g protocol is designed based on the 0.5 μm GaAs PHEMT technical process. For the output stage, the design method of load line matching is adopted, and the network with odd harmonics recycled and even harmonics suppressed is embedded so that the circuit can work in the F class, and the whole system can obtain relatively?high added efficiency. A matching calculation method and circuit structure is proposed. To make the output power and output efficiency maximum, optimization matching design is conducted for the power output stage. The working voltage of the power amplifier is 5 V. The simulation results show that in the 2.4 GHz frequency band, the output power of 1 dB compression point is 31.7 dBm, the output efficiency is 51.8%, the power gain is greater than 35 dB, the suppression of high?order even harmonics is greater than 47 dB, the low?order odd harmonics are recycled, and high efficiency is obtained.

Keywords: PHEMT technical process; F class; power amplifier; load line matching; harmonic suppression; power gain

射频功率放大器作为射频前端重要模块之一,其功能之一是把已调制信号无失真地放大到一定功率,能够让天线把信号发射到无线信道中。本文提出基于2.4 GHz ISM频段的一款能够应用于WLAN 802.11b/g协议的功率放大器。该功率放大器基于三安公司0.5 μm GaAs PHEMT工艺采用三级级联结构。第一级偏置状态为A类,静态电流为35 mA;二级偏置在AB类,静态电流为44 mA;第三级偏置在深AB类,静态电流为100 mA,第三级输出匹配电路采用F类匹配法;设计输出匹配,提高了整机的输出效率。依据仿真结果,输入反射系数S11小于-28.9 dB,小信号增益与功率增益大于35 dB,最高输出功率为31.7 dBm,饱和输出效率为51.8%。在输出端加入了谐波抑制匹配网络,对高次谐波有较好的抑制效果。

1 电路设计

1.1 功放设计思路

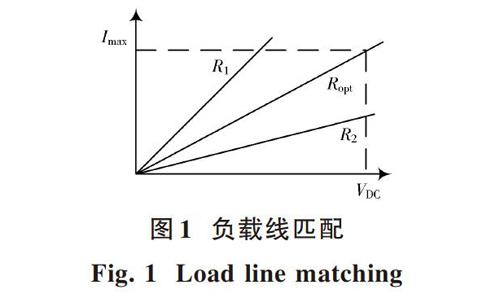

功率放大器相对于电压(V)放大器与电流(I)放大器首要不同之处在于:功率放大器的输出需要同时有足够大的电压摆幅和电流摆幅。由功率的计算公式[P=IV]可以得知电流与电压同时足够大才能获得大的功率。电压放大器与电流放大器只是强调了单项的电压与电流指标,它们的目的只是对输入的电压或电流信号进行放大;而功率放大器强调的目的是输出功率的大小,是要获得一定的功率值。换而言之,即使电压放大器与电流放大器输出信号的电压值或电流值足够大,快接近于电路直流源的极限,但输出功率却可能非常小。因此,在设计功率放大器时需要紧紧抓住输出电压与输出电流两项指标。为了获得晶体管的最大电压摆幅与电流摆幅,输出负载的确定非常关键。一般输出负载可以用负载线匹配方法获得[1]。负载线匹配法如图1所示。

假设晶体管漏源承受的最大电压为VDC,晶体管输出的最大电流为Imax,在负载为最优负载时有:

[VDC=ImaxRopt] (1)

当负载R1

1.2 匹配电路设计

本设计的功率放大器采用50 Ω匹配系统,输入匹配与级间匹配采用最佳功率匹配理论,即把下一级的输入阻抗匹配到本级输出阻抗的共轭阻抗,实现最大功率传输,使用单T型匹配网络匹配。功率放大器的重中之重是进行输出匹配。在现代实用的射频功率放大电路中,为了提高电路效率,通常最后一级工作在F类。F类的基本原理是对高阶偶次谐波的抑制与高阶奇次谐波的回收,也就是输出匹配网络对偶次谐波短路,对奇次谐波断路,从而达到对漏源电压VDS整形的目的。在理想条件下,F类功率放大器的效率[2?4]可以达到100%。理想的F类工作波形,在漏源有电流时,漏源电压VDS为零,在漏源电流为零时,漏源电压VDS为最大值,使漏源电压和电流错峰没有交叠,从而漏级无用功率耗散为零,有用信号功率全部输出给负载。理想的漏源电压VDS为方波:

[VDS=VDC-Vm1cos ω0t+n=3,5,7…∞Vmncos nω0t] (2)

漏源电流iDS表示为:

[iDS=I1+Imcos ω0t+n=2,4,6…∞Imncos nω0t] (3)

由漏源电压与电流关系可推导出,在漏源端观看输出匹配网络,基频阻抗:

[Z(ω0)=Ropt] (4)

观看到的直流阻抗与奇次谐波阻抗为:

[Z(nω0)=∞, n=0,3,5,…] (5)

观看到的偶次谐波阻抗为:

[Z(nω0)=0, n=2,4,6,…] (6)

考虑到硬件电路对高次谐波处理,使用集总参数器件搭建电路将非常复杂,使用的器件比较多,不便于集成。为了便于集成,且器件数不至于很多又能达到较好的效果,通常只对二次谐波短路,三次谐波开路。在漏级电流iDS中,二次谐波,与三次谐波的比重相对更高次谐波大,所以处理好二次,与三次谐波就可以获得相应比较好的电路性能。为了实现二次谐波短路,三次谐波开路,又能达到阻抗匹配目的的输出匹配电路如图3所示。

在此匹配电路中,C0为晶体的输出电容,其电容值的获取可通过工艺库模型获得,此电容为三次谐波并联谐振电路的容性阻抗部分。LC为输出级的扼流电感,其感抗大小通常为最优阻抗的11倍左右,也参与到输出匹配中。“201”虚线框为二次谐波短路结构,由L2与C2组成串联谐振电路,对二次谐波短路。“301”虚线框为三次谐波短路结构,由L3与C3组成串联谐振电路,对三次谐波短路。输出匹配网络工作在基频ω0时,由Z2看到的阻抗为最优阻抗Ropt,即Z2 = Ropt,在Z0处看到阻抗为50 Ω,也就是天线端的输入阻抗。工作在基频时的等效电路只需把图3中“201”和“301”看成电容,因为二次与三次谐振电路在基频ω0时等效为一个电容,二次短路结构在基频时等效为电容[Ceq2],三次短路结构在基频时等效为电容[Ceq3]。基频的等效电路匹配结构为2个L型低通匹配网络串联构成,可以适当地增加带宽,对高次谐波也起到了滤波衰减的功能。为了使功率放大器在工作频带内增益平稳,匹配电路对Z1有一定要求[5?8],即Z1满足:

[Z1Z0=Z2Z1] (7)

本设计电路[Z2=2.2 Ω],由式(7)计算出[Z1=10.5 Ω]。取匹配因子:

[M1=Z1Z0=0.21;M2=Z2Z1=0.21]

可得:

[C4=M1-1Z0ω0;L4=Z0M1-1ω0;Ceq3=M2-1Z1ω0;L1=Z1M2-1ω0]

输出匹配网络工作在二次谐波频率2[ω0]的情况下,二次谐波电流直接由“201”串连谐振电路短路到地,所以在漏源电压VDS中不含有二次谐波电压,达到了抑制二次谐波的效果,也不会对终端负载造成干扰,L2与C2满足关系式:

[2ω0=1L2C2] (8)

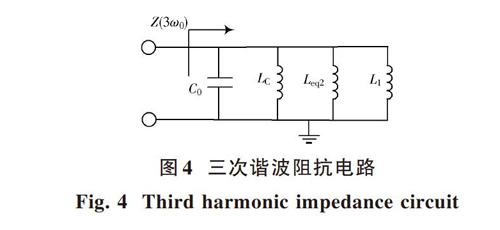

图4是输出匹配网络工作在三次谐波3[ω0]时的等效电路图,电路工作在三次谐波频率下,二次谐波谐振电路“201”在三次谐波频率3[ω0]等效为电感[Leq2],三次谐振电路“301”对三次谐波短路。要使等效电路对三次谐波开路,则需要电感L1,[Leq2],LC和输出电容C0共同组成并联谐振电路,理想的并联谐振电路阻抗为无穷大。由前文设计思路可以获得匹配电路电容电感的参数。在设计匹配电路时可以先定一个适当L2,由约束式可获得C2。电路工作在三次谐波时电抗为:

[3ω0Leq2=3ω0L2-13ω0C2] (9)

[13ω0C0=3ω0(Leq2//LC//L1)] (10)

三次諧振电路满足:

[3ω0=1L3C3] (11)

且有:

[1ω0Ceq3=ω0L3-1ω0C3] (12)

由以上约束条件可以计算出输出匹配电路的每一匹配原件参数。

1.3 功率放大器的实现

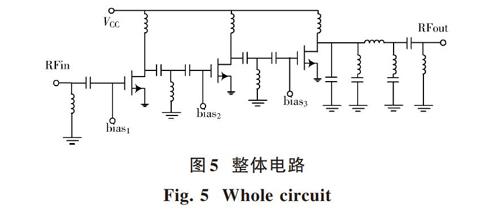

通过前文的原理分析与电路器件参数的计算,最终的电路如图5所示,输入匹配与级间匹配采用最大传输功率匹配方法[8]。

2 电路仿真结果

整体电路基于Agilent的电路设计软件ADS2015进行设计与仿真。图6是射频功率放大器输出级的漏源电压VDS与电流IDS的时域波形,可以看到漏源电压VDS类似于方波,在电压为最大时电流为零,在电压为最小时,电流为最大值。相对于传统功率放大器,漏源电压与电流的交叠面积降低明显,接近于理想的方波波形,提高了输出效率。

图7为功率放大器的小信号增益,由图可知在2.4~2.48 GHz时增益大于35 dB,对二次谐波与三次谐波波抑大于48 dB。图8为功率放大器输入功率与输出效率、输出功率和功率增益的关系图,在1 dB压缩点附近效率高达49.6%。图9为饱和输出功率与输入频率的关系图,在频带2.4~2.48 GHz内,输出饱和大于30 dBm。在2.4 GHz频带内饱和输出功率基本恒定。表1为性能参数对比表。

3 结 论

本文介绍了一种功率放大器的设计方法,重点分析了功放设计思路与输出级实现F类匹配的方法。同时兼顾了效率与线性度,从仿真结果来看达到了预期的效果,可以在2.4 GHz的通信系统中得到应用。

参考文献

[1] 池保勇,余志平,石秉学.CMOS射频集成电路分析与设计[M].北京:清华大学出版社,2006.

CHI Baoyong, YU Zhiping, SHI Bingxue. Analysis and design of CMOS RF integrated circuits [M]. Bejing: Tsinghua University Press, 2006.

[2] KANG D, YU D, MIN K, et al. A highly efficient and linear class?AB/F power amplifier for multimode operation [J]. IEEE transactions on microwave theory & techniques, 2008, 56(1): 77?87.

[3] CHEN K, PEROULIS D. Design of broadband highly efficient harmonic?tuned power amplifier using in?band continuous class?F?1/F mode transferring [J]. IEEE transactions on microwave theory & techniques, 2012, 60(12): 4107?4116.

[4] SESSOU K K, NEIHART N M. An integrated 700?1200?MHz class?F PA with tunable harmonic terminations in 0.13?μm CMOS [J]. IEEE transactions on microwave theory and techniques, 2015, 63(4): 1315?1323.

[5] YANG M, XIA J, GUO Y, et al. Highly efficient broadband continuous inverse class?F power amplifier design using modified elliptic low?pass filtering matching network [J]. IEEE transactions on microwave theory and techniques, 2016, 64(5): 1515?1525.

[6] ZHENG Yaohua, ZHANG Guohao, ZHENG Ruiqing, et al. Design of broadband class?F power amplifier for multiband LTE handsets applications [J]. Journal of semiconductors, 2015(8): 140?144.

[7] LIN Junming, ZHANG Guohao, ZHENG Yaohua, et al. Design of broadband class?F power amplifier with high?order harmonic suppression for S?band application [J]. Journal of semiconductors, 2015(12): 119?123.

[8] 黄亮,何全,章国豪.一种改善LTE应用功率放大器性能的设计[J].电子技术应用,2016,42(10):47?50.

HUANG Liang, HE Quan, ZHANG Guohao. A power amplifier performance enhancement design for LTE applications [J]. Application of electronic technique, 2016, 42(10): 47?50.

[9] KAZIMIERCZUK M K. RF power amplifiers [M]. Hoboken: John Wiley & Sons, 2008.

[10] JIN Y, HONG S. A 2.4?GHz CMOS common?gate combining power amplifier with load impedance adaptor [J]. IEEE microwave and wireless components letters, 2017, 27(9): 836?838.