基于STM32系统的ADC测试设计

2018-08-11叶敏意法半导体中国投资有限公司

叶敏 意法半导体中国投资有限公司

随着科技水平的提高,ARM内核的芯片,凭借强大的处理能力和极低的功耗,得到越来越广泛的应用。意法半导体的STM32系列微控制器是AR@Cortex@-M内核单片机市场和技术方面的领先者,目前提供12大产品线 (F0, F1, F2, F3, F4, F7, H7, L0, L1,L4, L4+,WB),超过800个型号。产品广泛应用于工业控制、消费电子、物联网、通讯设备、医疗服务、安防监控等应用领域,其优异的性能进一步推动了生活和产业智能化的发展。

本文以STM32H7为控制器为基础,具体阐述ADC测试系统及ADC误差种类。最后介绍了过采样技术及其原理,以及减少ADC测量误差的方法。

1.16位的STM32H7片内 ADC 概述

STM32H7微控制器自带的16 位 ADC 是逐次逼近型的模拟数字转换器。有通道数20个,2 个可以测量内部信号。各通道的A/D 转换模式类型有单次、连续、扫描或间断。有32位数据寄存器可以来存储 ADC 的转换结果。该单片机的 A/D 寄存器有状态寄存器、控制寄存器、采样时间寄存器、注入通道偏移寄存器、看门狗阈值寄存器、规则序列寄存器等。

2. 如何得到最佳的ADC精度

转换精度不是仅仅依赖于ADC模块的性能和功能,它与该模块周边应用环境的设计密切相关。

2.1 ADC误差的种类及相关的提高精度办法

2.1.1 ADC模块自身相关的误差

在STM32H7的数据手册中,给出了不同类型的ADC精度误差数值。通常,精度误差是以

LSB为单位表示。电压的分辨率与参考电压相关。电压误差是按照LSB的倍数计算:1 LSB = VREF+/216或VDDA/ 216

2.1.1.1 偏移误差

这是定义为从第一次实际的转换至第一次理想的转换之间的偏差。当ADC模块的数字输出从0变为1的时刻,发生了第一次转换。理想情况下,当模拟输入信号介于0.5 LSB至1.5 LSB表达的范围之内时,数字输出应该为1;即理想情况下,第一次转换应该发生在输入信号为0.5 LSB时。偏移误差以EO标注。

例子说明

对于STM32H7的ADC模块,最小的可检测到的电压增量变化,按LSB表示为:

1 LSB = VREF+/65536 (或对于没有VREF+管脚的产品:VDDA /65536)

如果 VREF+=3.3V,理想情况下输入7.63μV(0.5 LSB = 0.5 x 15.26μV)时,产生数字输出1。然而实际上,这时ADC模块的读数可能仍然为0。如果在输入电压达到8μV时,才能得到数字输出1,则:

偏移误差EO=实际的转换- 理想的转换

当输入的模拟电压大于0.5 LSB产生第一次的转换,则偏移误差是正值。

当输入的模拟电压小于0.5 LSB产生第一次的转换,则偏移误差是负值。

2.1.1.2 增益误差

增益误差定义为最后一次实际转换与最后一次理想转换之间的偏差。增益误差以EG标注。

最后一次实际转换是从FFFEh至FFFFh的变换。理想情况下,当模拟输入电压等于VREF+- 0.5LSB时产生从FFFEh至FFFFh的变换,因此对于VREF+ =3.3V的情况,最后一次理想转换应该在3.2999847V。

如果ADC数字输出为FFFFh时,VAIN< VREF+-0.5LSB,则增益误差为负值。

例子说明

增益误差EG=最后一次实际转换-最后一次理想转换

如果VREF+=3.3V并且VAIN=3.299935V时产生了从FFFEh至FFFFh 的变换,则:EG=3.299935 V - 3.2999847 V

如果在VAIN等于VREF+时不能得到满量程的读数(FFFFh)时,增益误差是正值,即需要一个大于VREF+的电压才能产生最后一次变换。

偏移和增益误差可以简单地使用ADC模块的自校准功能补偿。

除此之外,ADC模块自身相关的误差还有微分线性误差,积分线性误差等。

进行多次转换再做平均可以减小它们的影响。

2.1.2

与环境相关的ADC误差

2.1.2.1 电源噪声

模拟电源引脚是用于为转换提供参考电压,因为ADC输出是模拟信号电压和模拟参考电压之间的比例数值,因此任何模拟参考电源上的噪声都会使转换的数值产生变化。

例如:模拟参考电压为3.3V,输入信号为1V,则转换的结果是:(1/3.3) x 65535 = 4D93

如果在供电电源上有一个峰-峰为40mV的纹波,则当VREF+处于尖峰时,转换的结果变为:(1/3.34) x 65535 = 4CA5

通常开关式电源(SMPS)具有内部的快速开关功率晶体管,这会在输出上产生高频噪声,开关噪声的范围介于15kHz至1MHz之间。

2.1.2.2 消除模拟输入信号的噪声

平均值方法

平均值法是一个简单的技术,通过对一个模拟输入信号的多次采样和软件计算取平均值实现。这个技术有利于消除那些不频繁变化的模拟输入信号上的噪声。

平均值法需要在一个相同的模拟输入电压上进行多次采样,保证模拟输入信号在转换完成之前,保持在相同的电压,否则模拟输入的变化将会出现在结果数值中,从而引入新的误差。

增加一个外部滤波器

使用一个外部滤波器可以消除高频噪声,没有必要使用昂贵的滤波器去处理超出需要频率之外的频率分量。因此,一个相对简单的具有阻断频率fC,刚好超过需要频率的低通滤波器,可以有效地限制噪声和假波。采样速率超过最高的需要频率即可,通常为2~5倍于fC。

3. 过采样及测试结果

过采样技术即为提高采样率来提高数据精度,可以减少白噪声对采样结果的影响。STM32H7中的ADC模块自带过采样设计,适当配置寄存器后即可实现过采样。

3.1 过采样原理

3.1.1 量化噪声分析

ADC 采样过程其实是一个将连续的模拟信号量化成有限的数字的过程,每个数字代表一次采样所获得的信号。量化时,根据数据位把整个幅度划分为量化级,例如16位数据则表示216个量化级。把落入同一级的样本值归为一类,并给定一个量化值。由于模拟信号是连续的,量化结果和被实际模拟量的之间会有差值,该差值就是量化误差(eq),也称为量化噪声。

根据参考电压(Vref)和量化的数字的位数(N),能够确定的最小分辨率:

N越大,△就越小,量化误差也就越小。在没有其它能造成误差的因素如参考电压的变化的理想情况下,量化误差应该在±0.5△之内。

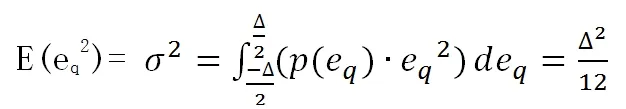

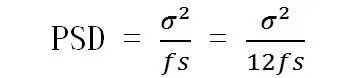

假设量化噪声是白噪声,则可通过计算量化误差的方差来得到平均噪声功率:

假设采样频率为fs,将量化噪声看成一个总功率为常数,平均分布在0~fs频带内,可以算出量化噪声的功率密度:

可以看出,采样频率越高,量化噪声影响越小。

3.1.2 过采样数据的计算

通过4p的过采样率得来的采样值再通过求和运算、平均计算等方法进行处理,但是却不能简单的把4p的采样值进行简单的加法和除法的运算,这种运算方法的滤波作用很低,比如R位的采样值通过精度的平均后仍然是R位,并不能提高过采样的精度。在进行过采样数据的提取时可以将4p个采样数据值进行相加得到R+2p位的数值,通过数值右移p个单位,就能够得到R+P位的数值,此时的数字是提高了p位后精度的采样最后结果。

3.1.3 过采样能够进行的前提

过采样技术并不是在任何情况下都能很好地发挥作用的,如果要使用过采样来增加采样精度,必须满下面两个条件:

(1)控制器输入的信号必须存在一些白噪音,而功率的平均分配要在采样技术有用的频率带内。

(2)噪声的幅度必须能够对输入信号产生足够大的影响。如果不能则输入的信号转出的值就会相同,这样的抽取结果不能提高过采样的数据精度。

3.2 测试方法

在由意法半导体设计生产的STM32H7微控制器Discovery开发板上,将PA0管脚连接1.25v外部输入,参考电压Vref接到2.5V稳压电源。测试环境满足过采样技术的使用条件。

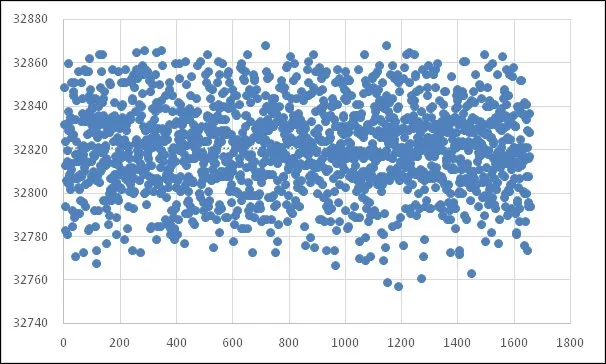

原始数据采样:通过1654次ADC连续采样PA0管脚的电压值,做出数据统计。

过采样数据收集:通过1654次ADC连续过采样采集PA0管脚的电压值。

STM32H7微控制器芯片内部ADC模块需配置CFGR2寄存器的ROVSE位置为1,使能过采样。将CFGR2寄存器的OSR位(过采样率)配置为1024x,OVSS(采样右移值)为6bit右移。

3.3 测试结果

3.3.1 原始采样值分布(1654次连续采样)

采样最大值-采样最小值 = 32868-32757 = 111

3.3.2 过采样求平均后结果

处理后结果最大值-处理后结果最小值= 4

4. 结论

本文通过对STM32H7微控制器ADC模块的介绍,ADC测量误差的种类分析,以及过采样技术的深入剖析,分析了ADC采样系统设计的原理以及提高采样精度的方法。通过过采样技术,大大减少了白噪声对采样结果的影响, 提高了ADC的采样精度。