基于FPGA的机载应答机数字DMTL设计

2018-08-07四川九洲空管科技有限责任公司夏喜龙祝正燕

四川九洲空管科技有限责任公司 夏喜龙 祝正燕

0 引言

机载应答机(“Airborne Transponder”)的译码性能对机载应答机系统性能有着重要的影响,机载应答机译码一般有两部分组成:DMTL(Dynamic Minimum Trigger Level)模块和模式译码模块。DMTL模块接收来自接收机的对数视频信息,经旁瓣处理、门限处理后生成PSV信号及幅度指示信号至译码模块;译码模块依据PSV、幅度指示信号解析出询问模式,并选择相应的应答天线送至应答编码模块。

DMTL特性对于机载应答机的旁瓣特性、多径询问下的应答性能及高密度询问下的性能有着重要的影响,对于提升应答机的译码性能具有重要的意义。目前应答机视频处理比较成熟的电路为模拟式电路,由于该电路采用全模拟电路设计,设计采用了固定延迟线、恒流源、放大器,比较器,定时器等模拟器件,并配有相当数量的电阻、电容,为调谐参数,配备了较多了可调电阻[1]。

数字电路较模拟电路在可靠性、抗干扰性方面有着先天的优势,且随着高速A/D采样技术、FPGA技术的发展,采用数字DMTL成为可能,因此,设计数字DMTL是必要且可实施的。

1 技术需求

按照ICAO附件10[2]及DO-181E[3]中对机载应答机的要求,机载应答机具有的以下性能应通过DMTL实现[4]。

1.1 旁瓣处理

P2>P1脉冲幅值时,90%被抑制(灵敏度电平之上3dB~50dB);

P1>P2+9dB脉冲幅值时,90%应回答(灵敏度电平之上3dB~50dB)。

1.2 回波抑制和恢复

应答器的设计必须包含回波抑制装置,以保证当空间信号出现回波时还可能正常运行。

1.2.1 灵敏度降低

在接收任何持续时间超过0.7微秒的脉冲时,应答机应提高接收机的阈值。阈值位于使灵敏度降低的脉冲电平和该电平-9dB之间的范围内,除非在接收到使灵敏度降低的那个脉冲之后的第1微秒期间内出现过冲。

1.2.2 恢复

灵敏度降低之后,接收机会在接收到降低灵敏度的脉冲后沿之后将其灵敏度恢复到MTL的3dB范围以内,其恢复平均速度不超过4.0dB/us。

1.3 应答率限度控制

为保护系统免受应答器过荷询问效应的影响,当已达到预定应答率时防止对较弱信号的应答,在设备中必须带有降低灵敏度式应答限度控制。

2 实施方案

如图1所示,数字DMTL分下通道(bot)和上通道(top)两个通道,分别为DDMTL单元的两个例化,幅度指示信号(ant_sel_ind)通过比较上下通道的天线选择(ant_sel_amp_level)生成,当下通道强时,输出为低;否则为高。

图1 FPGA软件功能框图

单个通道DDMTL单元如图2所示,模拟视频输入信号经A/D量化后进入FPGA,FPGA完成DMTL的控制,基本工作过程如下:

a)来自接收机的模拟视频输入一路进行延迟后输出至比较电路,另一路经6dB衰减后进入信号保持衰单元;

b)信号保持衰减单元一路输出至比较电路,另一路去往通道比较。信号保持衰减单元保持衰减特性受3us保持、自动过载(AOC)控制、灵敏度(MTL)控制单元的控制。

图2 单个通道DMTL功能框图

3 测试验证

3.1 软件仿真结果

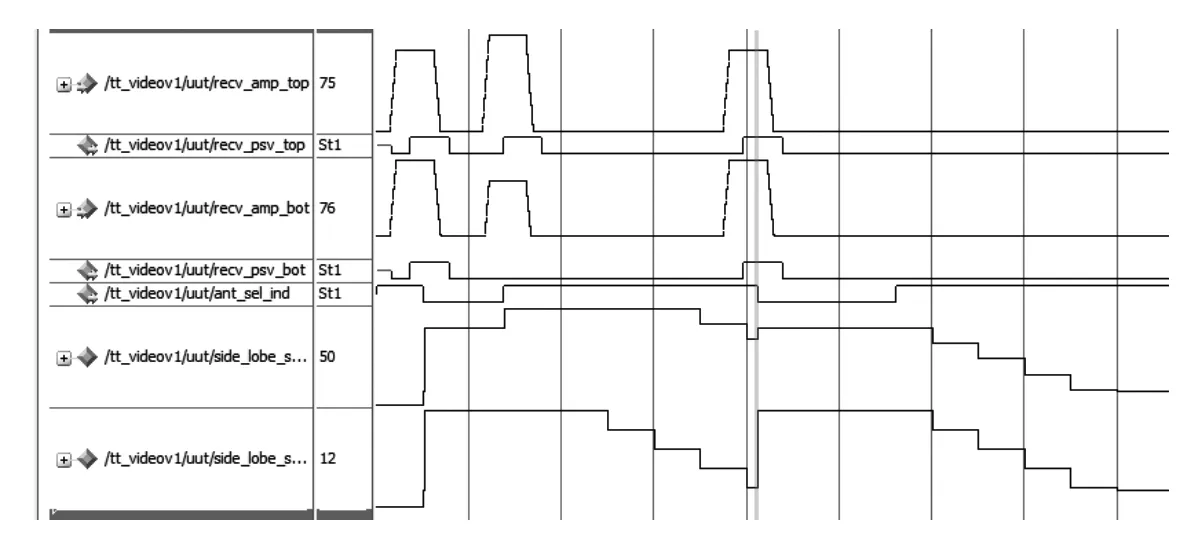

通过modelsim对数字DMTL进行了仿真,结果如图3所示,通过仿真可以看出:

a)P2>P1脉冲幅值时,未生成PSV,P1>P2+9dB脉冲幅值时,生成PSV旁瓣处理正确(按照接收机对数特性,1db对应数值为3);

b)当收到大于0.7us的脉冲后,灵敏度下降至当前脉冲幅度-6dB,4us后以4.0dB/us的速率下降;

c)当下通道信号强时,ant_sel_ind信号为并保持3us左右。

图3 FPGA软件仿真特性

3.2 系统测试

依托于JZ/YD126XD机载应答机进行了系统测试及空中试验,测试方法参见参考文献4。测试表明,与视频处理相关的特性旁瓣抑制特性、灵敏度降低与恢复特性、AOC特性、天线分集特性均满足系统要求。

4 结语

数字DMTL单元硬件平台采用A/D及FPGA,DMTL控制通过FPGA软件实现。通过仿真测试、系统测试表明:数字DMTL单元达到相关标准的技术要求,较传统模拟方式,该设计可靠性、经济型、尺寸重量等指标均具有较大的优势。该设计也可进一步推广至中频/射频数字化应答机设计中,具有较好的推广应用价值。