一种1Hz~1GHz时钟产生电路

2018-07-27赵金鹏

赵金鹏

(中国电子科技集团公司第四十一研究所,山东青岛,266555)

0 引言

随着自动测试技术的发展,对时钟信号的要求越来越高,主要体现在:第一,要求时钟频率范围宽,低频段频率相比以往更低,而高频段频率相比以往更高;第二,要求时钟的分辨率高,能以很小的频率分辨率实现对时钟频率的灵活设置;第三,对时钟的信号质量要求高,包括相位噪声、频率稳定度等。针对这些新的需求,中国电科41所研制了PXI/PXIe总线定时与同步时钟模块系列,并在研制的过程中,设计了一种频率覆盖1Hz~1GHz、频率分辨率达到μHz级的时钟产生电路。

1 时钟产生电路的总体方案

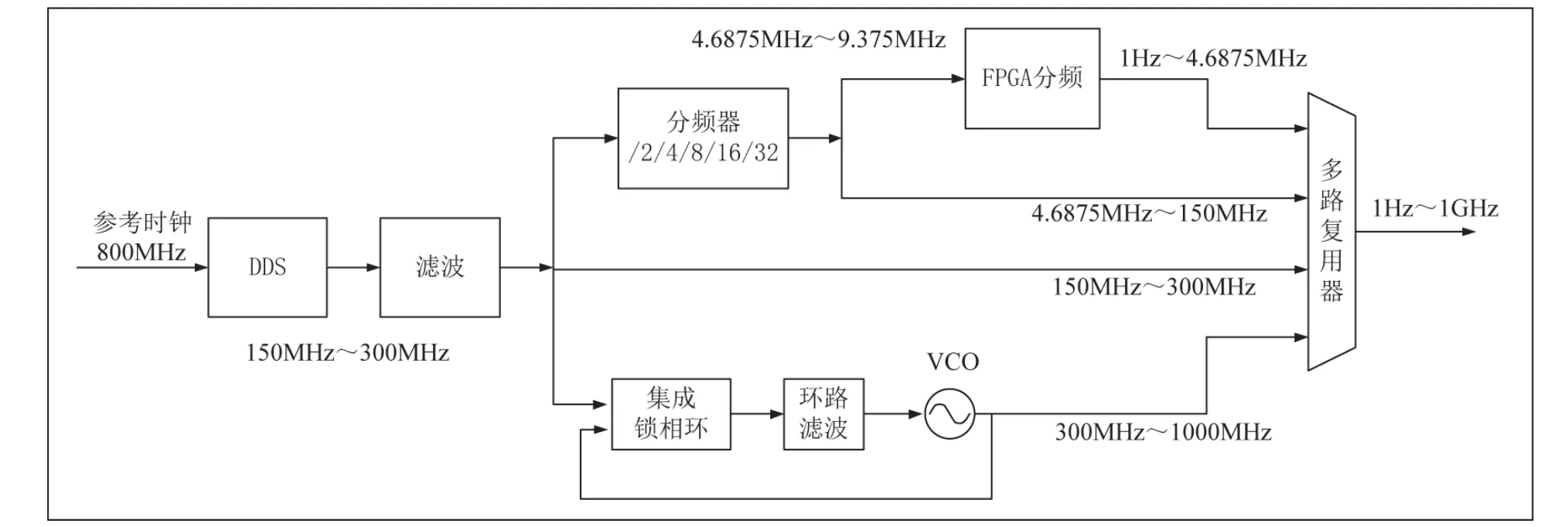

时钟产生电路总体方案如图1所示。将1Hz~1GHz整个频段划分为4个频段:1Hz~4.6875MH、4.6875MHz~150MHz、150MHz~300MHz 和 300MHz~1GHz,根据每一频段的特点,分别采用不同的方法产生时钟信号,最后利用多路复用器进行合路输出。

其中,150MHz~300MHz 是最为关键的频段,这一频段的信号利用DDS(直接数字频率合成器)直接产生,其余各频段的信号都是在这一频段信号的基础上产生。DDS采用频率为800MHz的高质量信号作为参考时钟,其输出会经过带通滤波器进行滤波,以消除DDS产生的无关杂散信号的影响。

图1 时钟产生电路总体方案示意图

在上述基础上,将一路150MHz~300MHz的信号通过分频器进行2/4/8/16/32次分频,得到4.6875MHz~150MHz的信号;其中一路4.6875MHz~9.375MHz的信号利用FPGA进行分频,得到1Hz~4.6875MHz的信号;将一路DDS产生的150MHz~300MHz的信号作为参考信号,组成锁相环,利用压控振荡器(VCO)产生300MHz~1GHz的信号。四路信号根据需要,通过多路复用器进行选择,实现1Hz~1GHz的定时同步时钟信号。

2 DDS参考时钟电路设计

如上所述,150MHz~300MHz这一频段是全频段信号产生的基础,这一频段信号的质量决定着全频段信号的质量,而DDS参考时钟的信号质量又决定着本频段信号的质量。所以,DDS参考信号的产生便是需要着重解决的第一个问题。

图2 参考时钟产生原理示意图

DDS参考时钟频率选择为800MHz,利用锁相环产生。该锁相利用具有超低相噪和高频率稳定度的10MHz恒温晶振输出或外部10MHz信号作为频率参考,为最终时钟信号的高质量奠定了基础。频率合成器选择ADI公司的ADF4002,带宽为400MHz,使用简单方便,只需要对初始化、功能、R分频、N分频四个24位的寄存器写数,便可实现相应的控制,具体操作过程在此不做过多赘述。压控振荡器(VCO)选择Synergy公司的HFSO800-5L,这是一款具有超低相位噪声的800MHz点频VCO,其在10kHz频偏处的相位噪声达到了-142dBc/Hz。

3 DDS电路设计

DDS(直接数字频率合成器)选用ADI公司的AD9912,其内部时钟频率高达1GSPs,集成了14位的DAC,最高能够输出400MHz的信号,它具有48位的频率控制字,频率分辨率达到了μHz,完全可以满足本文时钟频率产生电路的需要。

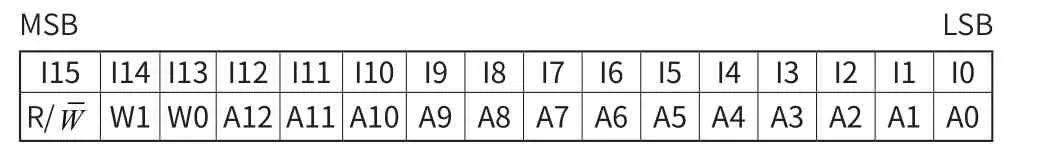

图3所示是DDS部分的电路,800MHz的参考信号以差分形式提供给AD9912。DDS的输出经过巴伦、带通滤波器后提供给其他各路或经多路复用器输出。AD9912 可通过串行 I/O 端口设置其内部控制寄存器的内容,其串行控制指令字如表1所示。

表1 AD9912串行控制指令字

本文所述时钟产生电路只利用AD9912产生150MHz~300MHz的信号,不涉及更为复杂的调制功能,对寄存器的操作相对较为简单,只需以下三步即可:

图4 DDS输出端带通滤波器

第一步,通过对0x0010寄存群器的写数,对AD9912的输出、系统时钟倍频锁相环等进行使能、掉电的管理,本文所述时钟产生电路写入0x10即可。

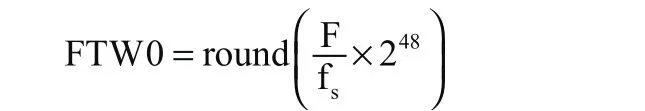

第二步,通过对0x01A6~0x01AB寄存器的写数,写入48位的频率控制字FTW0,

其中,F是期望DDS输出的信号频率,fs是DDS参考时钟的频率,在本文所述电路中,fs= 800MHz 。

第三步,对0x0005寄存器写入0x01,实现update功能,使前面两步操作生效。

为了滤除杂散,DDS的DAC OUT输出端是必须要加低通或带通滤波器的,本文为了更好的滤除杂散,选择使用带通滤波器,在ADS仿真的基础上设计了如图4所示的带通滤波器。

4 高频段锁相环设计

对于高频段即300MHz~1GHz部分,采用了锁相环来实现,如图5所示。该锁相环用DDS输出的150MHz~300MHz信号作为参考信号,频率合成芯片选用ADI公司的ADF4106,具有6.0GHz的带宽,使用方法与ADF4002类似,VCO(压控振荡器)选用Synergy公司的DCMO110250-8,频率范围覆盖1.1GHz~2.5GHz。

锁相环产生的信号经过分频器后输出。通过控制分频器的分频比,将锁相环产生的1.2GHz~2.4GHz信号进行4分频便得到了300MHz~600MHz的信号,将锁相环产生1.2GHz~2.0GHz信号进行2分频便得了600MHz~1GHz的信号。

5 测试结果

本文用分频段分别处理的方法,实现了1Hz~1GHz时钟信号的产生。在150MHz~300MHz这一中心频段,时钟信号的频率分辨率达到了2.84217uHz。50MHz的时钟信号相位噪声(10kHz频偏)达到了-131dBc/Hz,1GHz的时钟信号相位噪声(10kHz频偏)达到了-107dBc/Hz,大大优于-125dBc/Hz和-95dBc/Hz的设计要求。

图6 时钟产生电路输出信号相位噪声测试(10kHz频偏)