一种基于光纤数据传输实现的多板卡脉冲同步技术

2018-07-12袁子乔陈尹翔

刘 翔 袁子乔 杜 力 陈尹翔

(西安电子工程研究所 西安 710100)

0 引言

数字相控阵雷达大量的数字T/R组件在工作时必须同步发射或接收信号[1],任何一个组件的不同步都会造成数字T/R组件间的幅相不一致,影响波束形成的方向图,造成系统的不稳定性。传统相控阵雷达使用等长屏蔽同轴电缆来传输同步触发信号[2],但在强电磁环境中屏蔽层和接头处的微小瑕疵将降低屏蔽性能,影响触发信号的传输,造成触发信号的不同步; 继而通过改进,使用等长差分电缆作为同步触发信号的传输介质,差分电缆能有效抵抗电磁干扰,但增加了设备的连接电缆数量,增大了设备生产和调试难度,并且随电缆长度增加将导致触发沿的变化变缓,从而影响触发信号的同步性[3]。

目前还有一种传输同步脉冲的方法,利用光端机传输基准时钟和同步脉冲信号,利用光电转换,将时钟和同步脉冲信号功分至多块数字接收板卡,再利用时钟锁存同步脉冲,实现同步脉冲的传递。此方法存在的问题是成本高,需要由额外的光端机完成此功能;恢复的同步脉冲不稳定,由于光端机光电转换后,恢复脉冲采用的都是模拟电路,因此随环境,板卡批次的不同,恢复出来的脉冲不稳定性增加,经常返工维修,增加了调试时间。

本文介绍了一种基于光纤数据传输实现的多板卡脉冲同步技术,多块数字接收板通过光纤对接光纤处理板,光纤处理板上传控制指令至数字接收板,数字接收板把雷达回波信号预处理后,将处理数据传至光纤处理板;光纤处理板产生基准同步脉冲,通过发送控制指令,在控制指令中增加一些特殊字符,当数字接收板收到特殊字符后,恢复出脉冲信号,由于所有板卡光纤延时基本等长,因此各个板卡恢复出的脉冲信号为同一时刻,控制前端所有TR组件收发均为同一时刻,满足系统的时序要求。

1 多板卡脉冲同步技术系统设计

图1为多板卡脉冲同步技术的实现框图。在雷达信号处理前端设计中,由多块数字接收板和1块光纤处理板组成,数字接收板对接收的中频回波信号进行AD采样、数字下变频、通道校正、脉冲压缩处理,将处理后的数据通过光纤下传至光纤处理板,在光纤处理板中完成数字波束形成、目标检测、数据处理等功能[4]。

多板卡脉冲同步技术的系统设计基于原有工程架构,在实现雷达功能的前提下,增加脉冲同步功能。光纤处理板产生基准同步脉冲,通过发送控制指令到多块数字接收板,在控制指令中增加一些特殊字符,当数字接收板收到特殊字符后,恢复出脉冲信号,由于所有板卡光纤延时基本等长,因此各个板卡恢复出的脉冲信号为同一时刻,控制前端所有T/R组件收发均为同一时刻,满足系统的时序要求。

图1 多板卡脉冲同步技术的实现框图

2 多板卡脉冲同步技术实现过程

2.1 RocketIO简介

RocketIO是Xilinx在Virtex2 pro以上系列中集成的专用高速串行数据收发模块。可用于实现吉比特的数据传输,适用于多种高速数据传输协议,串行传输速度在600Mbps-10Gbps以上,可选8B/10B编解码。

Xilinx FPGA RocketIO收发器原理框图如图2所示,主要由PMA物理媒介层和PCS物理编码层构成,其中PMA主要包括串行器和解串器、发送和接收缓冲区、时钟生成电路、时钟恢复电路;PCS主要包括8B/10B编解码、弹性缓冲器、周期冗余检测CRC。

发送数据的原理为,发送端根据一定的算法生成的CRC校验码插入到预发送的并行数据中,数据经过8B/10B编码,写入发送端数据缓存FIFO,转换成差分数据发送出去。

接收端接收到串行差分数据后写入接收缓冲器,进行串并转换,输出的并行数据经过8B/10B解码,依据需要用弹性缓冲器实现通道绑定和时钟修正,经过CRC模块校验后并行输出。

2.2 多板卡脉冲同步技术实现

下面详细介绍多板卡脉冲同步技术的实现过程。

本文以多块数字接收板、1块光纤处理板为例。数字接收板上包含一块Xilinx FPGA和1路光纤收发模块;光纤处理板上的主要器件为一片Xilinx FPGA和多路光纤收发模块;多块数字接收板与光纤处理板之间通过光纤互连,光纤处理板通过光纤上传控制信息至数字接收板,数字接收板对雷达回波进行预处理,将处理后的数据发送至光纤处理板。

步骤一:

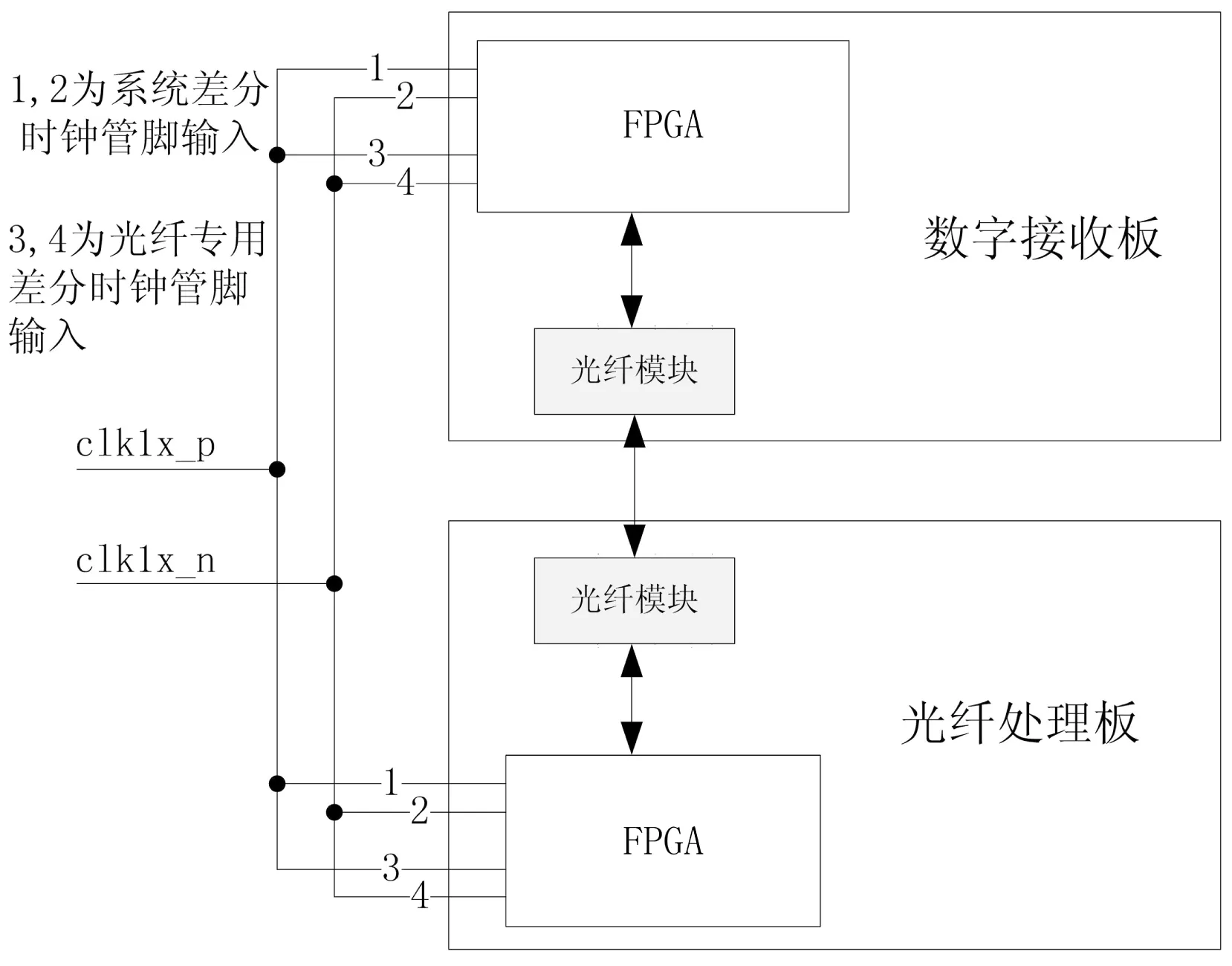

图3中,光纤处理板和数字接收板卡都有差分基准时钟clk1x_p,clk1x_n输入,在数字接收板卡上,差分基准时钟clk1x_p,clk1x_n接入FPGA的时钟管脚1,2,同时接入到FPGA光纤专用时钟管脚3,4;光纤处理板时钟的接法与数字接收板相同;在光纤处理板上产生基准时序,在基准时序的时刻下,光纤处理板多根光纤同时向多块数字接收板发送控制信息,控制信息中包含一定的特殊字符。

图2 FPGA GTX收发器原理框图

图3 多板卡脉冲同步技术时钟管脚连接关系图

步骤二:

如图4所示,FPGA光纤收发数的时候,光纤收发模块的参考时钟为clk1x,配置RocketIO IP核,使光纤传输速率为clk4x·20bit,即光纤收发数的用户时钟为clk4x,是参考时钟clk1x的四倍,数据位宽为20bit;当数字接收板收到控制信息后,缓存后进行使用,收到特殊字符时,恢复出时序脉冲,此脉冲是以clk4x为同步时钟,脉冲宽度大于一个clk1x时钟节拍即可。

步骤三:

在数字接收板恢复出的同步脉冲,由于Xilinx光纤收发数据的过程中,在GTX的硬核中会有tx_buffer缓存、rx_buffer缓存、8B/10B编码、10B/8B编码的影响,会使恢复出来的脉冲在单次上电时,位置是固定的,但不同次上电时,有一到两个clk4x时钟节拍的抖动,恢复出来的脉冲位置可能为位置1,位置2,位置3,位置4,如图4中所示;此时利用clk1x和clk4x时钟4倍频率的关系,调整恢复出来的同步脉冲前沿对准clk1x的下降沿,即位置3,这样即使恢复的同步脉冲有一到两个clk4x时钟节拍的抖动,利用clk1x时钟的上升沿锁存恢复的同步脉冲,此时同步脉冲也会稳定下来,且多块板卡恢复出来的同步脉冲位置相同,在多次上电过程中,位置稳定不变。

步骤四:

整个系统上行光纤均为等长设计,且光纤处理板在同时刻向多块数字接收板发送控制信息,利用clk1x和clk4x的4倍时钟频率关系,可以保证每个数字接收板卡恢复出来的脉冲的位置固定,且多次上电恢复出来的脉冲也是稳定的,系统时序同步问题得到解决。

图4 多板卡脉冲同步技术的时序图

3 结束语

本文介绍了一种基于光纤数据传输实现的多板卡脉冲同步技术,多块数字接收板接收同步时序控制前端T/R组件同步发射或接收信号,数字接收板与光纤处理板通过光纤互联,光纤处理板产生基准同步脉冲,通过发送控制指令,在控制指令中增加一些特殊字符,当数字接收板收到特殊字符后,恢复出脉冲信号,由于所有板卡光纤延时基本等长,因此各个板卡恢复出的脉冲信号为同一时刻,控制前端所有T/R组件收发均为同一时刻,满足系统的时序要求。