用于视频传输的10G网络接口设计

2018-07-03赵柏山王禹衡刘佳琪

赵柏山,王禹衡,刘佳琪

(沈阳工业大学信息科学与工程学院,沈阳110870)

1 引言

面对日益增多的数据和多媒体服务,以太网的大容量、高速率、多功能模块能够很好地满足市场要求[1]。随着网络技术的发展,绝大部分信息要通过互联网进行传输,人们对于网络的要求会更高,比如设备处理速度、传输速度、数据的还原度等。以太网已经在通信、控制、传输领域得到了广泛应用。经过十几年发展,10G以太网技术日渐成熟,成本也随之降低。传统的基于视频压缩的传输方案,虽然节省带宽,但也增加了系统设计复杂度并且会产生传输延迟,不能满足实时性的要求。采用万兆以太网传输将会跳过视频压缩的处理,直接将摄像头捕捉到的信号进行传输,这样可降低系统处理延迟,提高处理速度,保证了视频的实时性。

基于FPGA网络的应用,包含传输层协议、网络层协议、网络接口层协议(MAC协议)[2]。MAC控制器作为以太网核心部分之一,主要以两种形式存在,一种是将物理层MAC层集成为以太网卡芯片,另一种是MAC控制器独立存在IP核。10G以太网卡产品层出不穷,2012年,Intel公司推出了基于多模光纤传输介质的万兆以太网卡Intel X520-SRI以及基于RJ45传输的IntelX540-T2[3],这些网卡的价钱很高,达到了上千元。用FPGA实现MAC协议可以在很大程度上降低成本。

2 系统整体设计

在千兆以太网中,MAC层工作在125MHz、8bit位宽中;在万兆以太网中,MAC层工作在156.25MHz、64bit位宽。协议规定只适用于全双工模式,MAC层不使用CSMA/CD协议[4],也就是说一个时钟周期可以处理8字节数据,帧尾有效字节长度不等,在CRC校验中会产生新的问题。为解决这类问题,以IEEE802.3ae定义了新的介质无关接口:10G介质无关接口 (10 Gigbbit Media Independent Interface,XGMII)[5],同时对此接口进行设计,使物理层模块实现与FPGA的互连。

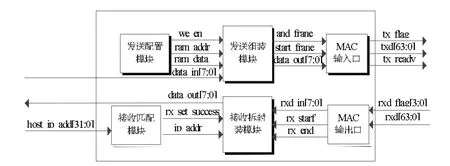

本文主要是对视频数据封装和解封装进行设计。如图1是以太网视频传输整体原理框图,视频采集模块FPGA通过I2C总线对摄像头内部寄存器进行配置,满足该摄像头工作状态,将采集视频数据写入SDRAM中进行数据缓存,选用的方法为乒乓操作[6]。当系统配置模块配置好数据后,使能SDRAM读信号,将缓存信号发送至UDP/IP模块。这个过程主要是对视频信号的采集,此后数据信号依次经过UDP/IP模块、MAC控制器模块,将数据流按照各层的协议打包成以太网帧格式,最后通过XGMII接口将数据发送至PHY光模块接口,完成整个发送过程。

图1 系统整体设计

3 UDP/IP协议栈设计

UDP/IP协议栈设计最主要是用来完成UDP头部和IP头部的封装和解封装。选择UDP协议(User Datagram Protocol),是因为它是非链接的协议,与TCP/IP[7]处理数据包的方式相比,此方案中的数据源端和终端不建立连接,这简化了该模块设计。摄像头捕捉到的视频数据经过视频编码器形成二进制数据码,作为数据部分,当有数据进入UDP/IP模块,会按照顺序依次将UDP/IP头部封装好,然后紧接着发送视频数据,将封装好的数据发送到数据链路层,交给MAC控制器,完成以太网帧的封装。UPD/IP协议栈结构如图2所示。

图2 UPD/IP 协议栈结构设计图

如图所示,其工作流程是:上层所发送的视频数据,经由此协议栈封装成所规定的数据帧格式,发送到MAC控制器模块;当从物理层接收到数据时,会根据MAC和IP地址与本设备的匹配及头部的校验,来判断是否正确,再对数据帧进行解封装操作;最后UDP/IP协议栈输出的数据为视频数据。整个过程可在设计上分为发送模块和接收模块,各个模块功能详述如下:

(1)发送模块

发送配置模块是把目的IP地址,源IP地址,目的MAC地址,源MAC地址的值输入到该模块,以一个字节的周期进行数据读取,将数据发送到帧组装模块;发送组装模块也是整个UDP/IP协议栈设计中最重要的部分,虽然发送配置模块包含了大部分数据,但是例如IP总长度、首部校验和数据报长度,这些数据需要在组装模块完成,并同时产生控制信号、数据帧开始和结束的标志位;配置好的数据将被发送到MAC数据接口模块,MAC数据接口模块会把8位数据转换成64位数据发送到MAC控制器,同时还产生有效数据。数据经过发送模块后所要形成的帧头存储数据如表1。

(2)接收模块

接收模块的工作流程是,从MAC层接收数据,经MAC数据接口模块把64位数据转换成8位数据,再通过数据解封装模块,把数据帧IP/UDP头部去除,把视频数据发送给用户层进行显示。此过程需要通过对数据进行匹配,匹配成功准确无误后才能发送数据。协议栈整体传输位宽为8bit,本研究中所设计的为万兆以太网,故此在MAC层数据,所设计位宽为64位,时钟为156.25MHz,需要另外设计一个接口缓冲模块(MAC接口模块),以满足发送和接收所需要的位宽,使MAC控制器和协议栈之间实现链接。这样处理增强了灵活性,整个设计是运用硬件描述语言来设计,与运用软件的方式相比,处理速度更快。对于UDP/IP整个发送的帧结构及内部所存储的数据,运用Quartus II软件IP核设计RAM存储器,对数据进行实时读写,这样可以节省版子的资源,也能节省占用FPGA逻辑资源。

表1 UDP/IP帧头数据存储情况

4 MAC控制器设计

协议规定万兆以太网使用的是全双工模式[8],因此MAC层不使用千兆CSMA/CD协议半双工模式,这样相对来说简化了MAC控制器设计[9]。相比千兆以太网使用的8位数据宽、125MHz进行传输,万兆以太网使用了156.25MHz和64位宽进行传输,这就产生了许多新的问题。CRC校验模块设计由8bit并行输入产生的32bit的校验码,变成由64bit并行输入产生32bit校验码,并且帧尾的有效字节不同。由于使用的是位宽64bit,所以可以一个时钟同时处理8个字节数据。数据帧结尾处数据含有有效数据或者校验的32位数据,如何处理结尾处的数据以及32位数据校验码的时序,使得XGMII接口设计成为本设计的关键。MAC控制整体设计,大体分为上层接口模块、控制器模块、状态机模块、流控模块、XGMII接口模块这五个模块。上层接口模块主要是把UDP/IP协议栈8bit数据通过该接口生成64bit数据位和7bit控制位;控制模块是判断发送暂停帧还是数据帧,如果数据长度小于规定的最小长度64字节,则进行数据填充(0字节),以满足最小的数据要求;状态机模块是在物理层的数据进入其中时,把整个数据添加上以太网帧头部和尾部校验码,此外状态机还要负责去掉前导码和帧起始定界符(SFD);流量控制模块是执行当前数据传输的流量控制;XGMII接口模块是把经过其中的64bit的数据位和7bit控制位转换产生32bit数据位和4bit控制位,发送到物理层,当接收物理层数据时,XGMII接口完成数据由32bit到64bit的转换。

4.1 CRC校验模块设计

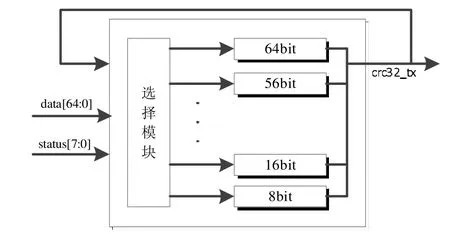

万兆MAC帧控制器的位宽为64bit,所以其校验主要以64bit校验为主,设计方法有两种[10-11]。第一种是,当tx_status[7]有效时,表示帧开始传输数据,进入状态机,同时进入CRC校验模块,开始进行数据校验。当检测到tx_status[6]有效时,检测tx_status[3:0]数值。不同的有效字节数有不同的校验模块,例如检测到数值位4时,触发32bit校验模块,将结尾32位有效数据输入32bit校验模块,完成最后的校验。方法一的校验过程如图3所示。运用此种方法,整个传输过程中没有延迟情况,有效率高的优点,但是比第二种方法占用了FPGA芯片更多的逻辑资源。

图3 CRC32无延迟校验模块

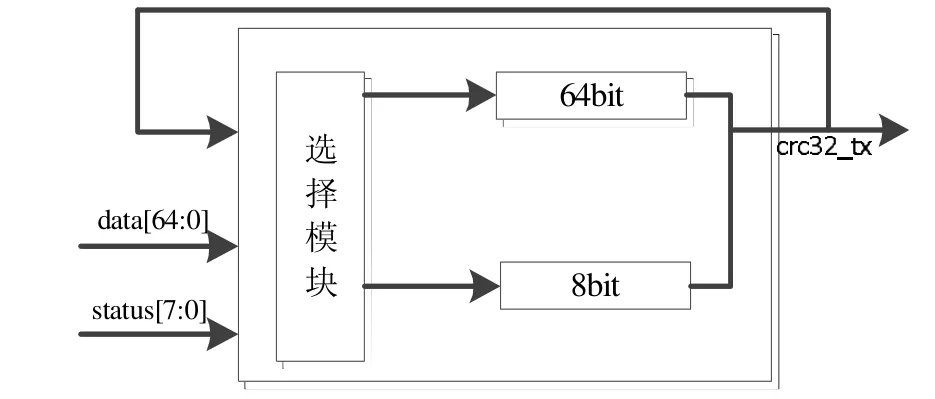

图4所示即为方法二,它也使用了64bit校验模块,当检测到帧结尾信号时,只使用8bit校验模块,而最后8字节数据将根据有效字节个数逐字节进行处理。例如,当有效字节为4时,将32bit数据输入CRC校验模块,每个时钟处理一个字节数据,4个时钟过后即得到CRC校验码,所得值和方法一相同。

图4 CRC32 8时钟延迟校验模块

这种方法的优点是占用的逻辑资源较少,但会产生数据延迟,最多延迟达8个时钟,同时为了实现在数据发送完毕时紧接着发送FCS,还需要增加一个缓冲模块,才能保证整个数据发送的完整性。

本研究所使用的FPGA芯片逻辑资源足以满足整个系统的设计,所以综合考虑使用第一种方法。

4.2 以太网帧处理

以太网帧处理分成接收数据和发送数据两个部分。发送数据将同步字段和校验位添加到以太网帧,接收数据将物理层接收到的数据进行分解,去除头部校验部分并判断是否满足最小帧长度要求,如果满足,则发送数据到UDP/IP协议栈。图5为将数据封装成以太网数据帧的结构设计。

图5 以太网发送模块

完成这些工作的主要模块是发送状态机和接收状态机。发送状态机设计的主要功能是把上层数据前端加入同步字节(前导码,起始定界符)8字节,由于数据位宽为64bit,所以只需要一个时钟周期就能把8个字节数据添加到以太网头部,与千兆以太网需要8个时钟周期才能完成这一动作相比,此方案节省很多时间,处理速度大有提高。但在数据帧结尾处,有效字段不定长,数据帧结尾处一个时钟周期需要发送8个字节数据,其中可能包括有效字节数和32位CRC校验数据,也可能不包括,针对这一点,将帧尾数据进行统计,把帧尾数据的各种情况列出两个表。

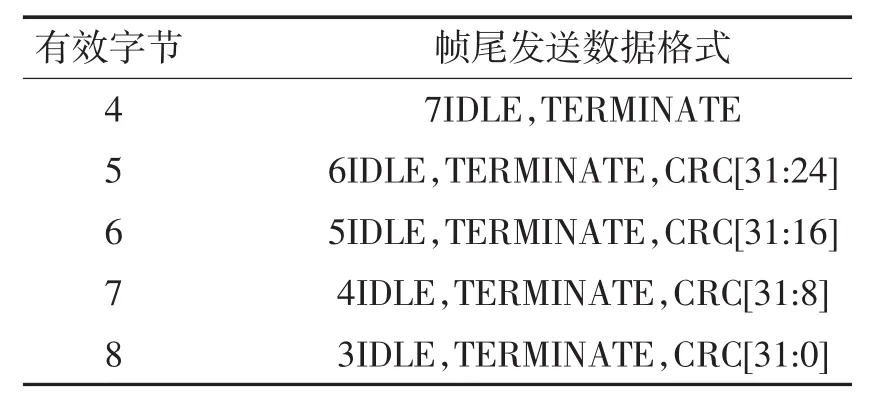

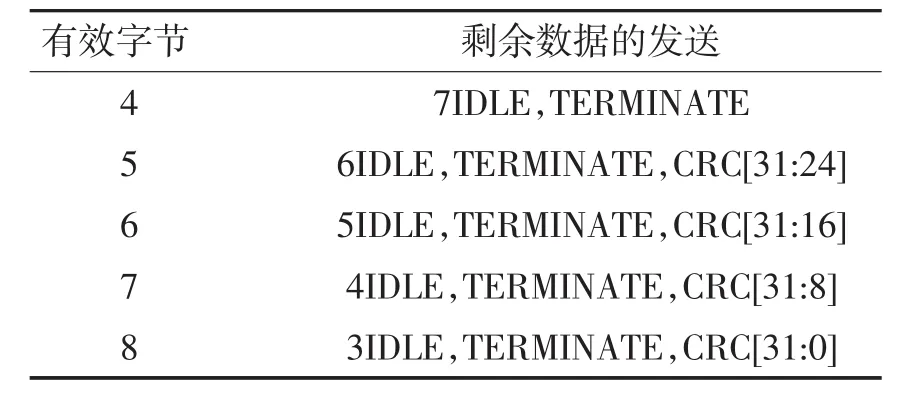

表2所示是当数据发送到帧尾时,帧尾内所包含的数据种类。表中IDLE、TERMINATE、CRC、data分别表示帧间隔、结束码、校验码、数据。由2表可知,不同的有效字节数,发送的数据不一样。当有效字节为4~8时缺少结束码和CRC32部分数据,这个状态下,还有部分信息不完整,还需要另一个时钟周期把未发送完成的数据发送出去。表3即是将剩余的部分发送出去,这样才能完成一帧以太网数据帧的发送。由于协议规定,每一帧数据的起始数据必须要在通道next_xgmac_txd[7:0]处,设计也保证了帧的每次传输的起始位置都在next_xgmac_txd[7:0]通道的位置上。

表2 帧尾数据

表3 剩余帧尾数据

5 验证仿真

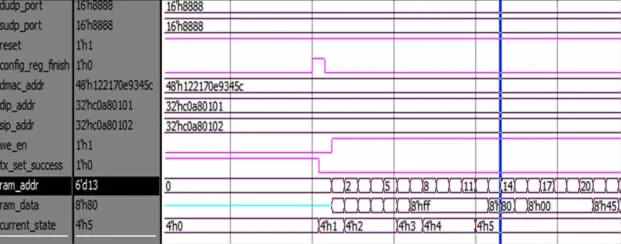

采用ALTERA公司的Cyclone IV系列EP4CE6F17C8N器件,共有6272逻辑单元,6272逻辑门,276480 RAM;使用Verilog语言编程;使用Mentor公司的ModelSim对设计进行功能仿真。UPD/IP协议栈发送仿真波形如图6。从图6可以看出,ram_addr地址计数器位13和14是发送的80两个字节,整个数据在UDP/IP协议栈传输,添加数据帧头数据,整个过程按照表1的顺序进行数据传输。在传输过程中,竖线的位置为IP头部校验和,将IP头部数据进行计算,两个数值相等,与设计相符合。

图6 UDP/IP协议栈发送仿真波形

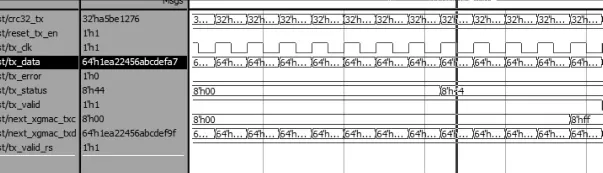

MAC发送控制器仿真波形如图7所示,其中next_xgmac_txd为XGMII接口发送数据,tx_valid_rs为整个数据传输的有效数据,由图可以看出当检测到开始帧数据时,开始发送数据,但是再发送数据前需要8字节帧同步信号。此处加了数据缓冲区的目的是为了缓冲一个时钟输入同步字段,且数据没有丢失。对于图7,当检测到数据帧结尾处时,此图的时序是4个有效字段,竖线所在位置为对结尾处数据帧的处理,分别取出CRC校验模块32位数据和数据帧前32位数据,组成帧尾数据,此状态没有结束码,则进入下一个状态进行结束码的输入,同时CRC32位校验码紧跟在数据帧后面。仿真波形符合设计的预定目标。

图7 MAC控制器发送模块时序

6 结束语

根据IEEE802.3-2005和IEEE802.3ae标准,使用ALTERA公司的Cyclone IV系列EP4CE6F17C8N,系统地阐述了对万兆以太网视频传输系统的设计,也详细介绍了UDP/IP协议栈设计和万兆MAC控制器设计。将传输层和网络层合并到一个处理模块中的思路,简化了系统的设计,同时节省了逻辑资源。针对MAC控制器的帧尾有效字节的不同,对以太网帧处理模块进行设计,并通过ModelSim对设计进行功能仿真。由仿真结果可以看出,协议规定的标准格式得到了满足。对并行输入CRC校验模块也做了设计,针对有效字节不定长的问题,提出两种解决方法。对设计模块进行布局布线后仿真,结果表明,整体传输速率可以达到10Gb/s。本研究对于摄像头实时监控系统的接收数据快速处理有着很高的应用价值。

[1]李嘉琛,杨光.基于FPGA的视频以太网传输[J].数字技术与应用,2017(4):32-35.LI Jiachen,Yang Guang.Video Ethernet transmission based on FPGA[J].Digital Technology and Application,2017(4):32-35.

[2]李修堂.基于FPGA的以太网UDP/IP处理器的设计与验证[D].成都:电子科技大学,2015.LI Xiutang.Design andverification of Ethernet UDP/IP processor based on FPGA[D].Chengdu:University of Electronic Science and Technology of China,2015.

[3]杨莹.10G以太网MAC控制器的设计与验证[D].合肥:中国科学技术大学,2016.YANG Ying.Design and verification of 10G Ethernet MAC controller[D].Hefei:University of Science and Technology of China,2016.

[4]丁铁夫,刘超,杨磊,等.基于千兆以太网的实时视频传输系统设计[J].微计算机信息,2008,24(36):132-134.DING Tiefu,LIU Chao,YANG Lei,et al.Design of realtime video transmission system based on Gigabit Ethernet[J].Microcomputer Information,2008,24(36):132-134.

[5]宋国栋,程伟森,程国栋.10G以太网光接口及其实现[J].中兴通讯技术,2004(s1):40-43.SONG Guodong,CHENG Weisen,CHENG Guodong.10G Ethernet optical interface and its implementation[J].ZTE Technology Journal,2004(s1):40-43.

[6]段晓晨,何小刚,程永强.实时视频SDRAM控制器的FPGA设计与实现[J].太原理工大学学报,2006(S1):8-11.DUAN Xiaochen,HE Xiaogang,CHENG Yongqiang.FPGA design and implementation of real-time video SDRAM controller[J].Journal of Taiyuan University of Technology,2006(S1):8-11.

[7]MILEVA A,PANAJOTOV B.Covert channels in TCP/IP protocol stack[J].Ext.ed.Central European Journal of Computer Science,2014,4(2):45-66.

[8]张友亮,刘志军,马成海,等.万兆以太网MAC层控制器的FPGA设计与实现[J].计算机工程与应用,2012,48(6):77-79.ZHANG Youliang,LIU Zhijun,MA Chenghai,et al.FPGA design and implementation of 10 Gigabit Ethernet MAC layer controllers[J].Computer Engineering and applications,2012,48(6):77-79.

[9]IEEE.Media Access Control(MAC)Parameters,Physical Layers,and Management Parameters for 10 Gb/s Operation[J].IEEE Stdae,2002.

[10]彭建辉.10G以太网接口并行CRC校验的一种简化算法[J].微计算机信息,2006,22(20):213-215.PENG Jianhui.A simplified algorithm for parallel CRC check of 10G Ethernet interface[J].Microcomputer Information,2006,22(20):213-215.

[11]刘昭,苏厉,金德鹏,等.10G以太网系统中的并行CRC编解码器的设计[J].电子技术应用,2004,30(4):47-50.LIU Zhao,SU Li,JIN Depeng,et al.Design of parallelCRC codec in 10G Ethernet system[J].Application of Electronic Technique,2004,30(4):47-50.