基于Hyperlynx高速PCB串扰及差分信号分析

2018-06-28

( 河北农业大学 教务处,河北 保定 071001 )

0 引言

高速电路的不断发展使得电子设备的时钟频率早已迈向了GHz的时代,对于绝大多数电子产品来说,当时钟频率超过100 MHz时,信号传输过程中产生的干扰问题就不能被忽略了。由于差分信号具有对外部干扰高度免疫性的优点,被广泛应用于电路设计中。电路板尺寸的减小,布线密度的增加、传输速率的提高,使信号完整性问题已经成为电路设计中必要环节之一,如何处理高速电路产生的问题成为设计过程中的关键[1]。ADV7390高速视频编码器容易受到噪声、电磁干扰等因素的影响而产生异常现象,如颜色异常、音色失真等问题,为了减小串扰、过冲、地弹噪声等干扰对信号传输过程中的影响,在遵循PCB布线原则和元器件的布局规则的前提下,还需要对系统采取必要的措施和改进[2]。以ADV7390高速视频编码器为基础对其进行了仿真研究,对其中的关键信号线进行了系统地讨论分析,在此基础上对其重要结构做了进一步验证和优化。

1 ADV7390编码器原理

图1 视频编码系统原理框图

ADV7390采用32引脚LFCSP封装,属于低功耗、高速、高度集成数模视频编码器,此编码器针对低功耗操作进行了优化,尺寸较小,能够将来自于CMOS设备传输的8位视频数据快速转换为标准模拟基带视频信号。其原理如图1所示。由于此系统信号传输关系较为复杂,若对整板每一路传输线都进行分析,过于繁琐且没有必要,所以选择了易产生干扰且易受到其它信号源干扰的关键网络进行研究。寻找关键网络信号可通过Hyperlynx自带的“Board Wizard”板级向导功能,通过对整块板进行快速地扫描和高效地处理,给出 网络警告信息报告从而判断关键网络;也可根据分析元器件的上升下降沿速率、工作频率、走线方式和走线长度来判断关键网络。结合板级向导与理论分析可知,此系统中高速信号集中于可编程时钟与时钟分配的传输线上,由此判断出关键网络的具体位置。

2 传输线耦合理论

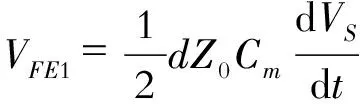

传输线之间产生的耦合一般分为容性耦合和感性耦合,低耦合理论认为当耦合系数k≤0.316时不会产生二次耦合,此系统满足低耦合理论。由于互耦电容的存在,动态线上产生的位移电流耦合至静态线并向两端传输,根据Kirchhoff电流定律得出[3]

(1)

式中,Z0为网络特性阻抗;Cm为传输线单位长度耦合电容大小;Vs为动态线上电压;Δx为耦合传输线长度。由于Vb=Vf,代入式(1)中,推导出对于长度为d的传输线,静态线上容性耦合产生的远端串扰为

(2)

同样根据Kirchhoff电流定律可以得出静态线上感性耦合产生的远端串扰为

(3)

式中,Lm为传输线单位长度互耦电感的大小,由于容性耦合和感性耦合产生远端串扰的极性相反,可以得出传输线上总远端串扰为

(4)

分析式(4)可知,传输线上的远端串扰为脉宽很小的脉冲信号,其串扰的大小与网络特性阻抗、传输线单位长度的电容、电感、耦合线长度等因素相关,且与耦合线长度成正比。在对传输线上的串扰耦合进行抑制时,可在这几方面采取抑制措施。

3 信号串扰仿真分析

3.1 等效电路模拟分析

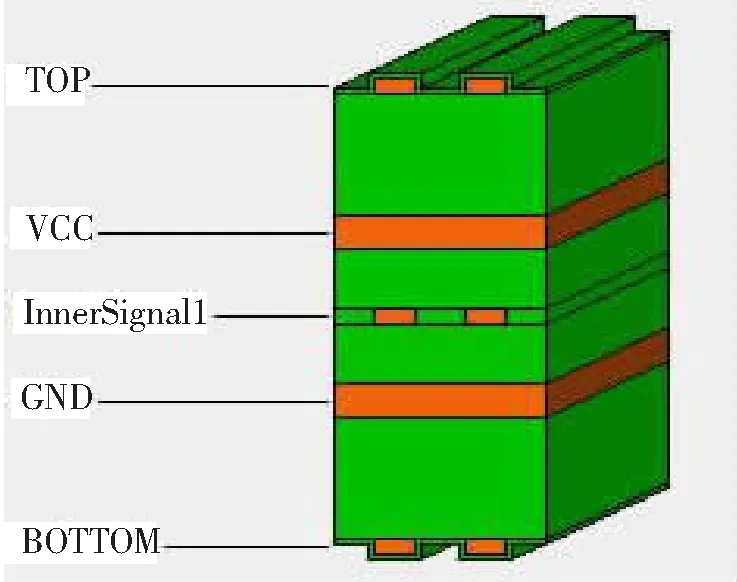

串扰是信号在传输线上传导时,相邻传输线之间产生的互容和互感效应而引发的噪声干扰。在设计高速PCB时,串扰现象是非常普遍的,同时也是影响信号完整性的主要因素之一。大规模的串扰会影响电路的传输特性,包括特性阻抗、传输速率、信号失真等问题。一般的信号串扰是由多种因素引发的,如叠层厚度、布线间距、平行线长度、端接技术等[4]。对此建立了双传输线模型如图2所示,图中传输线TL1和TL2分别为攻击线和受害线,接收端和驱动端均为电压值3.3 V的高速CMOS模型,设置其基本参数为:走线长度12 cm,线宽102 μm,布线间距178 μm,介电常数4.0。其层叠结构如图3所示,两路传输线均布置于统一耦合区域InnerSignal层。

图2 双传输线模型

图3 PCB层叠结构设计

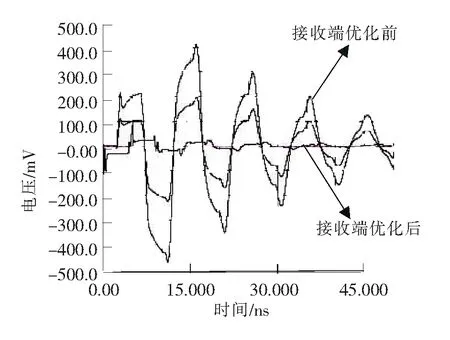

为了更直接地观察受害线受到串扰影响的干扰程度,将受害线的驱动端设置为恒低电平,且仅在受害线的驱动端U3.1和接收端U4.1处放置探针进行观测,对模型进行仿真运行,得到如图4所示的TL2传输线信号波形,由图可知,由于受到攻击线的串扰影响,使两条传输线产生了耦合效应,致使传输线TL2上的信号产生了很大的波动,最大值将近500 mV,如此大的干扰在实际过程中是不能忽略的。过程中由于能量传输损耗,致使波形随时间变化逐渐趋于平缓。

改变二者的布线间距,根据“3W”设计规则,即线间距应为线宽的3倍以上,将布线间距由原始178 μm修改为356 μm,再次运行仿真,得到如图5所示的波形图,发现增大布线间距后的信号干扰明显降低,优化后接收端U4.1的干扰电压的最大值约为200 mV,但依旧高于设计要求值40 mV,需要进行进一步优化。

图4 TL2传输线信号

图5 线间距优化前后对比

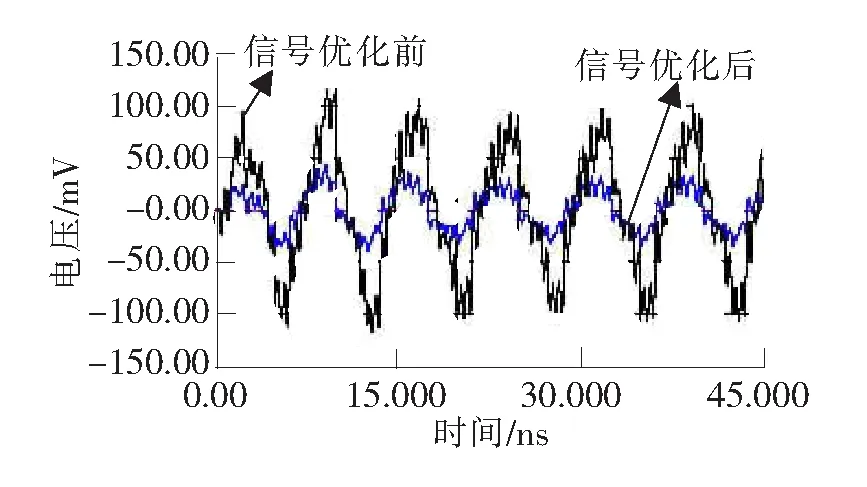

修改模型层叠厚度。将InnerSignal相邻上下层介质厚度减小一半,由原来的0.7 mm修改为0.35 mm,运行仿真,得到如图6所示波形图。图中可以看出,减小介质厚度后接收端U4.1的信号改善明显,由起初的串扰峰值200 mV降至50 mV左右。在此基础上,运行端接向导功能,向导给出端接建议阻值,在攻击线TL1传输线与IC元件U1.1之间串接建议阻值75 Ω的电阻,再次运行程序,仿真结果如图7所示。由于对攻击线进行了端接,净化了其传输信号,使得对周围传输线的干扰影响大大降低。分析图7可知,端接优化后,接收端U4.1最大串扰值仅为18 mV,满足设计需求。

图6 介质厚度优化前后对比

图7 端接优化前后对比

3.2 PCB板级串扰分析

通过分析此PCB中传输速率、工作频率、走线长度等因素,从而判断,关键网络位于可编程时钟和时钟分配之间的传输线上[5]。将耦合电压设置为50 mV,即与关键网络之间产生的串扰值大于50 mV的传输线均视为攻击网络。为了使波形更加清晰精准,将关键网络设置恒为低电平观察其受影响程度。运行仿真,得到如图8所示的串扰网络。图中实线部分为关键网络传输线CLK,两条虚线表示两路攻击网络DSR和RTS,图中虚线框部分表示三者之间产生串扰耦合的区域,说明此处产生的耦合电压值已超过设定值50 mV。

图8 耦合电压40 mV时的串扰信号

对图8中参数进行设置,将关键网络CLK的驱动端U1.AD5设置为静态,设置攻击网络的驱动端U1.AD10和U1.AK8为“CMOS”模型,运行仿真得到如图9所示的波形图。由图可知,关键网络CLK已设置为静态,但由于受到附近攻击网络1、2的影响产生了串扰效应,引发了网络CLK在零电压上下的波动,波动峰值超过了100 mV。根据端接向导的建议阻值,在此情况下对攻击网络1、2的驱动端分别串接了100 Ω和150 Ω的电阻,再次运行仿真,结果如图10所示。图中分别为采取端接电阻措施前后关键网络CLK的波形,对比两波形可以发现,端接优化后其信号波动明显降低,波形最大值仅为37 mV左右。

图9 优化前信号串扰波形

图10 优化前后CLK接收端信号对比

4 差分信号分析

4.1 差分对理论

差分对是通过两条完全互补的信号线驱动,差分对可以很好地避免噪声干扰并提高信噪比,可以利用相反的磁场极性来抵消外界的电磁干扰,但对布线有较高要求,两条传输线必须始终平行,且长度完全相同。假设传输线1、2的特性阻抗分别为Z11和Z22,电流分别为I1和I2,耦合常数为C1、C2,根据欧姆定律,可得出两传输线的电压为[6]

(5)

当传输线间距较近时,则阻抗Z11=Z22=Z0,I1=-I2,C1=C2=C,可得到其差分阻抗为

Zdiff=2V1/I1=2Z0(1-C)

(6)

分析上式可知,当传输线间距较小时,差分对的特性阻抗比单个传输线对地阻抗的2倍小,且差分信号线的间距越小,它们之间的耦合能力越强,抵抗外界干扰能力越强。

4.2 差分传输线仿真

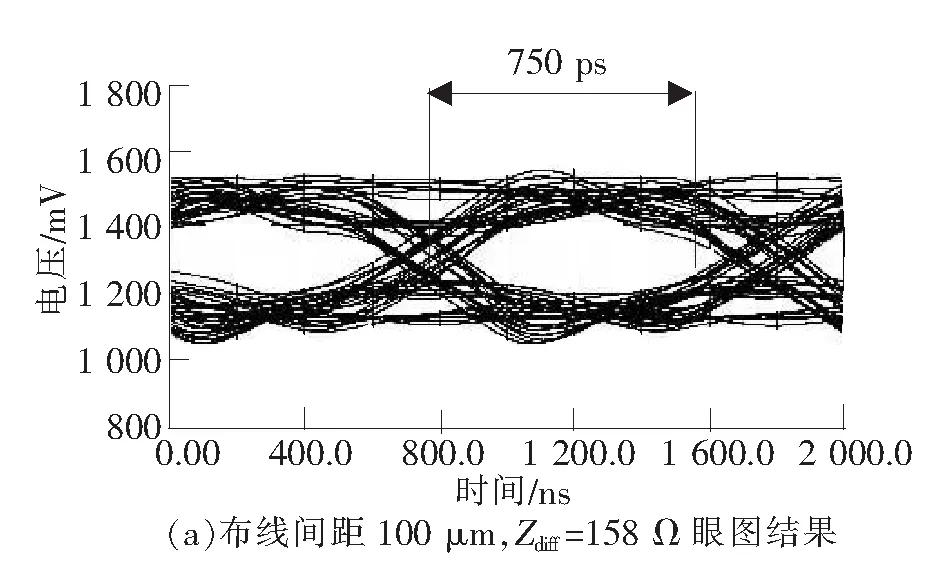

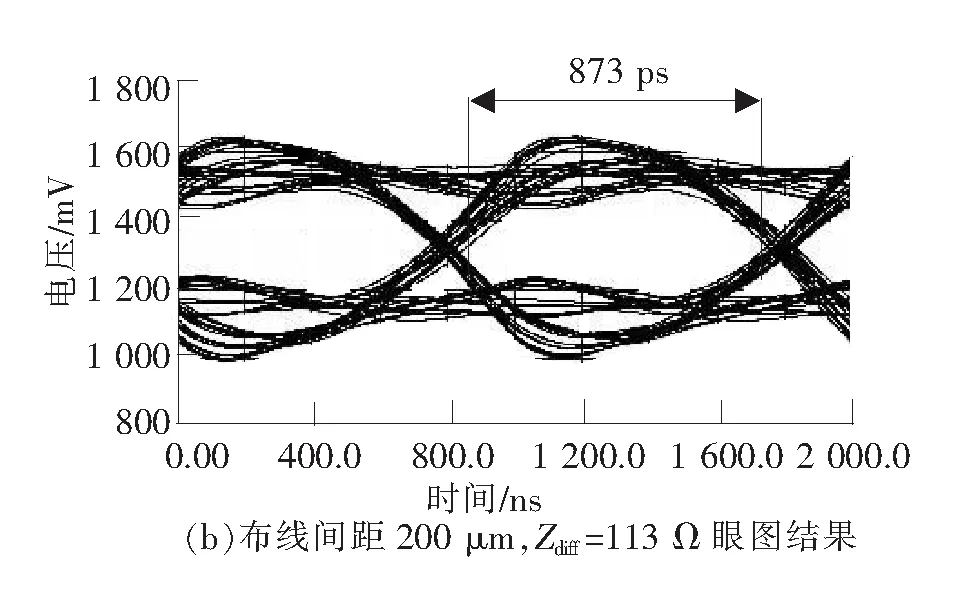

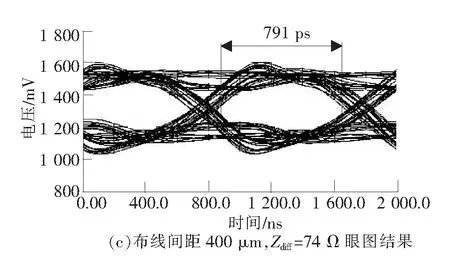

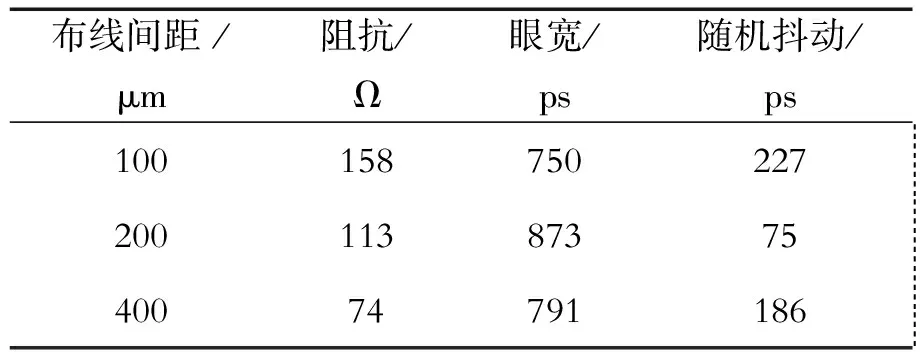

时钟差分对传输线传输速率高,对阻抗匹配有较高要求。对时钟差分对阻抗的有效控制,能保证元器件连接之间信号内部转换的正确性[7]。通过理论计算得到差分阻抗为110 Ω,以此来指导差分布线。在不考虑过孔影响的情况下,差分对布线间距为200 μm,由式(5)和式(6)可知,可以通过改变布线间距去改变差分阻抗值。为了验证理论计算的正确性,设计了3种不同的布线间距,分别为100 μm、200 μm、400 μm,三者对应的差分阻抗分别为158 Ω、113 Ω、74 Ω。

为了更为直观和准确地分析3种情况,通过眼图观测波形。“眼”张开的大小表示信号失真的程度,直观地反映了码间串扰的强弱、噪声影响以及信号传输的优劣,眼宽越大,抖动越小,则信号越好。设置眼图参数:驱动Bit流为伪随机码“PRBS”,序列位数为6,Bit间隔1 ns,起始状态为“Low”,抖动区域为高斯分布。运行仿真,结果如图11所示。

表1为3种情况下的数据对比,通过观察图11和表1可知,当布线间距为200 μm,差分阻抗为113 Ω时,眼宽为3种情况下最宽,其值为873 ps,且随机抖动最小,仅为75 ps,“眼”张开最大,表示其信号失真最小,信号完整性最好。其它两种情况,信号传输情况均不太理想,宜采用差分阻抗为113 Ω的布线方式。

图11 差分阻抗对信号的影响结果

表1 不同差分阻抗的数据对比

4.3 差分对场强分布结果

为了较为直观地反映差分对的耦合特性和电场分布,利用ANsoft HFSS建立了等效差分对模型,设置其介质厚度为1.5 mm,介电常数为4.0,差分对线长7 cm,线宽102 μm,布线间距200 μm。计算得出差分阻抗110 Ω,输入差分信号,运行仿真,结果如图12、图13所示的差模场强覆盖图,由图12可知,由于差分信号相位差的影响,在差分对传输线的垂直切面方向形成了电壁—奇对称轴,中间颜色较深区域表示电力线较为密集,耦合较强,差分对两侧越远区域电场越弱。分析图13矢量场强覆盖图可知,图中磁针指向表示电力线方向,电力线从正电压传输线出发回到了负电压传输线。

图12 差分场强覆盖云图

图13 差分矢量场覆盖图

5 结论

本文主要对高速PCB的串扰和差分对等信号完整性问题进行了研究讨论,基于ADV7390视频编码器,利用Hyperlynx建立了传输线等效模型并对实际布线后PCB中的关键信号线进行了串扰仿真分析,发现其信号传输过程中失真严重,针对此问题提出了具体优化措施,通过修改介质厚度、布线间距和端接电阻等方式使信号质量得到了明显改善。应用眼图对比分析结果验证了时钟差分对传输线阻抗匹配的合理性,并利用ANsoft HFSS分析了差分对传输过程中的场强分布,为设计差分布线间距和差分走线方式提供了依据。结果表明,仿真分析对PCB的设计及优化具有重要的指导作用,对其信号完整性分析有较为深远的意义。

参 考 文 献

[1]杨华,陈少昌,朱凤波. 高速数字电路PCB中串扰问题的研究与仿真[J]. 电光与控制,2012,42(3):90-94.

[2]张成刚,李斌,王六春. 高速PCB信号完整性仿真与分析[J]. 微波学报,2012,47(S3):359-360.

[3]张木水,李玉山.信号完整性分析与设计[M].北京:电子工业出版社,2010.

[4]张志伟. 高速互连总线结构中多平行传输线间的串扰分析与控制[J]. 计算机应用研究,2013,35(12):3729-3731+3734.

[5]闫静纯,李涛,苏浩航. 高速高密度PCB电源完整性分析[J]. 电子器件,2012,52(3):296-299.

[6]张海风.Hyperlynx仿真与PCB设计[M].北京:机械工业出版社,2005.

[7]杨章平. 高速PCB设计中的差分等长处理及仿真验证[J]. 通信技术,2015,48(5):626-630.