射频信号生成系统PCIe总线接口设计

2018-06-19刘瑞麒姚志成

刘瑞麒,杨 剑,姚志成,耿 志

(1.火箭军工程大学 控制工程系,陕西 西安 710025;2.原成都军区联勤部 后勤信息中心,成都 四川 610015)

0 引 言

随着电子对抗活动的发展,对信号源在高速率、宽频段及可灵活配置等方面提出了迫切需求。高速DAC技术的发展使器件具备极高的采样速率与转换精度,使多样化、宽频段信号的产生成为可能[1-6],但对控制端上位机数据传输总线速率提出了更高要求。传统的PCI总线带宽过小,难以满足需求。PCIe总线技术是由英特尔提出的第三代高性能I/O总线技术,其提供了更加完善的性能,更强的可扩展性和更低的成本,充分弥补了PCI总线的不足,能够满足大量数据的高速传输需要。对PCIe总线接口开发,通常使用专用接口芯片进行,硬件开销大且可拓展性低,降低了设计配置的灵活性。Xilinx公司推出的第6代高性能FPGA芯片——Virtex-6内部集成了高速收发器GTX Transiver及PCIe硬核,能够通过编程实现PCIe总线接口功能。利用其开发PCIe总线接口,既可降低开发成本,又可充分利用FPGA资源丰富、速度高和可重构的特点,提高了PCIe总线接口开发速度和使用灵活性。且相较PEX8111、PEX8311等专用接口芯片,其最高支持总线数据位数达到128位,单链路最高数据传输速率达5.0 Gb/s[7],能够满足PCIe高速数据通信需要。

基于此,本文针对射频信号生成系统数据高速交互需求,在Virtex-6 FPGA上开发了PCIe总线接口并实现DMA传输,最后在X8链路宽度下进行了测试。

1 系统结构概述

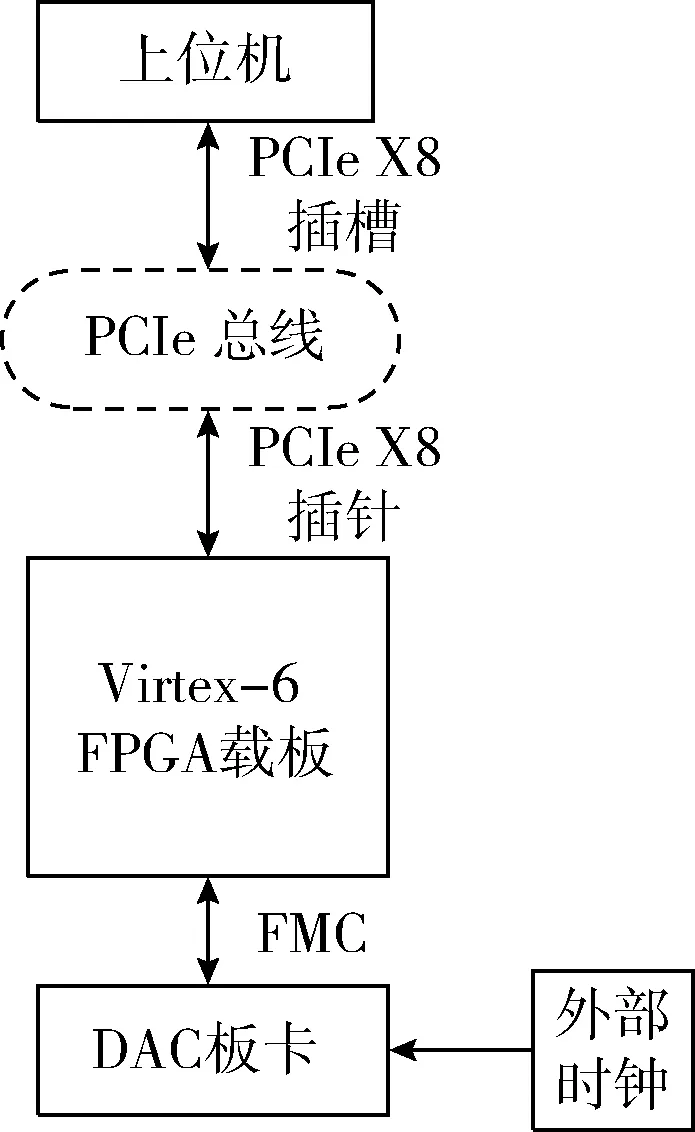

本设计中高速射频数模转换(DAC)板卡的核心为EV12DS130ACZPY芯片,其具有12位分辨率、3 Gs/s转换速率、7 GHz模拟输出带宽[8]。为使其正常工作,设计实现了如图1所示射频信号生成系统,主要由上位机、FPGA载板、高速DAC板卡组成。

图1 射频信号生成系统结构

在该系统中,上位机作为主控端,提供给操作者控制界面并生成射频信号对应的数据;FPGA载板为一块Xilinx ML605板卡,其通过PCIe插槽同上位机连接,通过FMC-HPC接口同高速DAC板卡连接,完成从上位机接收信号数据缓存及向DAC发送功能;DAC板卡为以EV12DS130芯片为核心的板卡,通过FPGA配置后可直接生成各类射频信号。

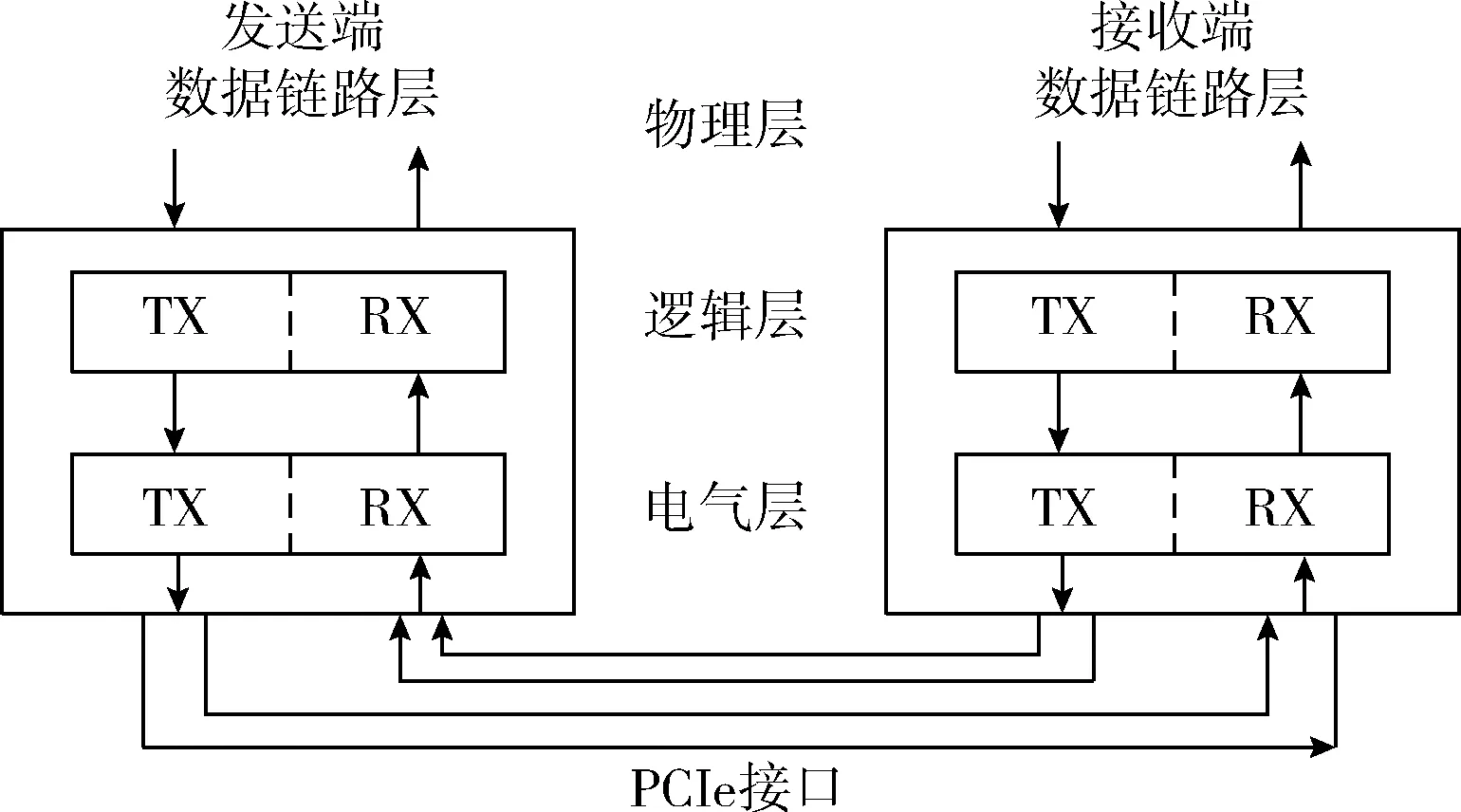

系统中使用的PCIe总线是一种高速串行总线,为实现高速数据传输功能,在电气连接上PCIe总线采用了差分信号传输方式,同单端信号相比,差分信号抗干扰能力更强,且差分信号对外界的电磁干扰较小,能够满足更高的总线频率需求。在数据传送上,PCIe总线采用了端到端的数据传送方式,其发送端和接收端中都含有发送逻辑和接收逻辑。PCIe总线的一个基本数据通路结构如图2所示。

图2 PCIe总线接口结构

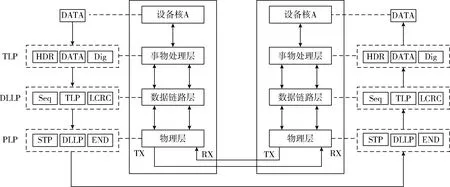

PCIe总线使用数据包(Packet)进行数据传输,数据报文在接收和发送过程中。首先在设备的核心层(device core)中产生,然后再经过该设备的事务层(transaction layer)形成事务层包(TLP)向数据链路层(data link layer)发送,数据链路层在TLP包上附加错误核对标志信息后向物理层发送(physical layer),物理层对TLP包进行编码后,最终发送出去。而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达设备核(device core),完成数据的传递[9-11]。数据通信结构如图3所示。

图3 PCIe通信结构

2 PCIe总线接口设计

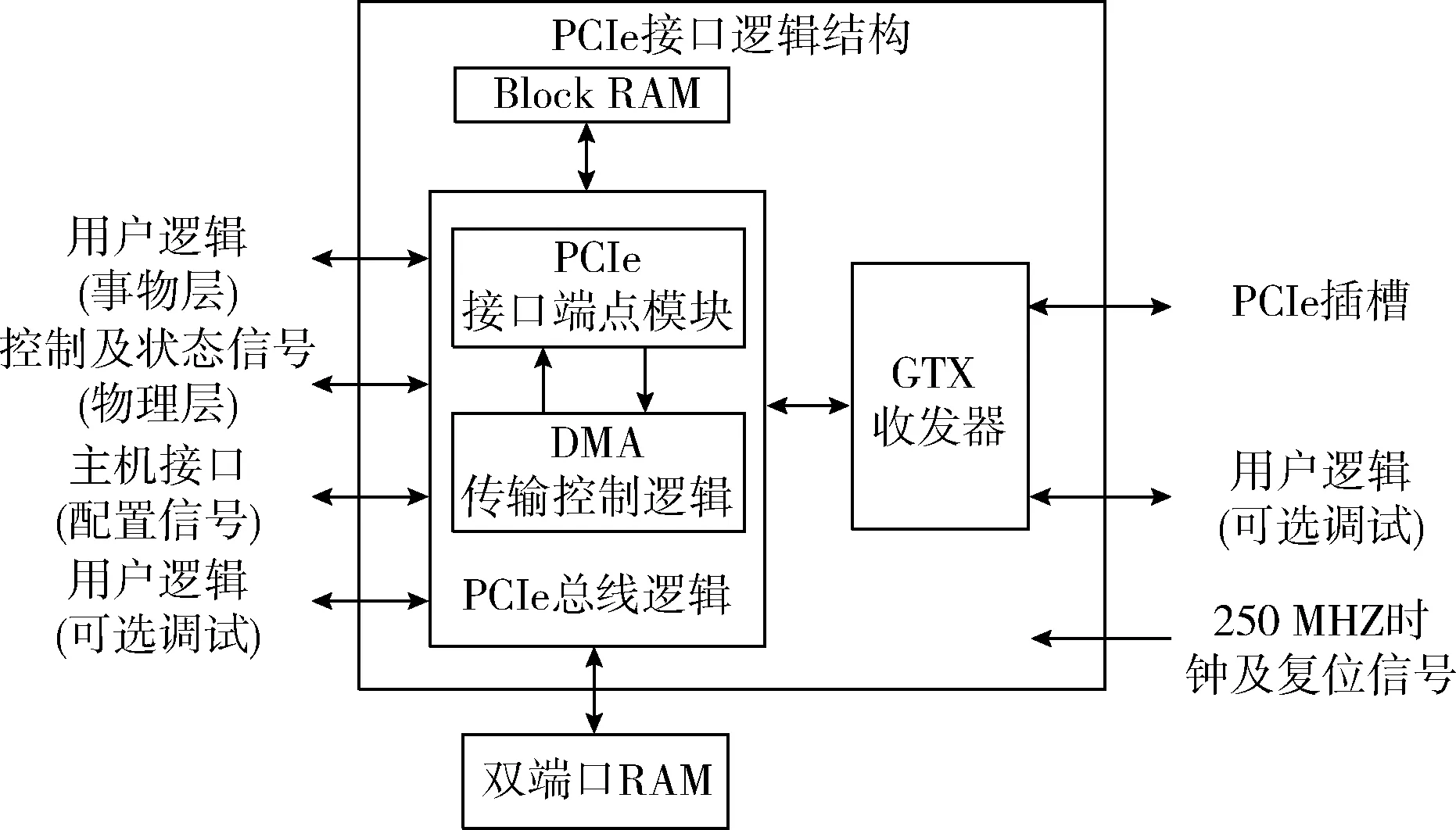

利用FPGA实现PCIe总线接口功能,需要搭建PCIe总线端点模块并设计总线数据传输控制逻辑。Xilinx Virtex-6为PCIe开发方便,集成了PCIe总线接口硬核,该模块支持2.0版本的PCIe协议,经由GTX收发器能够支持Gen 2(5 Gb/s速率),并且接口模块支持X1,X2,X4或者X8的位宽[12]。为测试方便,本设计在设备端专门添加了双端口BRAM以便接收和发送PCIe总线上的数据。本文设计的PCIe顶层模块结构及接口如图4所示。

2.1 PCIe总线接口端点模块设计

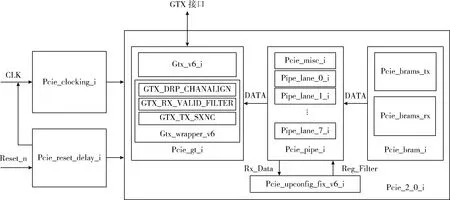

为搭建PCIe总线接口端点模块,需在FPGA中编写相应逻辑以实现PCIe协议中的事务处理层、数据链路层及物理层结构。本文所设计的PCIe端点模块结构如图5所示。

图4 PCIe总线接口顶层结构及接口

PCIe_pipe模块,为PCIe内部各条链路搭建了信号通道,每条链路包含一对差分的发送和接收信号,与GTX收发器相连,保证信号在PCIe核中的传输;

PCIe_gt模块,通过调用GTXE1 IP核,封装PCIe各个链路信号与GTX收发器的连接关系,实现同外部设备间的高速信号连接;

PCIe_brams模块,通过调用RAM IP核,搭建块随机存储器(Block RAM),实现总线高速信号的缓存;

图5 PCIe端点模块结构

PCIe_upconfig模块,为端口配置模块,内部包含PCIe配置空间及状态与控制寄存器,实现PCIe配置及数据统计监测功能;

PCIe_clocking模块,通过调用MMCM时钟管理IP核,将外部输入时钟分频变换后为PCIe程序中的各个模块提供所需时钟。

由于PCIe设备的时钟信号是保证PCIe设备正确工作的关键信号,在PCIe协议中规定时钟信号为100 MHz。本设计为提高外部PCIe设备工作的独立性及设备性能,针对ML605板上独立250 MHz时钟信号设计了时钟管理模块PCIe_clocking,为PCIe 2.0模块、PCIe_pipe、PCIe_gt、PCIe_upconfig模块提供时钟信号[13]。

由ISE软件生成的RTL如图6所示。

图6 时钟模块RTL级结构

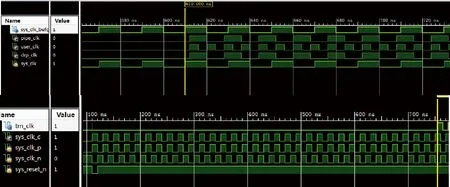

为确保时钟设计正确,使用Isim对该模块进行仿真,通过图7中仿真结果,可以看出时钟转换模块所产生的各个时钟信号与所设计的时钟逻辑相符。

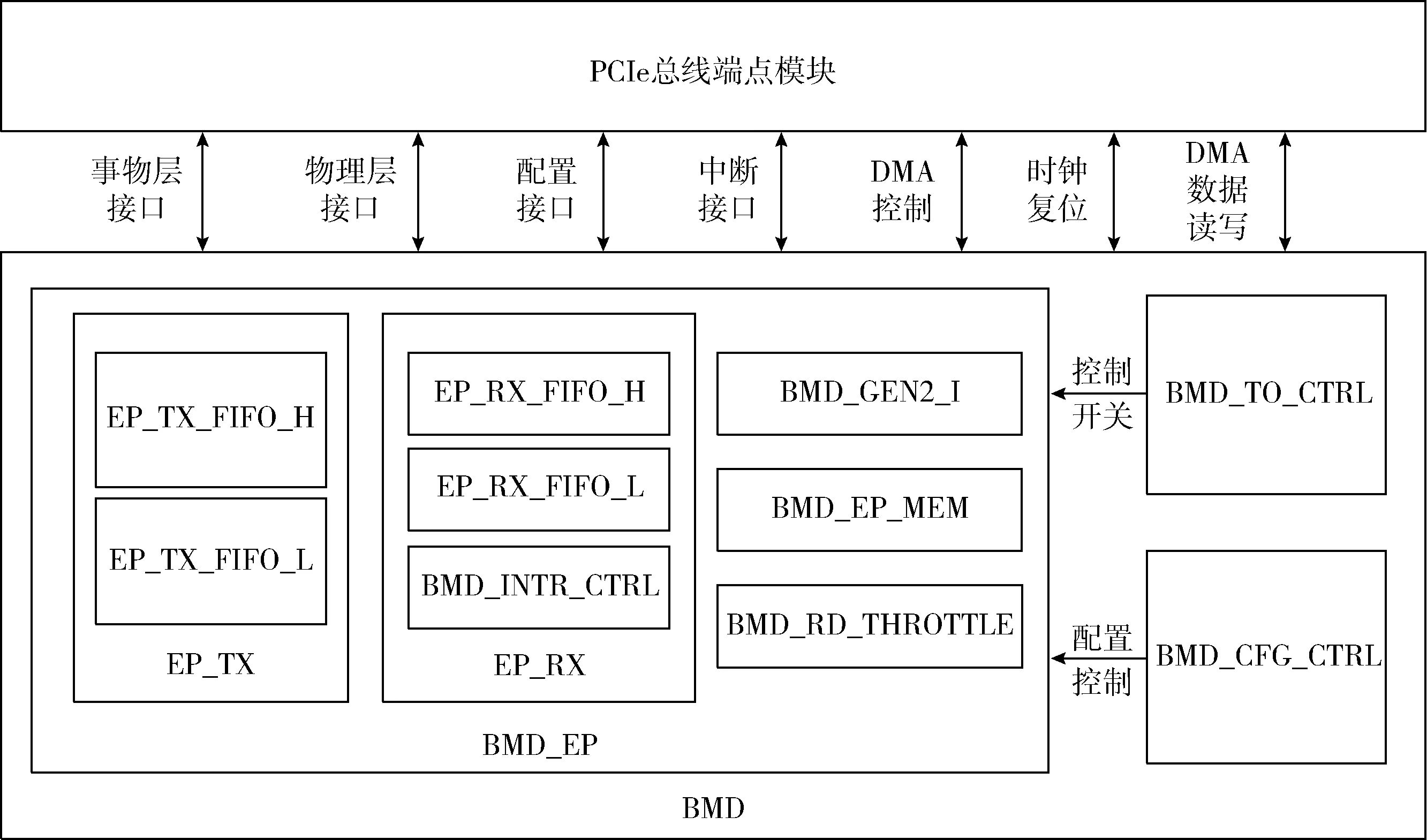

2.2 DMA控制逻辑设计

射频信号生成过程中需要对数据进行猝发式传输,通过CPU执行I/O端口指令来进行数据的读写的PIO数据交换模式已经不能够满足要求,需要采取通过DMA控制器控制传输过程,且传输速率较高的直接内存访问方式来对数据进行传输[14-16]。为在PCIe总线接口中实现DMA传输,设计了结构如图8所示的总线控制模块,与PCIe总线接口通道模块一起实现DMA传输。

图7 时钟模块时序仿真结果

EP_TX和EP_RX模块,通过调用FIFO IP核,实现对端口发送和接收数据的缓存,其中的中断控制模块对收发数据进行精确控制;

BMD_EP_MEM模块,为端点控制和状态寄存器,实现对总线数据的暂存和工作状态的控制;

BMD_GEN2模块,是针对64位系统接口设计的直接连接转换模块,实现对总线连接的检查和相关协议的转换;

BMD_RD_THROTTLE模块,通过测量读到的数据并进行控制,实现对读到的数据位数的控制;

图8 总线控制逻辑结构

BMD_TO_CTRL模块,通过检测总线传输请求和等待状态,实现对总线工作的开关控制;

BMD_CFG_CTRL模块,实现对总线的配置控制。

在数据传输时,上位机发送DMA地址及相关控制指令给端点模块,经由其转换后发送给BMD模块中的TO_CTRL及CFG_CTRL模块启动DMA传输。上位机发送的TLP包经过端点模块后取得相应的数据暂存在BMD FIFO中,并向双端口RAM发送供用户端调用,当RD_THROTTLE检测到传输数据位数达到设定值时向端点模块发送中断请求指令,端点模块向上位机发送总线中断请求,如此反复,直到上位机发出停止DMA传输指令,完成一次数据传输。

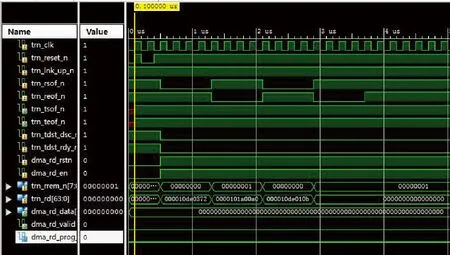

为验证程序逻辑设计正确,以Isim软件对BMD模块的读数据操作进行仿真为例,得到图9的仿真结果。从中可以看出,trn_reset_n给出复位信号后,当trn_rsof_n,trn_tdst_rdy_n置0,程序从trn_rd读入TLP包数据,当数据接收完后,trn_reof_n变为置0、trn_rsof_n置1,同设计的逻辑一致。

图9 程序DMA读操作时序仿真

2.3 GTX收发器及时钟约束设计

为满足总线接口程序高速数据传输硬件实现,在设计中需要使用GTX模块对数据进行传输。GTX是Virtex-6系列FPGA上的低功耗吉比特收发器,其由FPGA的可编程逻辑资源集成且具有较高的可配置性。相较于早期Virtex-5芯片中的低电压吉比特收发器GTP,其性能明显提高,器件线性工作速率覆盖750Mb/s-6.6Gb/s,正确配置与使用GTX收发器能更好发挥器件性能。

在配置GTX收发器时,通过GTX Wizard在图形化界面中完成参数配置,并生成IP核进行调用。由于高速信号传输对管脚布置要求较高,在不同型号的FPGA芯片具有专门的GTX管脚分布及约束方式,因而在设计中需要针对所使用的xc6vlx240t-1156芯片的约束文件进行专门配置。

针对参考时钟信号,本设计对应的硬件板卡采用了单个250 MHz外部差分参考时钟输入方式。在对GTX收发器配置时,此信号必须被作为一个专用时钟信号,并且在引入GTX传输模块前,必须要经过一个差分缓冲器IBUFDS,因此需要在UCF文件中利用语句IBUFDS_GTXE1实例化该模块已完成时钟信号的配置。最后,为产生多种时钟信号供不同GTX模块使用,在设计中调用了时钟管理模块MMCM对250 MHz的参考时钟信号进行变换,因而在约束文件中利用语句MMCM_ADV实例化时钟管理模块的相关连接。

针对PCIe传输的8条通道,由于其相互独立工作,因而在为其设计约束时,应使各条Lane的连接相互独立,为其配置不同的GTX收发器。

此外,在Virtex-6中每4个GTX收发器被串在一个Qaud中,每个Qaud中的4个GTX收发器共用一个差分时钟信号。由于这种特殊的构成方式,当FPGA芯片中的多个GTX被使用时,为了避免在高速设计中信号的抖动幅度过大,需要合理分布GTX信号与时钟输入信号在FPGA中的位置。

针对以上信号在FPGA位置的分配,Xilinx规范同一个参考时钟信号最多供给3个Quad使用,并且在时钟信号资源上方和下方的Quad数量都不能超过1个。设计时还需要遵循同一个物理接口的几个GTX放在一起,由同一个参考时钟作为时钟输入;不同物理接口的GTX如果在同一个参考时钟的驱动覆盖范围内,可以采用同一个参考时钟输入的原则[17]。

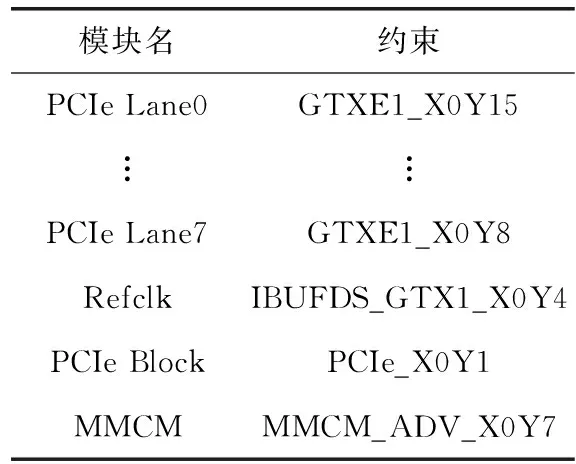

通过查阅芯片手册,在该款芯片中,GTX收发器共有5个Quad,分布于FPGA的X0Y1-X0Y15区,综合考虑后以上原则后对各个GTX模块做约束配置见表1。

表1 GTX模块约束设计

3 接口性能测试

为验证PCIe总线接口可用性及设计效果,将设计的FPGA程序通过Xilinx公司提供的ISE软件进行综合编译及布线后生成.bit文件,下载到FPGA中并将板卡与上位机连接,测试PCIe总线接口性能。

3.1 PCIe总线接口连接测试

PCIe总线接口设备正常工作需要由上位机通过插槽给出全局复位信号,因而当FPGA程序加载完毕后需重启计算机,之后计算机自动识别位于其主板PCIe插槽上的PCIe设备并提示安装驱动程序。通过硬件读写操作软件RW-everything能够对PCIe设备上的BAR 0空间进行读写操作,改变软件界面中各个地址空间所对应的寄存器值,能够使PCIe设备工作状态及存储值相应改变,可证明设备工作正常。

3.2 程序逻辑测试

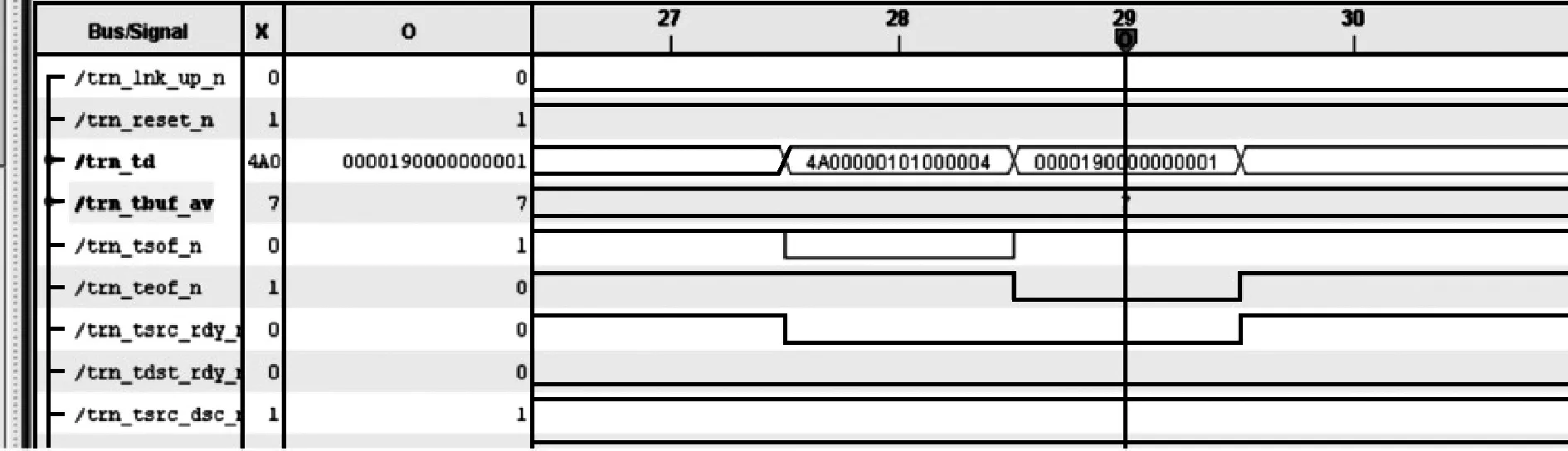

为检查在程序仿真中没有能够发现的错误,通过Xilinx提供的在线调试工具Chipscope对程序进行检测[18,19]。通过ISE在设计文件中加入Chipscope IP核,并添加期望观察的信号,编译成功并下载到FPGA后,可通过Chipscope pro Analyzer对PCIe设计中各个信号在FPGA中的值进行观察分析,并与PCIe协议相比对。在此由FPGA通过PCIe总线向上位机发送一个TLP包,并进行抓取波形观测。从图10中可以看出,在发送TLP包开始时trn_tsof_n(包开始信号)为低电平,结束时trn_teof_n(包结束信号)为高电平,trn_tdst_rdy_n(数据接收准备好信号)为低电平,与正确的发送逻辑相符。

图10 TLP包传送信号抓取

3.3 DMA速度测试

利用WinDriver软件对PCIe设备开发相应驱动程序并安装,在VisualStudio 2010上编写测试程序,通过调用WinDriver提供的API函数访问PCIe设备,向板卡发送和读回TLP包。通过记录传输过程中经过的TRN_CLK脉冲数n,由式(1)可精确计算传输速度

(1)

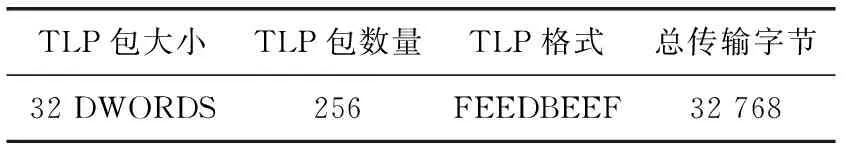

性能测试数据包设定见表2。

表2 测试用TLP包数据

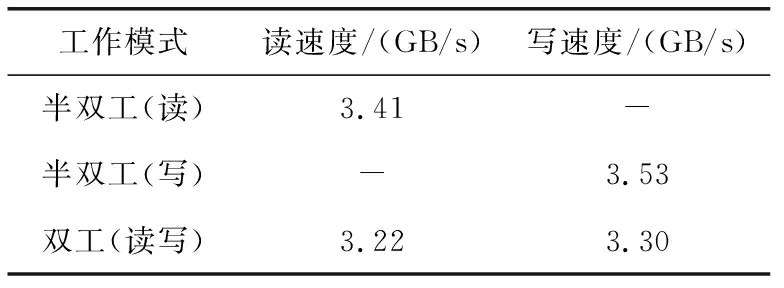

通过计算,此PCIe设备的读写速度测试结果见表3,从测试结果可以看出,设计的PCIe总线接口读写速度接近于PCIe 2.0协议中给出的4 GB/s(X8链路最高速率)。

表3 读写测试结果

注:本测试基于Xilinx ML605评估板,ASUS B85-PLUS R2.0主板。

4 结束语

本文针对射频信号生成系统数据高速交互需求,在Xilinx Vertex6 FPGA芯片为核心的平台上开发了PCIe总线接口及DMA传输方式控制程序。经测试,本文开发的硬件程序逻辑正确,功能完备,并且在通用平台下测试,半双工模式下能够达到最高3.53 GB/s的写速率及3.41 GB/s的读速率,接近理论最大值4 GB/s。能够满足数据高速传输需求,解决了射频信号生成系统数据高速交互的瓶颈问题,具有良好的可拓展性及实用价值。

参考文献:

[1]ZHAO Li,LIU Chaohua.Analysis of the current situation of military communications countermeasures[J].Digital Technology and Applications,2014,16(8):48(in Chinese).[赵莉,刘超华.军事通信对抗发展现状分析[J].数字技术与应用,2014,16(8):48.]

[2]ZHANG Naiqian,MA Jianguang.Looking at the development and application of Russian electronic warfare equipment from the Syria war[J].National Defense Science and Technology,2016,37(4):21-25(in Chines).[张乃千,马建光.从叙利亚战争看俄罗斯电子战装备发展与运用[J].国防科技,2016,37(4):21-25.]

[3]Liu H J.Overview of U.S.military airborne RF and FSO hybrid communication[J].Telecommunication Engineering,2014,54(12):1711.

[4]Qiu L.Design of high speed high resolution ADC with innovative architecture and circuits[D].Singapore:Nanyang Technological University,2016:46-65.

[5]BAO Xiaoqi.Research and design of high-speed arbitrary waveform synthesis technology[D].Taiyuan:North Central University,2015:86-97(in Chinese).[鲍晓祺.高速任意波形合成技术研究与设计[D].太原:中北大学,2015:86-97.]

[6]Sadri M,Schryver C D,Wehn N.High-bandwidth low-latency interfacing with FPGA accelerators using PCI express[M].Germany:Springer International Publishing,2015:117-141.

[7]Virtex-6 family overview v2.5[M].America:Xilinx,2015:16-31.

[8]EV12DS130ACZPY/EV12DS130AVZPY low power 12-bit 3 GSps DAC with 4/2:1 MUX datasheet[M].England:e2v,2012:2-10.

[9]XU Feng.Design of PCI Express high-speed acquisition card based on Virtex-6[J].Modern Electronic Technology,2012,35(16):79-81(in Chinese).[许峰.基于Virtex-6的PCI Express高速采集卡设计[J].现代电子技术,2012,35(16):79-81.]

[10]LUO Xuanping,LIU Benyuan,LU Zaiqi.Design of PCIE interface based on Wishbone and endpoint IP[J].Modern Electronic Technology,2012,35(11):23-26(in Chinese).[罗宣平,刘本源,卢再奇.基于Wishbone和端点IP的PCIE接口设计[J].现代电子技术,2012,35(11):23-26].

[11]XIAO Mingguo,DONG Mingli,LIU Feng,et al.Design and implementation of data acquisition card based on PCIe bus[J].Computer Measurement and Control,2016,24(3):252-254(in Chinese).[肖明国,董明利,刘锋,等.基于PCIe总线的数据采集卡设计与实现[J].计算机测量与控制,2016,24(3):252-254.]

[12]Virtex-6 FPGA integrated block for PCI express user guide v1.3[M].America:Xilinx,2012:27-82.

[13]Virtex-6 FPGA clocking resources user guide v2.5[M].America:Xilinx,2014:86-121.

[14]LI Jingzhang.Based on design of PCI Express transmission FPGA[D].Chongqing:Chongqing University,2012:35-75(in Chinese).[李经章.基于FPGA的PCI Express传输设计[D].重庆:重庆大学,2012:35-75.]

[15]LI Muguo,HUANG Ying,LIU Yuzhi.DMA transmission design of PCIe bus interface based on FPGA[J].Computer Measurement and Control,2013,21(1):247-249(in Chinese).[李木国,黄影,刘于之.基于FPGA的PCIe总线接口的DMA传输设计[J].计算机测量与控制,2013,21(1):247-249.]

[16]CHEN Gang,ZHANG Jing,TANG Jian.A design method of PCIe bus and DMA based on FPGA[J].Ordnance Industry Automation,2014(5):75-77(in Chinese).[陈刚,张京,唐建.一种基于FPGA的PCIe总线及其DMA的设计方法[J].兵工自动化,2014(5):75-77.]

[17]LogiCORE IP Virtex-6 FPGA GTX transceiver wizard user guide v1.12[M].America:Xilinx,2012:23-45.

[18]CHENG Litao.Design and implementation of high speed PCIe optical fiber interface card based on FPGA[D].Harbin:Harbin Institute of Technology,2015:45-80(in Chinese).[成立涛.基于FPGA的高速PCIe光纤接口卡设计与实现[D].哈尔滨:哈尔滨工业大学,2015:45-80.]

[19]Chipscope pro software and cores user guide v14.3[M].America:Xilinx,2012:21-90.