基于FPGA的多频耳声导抗测试系统的设计

2018-06-12阮小微林霖王涛

阮小微 林霖 王涛

摘 要: 为了实现多频探测音的声导抗测试方法,提升声导抗诊断灵敏度,设计一种基于FPGA的多频耳声导抗测试系统。采用FPGA芯片协调多模块同步工作,实现上位机通信、探测音产生、气压改变、声压和气压信号采集、数据缓冲和传输等核心功能,由上位机软件对数据实时处理和鼓室导抗图显示。系统对多名正常听力成年人采用1 000 Hz高频和226 Hz低频探测音进行测试试验,结果稳定并与理论分析一致,表明该系统设计正确和工作可靠。

关键词: FPGA; 多频探测音; 耳声导抗测试; 诊断灵敏度; 同步工作; 鼓室导抗图

中图分类号: TN304.94?34; TH77 文献标识码: A 文章编号: 1004?373X(2018)12?0063?04

Abstract: A multi?frequency ear acoustic immittance testing system based on FPGA is designed to realize the acoustic immittance testing method for multi?frequency probing sounds and improve the sensitivity of acoustic immittance diagnosis. The FPGA chip is used to coordinate multiple modules′ synchronous working, so as to realize the key functions such as communication with the upper computer, generation of probing sounds, air pressure variation, acquisition of sound pressure and air pressure signals, and data buffering and transmission. The software of the upper computer is used to perform real?time data processing and tympanogram display. A test in which several adults with normal hearing were tested with the 1000 Hz high frequency probing sounds and 226 Hz low frequency probing sounds was carried out by the system. The testing results are stable and consistent with those of the theoretical analysis, which indicates the correctness and reliability of the designed system.

Keywords: FPGA; multi?frequency probing sound; ear acoustic immittance testing; diagnosis sensitivity; synchronous working; tympanogram

0 引 言

耳声导抗测试是在改变外耳道压力的情况下引起鼓膜连同听骨链对探测音的顺应性的改变,测量耳道内的反馈声压发生改变,利用等效容积法,将其与已知容积的标准腔内声压级相比,得到声导抗值,从而画出耳道内气压与声压的关系图,既鼓室导抗图[1]。耳声导抗测试被广泛应用于中耳功能状态检查。根据探测音的频率不同,可分为低频耳声导抗测试和高频耳声导抗测试。低频耳声导抗测试主要反映中耳的劲度声纳的情况,高频耳声导抗测试主要反映中耳质量声纳的情况[2]。测量时既要同步采集气压和声压数据,又要同步改变耳道内压力。国内关于耳声导抗测试仪器的研发较少,文献[1]利用ARM作为主控芯片,硬件结构复杂,且因ARM只有串行工作模式的限制[3],不能实现声压和气压采集并行同步进行,数据结果需要校正,较难实现。本文根据以上设计的不足,结合当前FPGA的发展及其接口简单灵活、数据传输速率快且资源容量大等特点[4],提出采用FPGA作为主控芯片实现耳声导抗测试仪的设计。FPGA芯片既能用作数字频率合成器(Direct Digital Synthesizer,DDS)产生多个频率探测音,又能同步控制气压声压采集,还能同步控制气压改变以及数据传输。

1 系统的总体设计

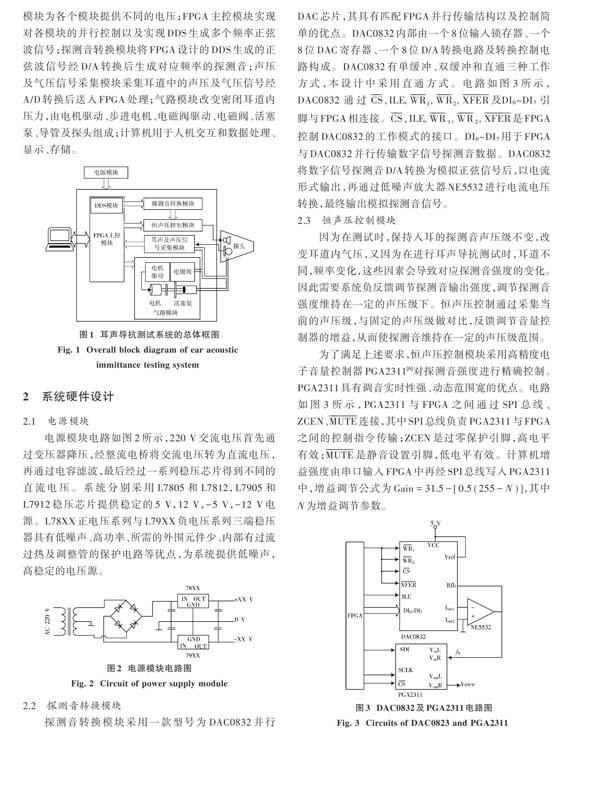

本设计主要由电源模块、FPGA主控模块、探测音转换模块、恒声压控制模块、声压及气压信号采集模块、气路模块以及计算机几个部分组成[5]。基于FPGA多频耳声导抗测试系统的总体设计框图如图1所示。电源模块为各个模块提供不同的电压;FPGA主控模块实现对各模块的并行控制以及实现DDS生成多个频率正弦波信号;探测音转换模块将FPGA设计的DDS生成的正弦波信号经D/A转换后生成对应频率的探测音;声压及气压信号采集模块采集耳道中的声压及气压信号经A/D转换后送入FPGA处理;气路模块改变密闭耳道内压力,由电机驱动、步进电机、电磁阀驱动、电磁阀、活塞泵、导管及探头组成;计算机用于人机交互和数据处理、显示、存储。

2 系统硬件设计

2.1 电源模块

电源模块电路如图2所示,220 V交流电压首先通过变压器降压,经整流电桥将交流电压转为直流电压,再通过电容滤波,最后经过一系列稳压芯片得到不同的直流电压。系统分别采用L7805和L7812,L7905和L7912稳压芯片提供稳定的5 V,12 V,-5 V,-12 V电源。L78XX正电压系列与L79XX负电压系列三端稳压器具有低噪声、高功率、所需的外围元件少、内部有过流过热及调整管的保护电路等优点,为系统提供低噪声,高稳定的电压源。

2.2 探测音转换模块

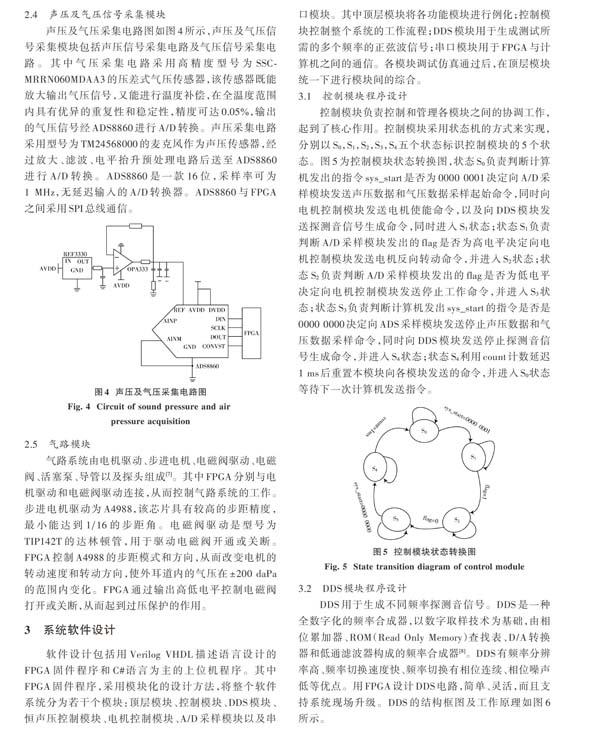

探测音转换模块采用一款型号为DAC0832并行DAC芯片,其具有匹配FPGA并行传输结构以及控制简单的优点。DAC0832内部由一个8位输入锁存器、一个8位DAC寄存器、一个8位D/A转换电路及转换控制电路构成。DAC0832有单缓冲、双缓冲和直通三种工作方式,本设计中采用直通方式。电路如图3所示,DAC0832通过[CS,ILE,WR1,WR2,XFER及DI0~DI7]引脚与FPGA相连接。[CS,ILE,WR1,WR2,XFER]是FPGA控制DAC0832的工作模式的接口。[DI0~DI7]用于FPGA与DAC0832并行传输数字信号探测音数据。DAC0832将数字信号探测音D/A转换为模拟正弦信号后,以电流形式输出,再通过低噪声放大器NE5532进行电流电压转换,最终输出模拟探测音信号。

2.3 恒声压控制模块

因为在测试时,保持入耳的探测音声压级不变,改变耳道内气压,又因为在进行耳声导抗测试时,耳道不同,频率变化,这些因素会导致对应探测音强度的变化。因此需要系统负反馈调节探测音输出强度,调节探测音强度维持在一定的声压级下。恒声压控制通过采集当前的声压级,与固定的声压级做对比,反馈调节音量控制器的增益,从而使探测音维持在一定的声压级范围。

为了满足上述要求,恒声压控制模块采用高精度电子音量控制器PGA2311[6]对探测音强度进行精确控制。PGA2311具有调音实时性强、动态范围宽的优点。电路如图3所示,PGA2311与FPGA之间通过SPI总线、ZCEN、[MUTE]连接,其中SPI总线负责PGA2311与FPGA之间的控制指令传输;ZCEN是过零保护引脚,高电平有效;[MUTE]是静音设置引脚,低电平有效。计算机增益强度由串口输入FPGA中再经SPI总线写入PGA2311中,增益调节公式为[Gain=31.5-[0.5(255-N)]],其中N为增益调节参数。

2.4 声压及气压信号采集模块

声压及气压采集电路图如图4所示,声压及气压信号采集模块包括声压信号采集电路及气压信号采集电路。其中气压采集电路采用高精度型号为SSCMRRN060MDAA3的压差式气压传感器,该传感器既能放大输出气压信号,又能进行温度补偿,在全溫度范围内具有优异的重复性和稳定性,精度可达0.05%,输出的气压信号经ADS8860进行A/D转换。声压采集电路采用型号为TM24568000的麦克风作为声压传感器,经过放大、滤波、电平抬升预处理电路后送至ADS8860进行A/D转换。ADS8860是一款16位,采样率可为1 MHz,无延迟输入的A/D转换器。ADS8860与FPGA之间采用SPI总线通信。

2.5 气路模块

气路系统由电机驱动、步进电机、电磁阀驱动、电磁阀、活塞泵、导管以及探头组成[7]。其中FPGA分别与电机驱动和电磁阀驱动连接,从而控制气路系统的工作。步进电机驱动为A4988,该芯片具有较高的步距精度,最小能达到[116]的步距角。电磁阀驱动是型号为TIP142T的达林顿管,用于驱动电磁阀开通或关断。FPGA控制A4988的步距模式和方向,从而改变电机的转动速度和转动方向,使外耳道内的气压在[±200] daPa的范围内变化。FPGA通过输出高低电平控制电磁阀打开或关断,从而起到过压保护的作用。

3 系统软件设计

软件设计包括用Verilog VHDL描述语言设计的FPGA固件程序和C#语言为主的上位机程序。其中FPGA固件程序,采用模块化的设计方法,将整个软件系统分为若干个模块:顶层模块、控制模块、DDS模块、恒声压控制模块、电机控制模块、A/D采样模块以及串口模块。其中顶层模块将各功能模块进行例化;控制模块控制整个系统的工作流程;DDS模块用于生成测试所需的多个频率的正弦波信号;串口模块用于FPGA与计算机之间的通信。各模块调试仿真通过后,在顶层模块统一下进行模块间的综合。

3.1 控制模块程序设计

控制模块负责控制和管理各模块之间的协调工作,起到了核心作用。控制模块采用状态机的方式来实现,分别以S0,S1,S2,S3,S4五个状态标识控制模块的5个状态。图5为控制模块状态转换图,状态S0负责判断计算机发出的指令sys_start是否为0000 0001决定向A/D采样模块发送声压数据和气压数据采样起始命令,同时向电机控制模块发送电机使能命令,以及向DDS模块发送探测音信号生成命令,同时进入S1状态;状态S1负责判断A/D采样模块发出的flag是否为高电平决定向电机控制模块发送电机反向转动命令,并进入S2状态;状态S2负责判断A/D采样模块发出的flag是否为低电平决定向电机控制模块发送停止工作命令,并进入S3状态;状态S3负责判断计算机发出sys_start的指令是否是0000 0000决定向ADS采样模块发送停止声压数据和气压数据采样命令,同时向DDS模块发送停止探测音信号生成命令,并进入S4状态;状态S4利用count计数延迟1 ms后重置本模块向各模块发送的命令,并进入S0状态等待下一次计算机发送指令。

3.2 DDS模块程序设计

DDS用于生成不同频率探测音信号。DDS是一种全数字化的频率合成器,以数字取样技术为基础,由相位累加器、ROM(Read Only Memory)查找表、D/A转换器和低通滤波器构成的频率合成器[8]。DDS有频率分辨率高、频率切换速度快、频率切换有相位连续、相位噪声低等优点。用FPGA设计DDS电路,简单、灵活,而且支持系统现场升级。DDS的结构框图及工作原理如图6所示。

图6中:K表示频率控制字;fclk表示时钟频率;f0表示DDS系统的输出频率;相位累加器是由N位的全加器和一个N位的相位寄存器构成。相位累加器相当于以步长K做累加运算,累加的结果存储在相位寄存器中;把相位寄存器中的结果作为地址码寻址存储在ROM的正弦表,每寻址一次,ROM查找表就输出一个对应的幅度值。为了节省ROM的存储空间,本设计中相位累加器只用了高M位而不用全部的N位来寻址。

DDS的输出频率为:

3.3 上位机设计

上位机程序主要负责下发指令控制FPGA各固件模块工作[9],完成声导抗测量并具有数据的传输、处理、显示和存储的功能,采用以C#语言为主的编程语言开发。上位机程序主要包括人机交互模块、数据传输模块、数据处理模块、鼓室导抗图显示模块,其采用多线程交互控制技术实现数据的同步传输、处理、显示、存储[10]。

4 实 验

为了测试本系统工作的有效性与稳定性,本文采用226 Hz和1 000 Hz探测音,分别重复进行4次实验。将实验的数据导入Matlab处理,画出鼓室导抗图如图7所示。

从图7可清晰看出,实验结果重复性强,同时证明,按上述方案设计的基于FPGA的多频声导抗系统运行稳定,具有很强的实用性和可行性。

5 结 论

本文设计了一种基于FPGA的多频耳声导抗测试系统。该系统采用FPGA芯片协调多模块同步工作,实现了上位机通信、探测音产生、气压改变、声压和气压信号采集、数据缓冲和传输等核心功能,由上位机软件对数据实时处理和鼓室导抗图显示。系统对多名正常听力成年人采用1 000 Hz高频和226 Hz低频探测音进行测试试验。结果表明,该系统设计正确,工作可靠稳定并与理论分析一致。

注:本文通讯作者为王涛。

参考文献

[1] 王立伟,李跃杰.一种基于ARM系统的多频耳声导抗测试系统的研究[J].医疗卫生装备,2008,29(1):3?5.

WANG Liwei, LI Yuejie. Research on multiple frequency tympanometry on ear system based on ARM [J]. Chinese medical equipment journal, 2008, 29(1): 3?5.

[2] 谢鼎华,伍伟景.基础与应用听力学概要[M].长沙:科学技术出版社,2016.

XIE Dinghua, WU Weijing, XU Li. Introduction to bases and applications of hearing science [M]. Changsha: Hunan Science & Technology Press, 2016.

[3] 韩彬,于潇宇,张雷鸣,等.FPGA设计技巧与案例开发详解[M].2版.北京:电子工业出版社,2016.

HAN Bin, YU Xiaoyu, ZHANG Leiming, et al. Detailed explanation of FPGA design skills and case development [M]. 2nd ed. Beijing: Publishing House of Electronics Industry, 2016.

[4] 樊继明,陆锦宏.FPGA深度解析[M].北京:北京航空航天大学出版社,2015.

FAN Jiming, LU Jinhong. Depth analysis of FPGA [M]. Beijing: Beihang University Press, 2015.

[5] MURAKOSHI M, YOSHIDA N, SUGAYA M, et al. Dynamic characteristics of the middle ear in neonates [J]. International journal of pediatric otorhinolaryngology, 2013, 77(4): 504?512.

[6] 徐荣,曾琼,田湘.音频控制芯片PGA2311的音频增益自动控制[J].单片机与嵌入式系统应用,2011,11(8):72?73.

XU Rong, ZENG Qiong, TIAN Xiang. Audio gain automatic control of audio control chip PGA2311 [J]. Microcontroller & embedded systems, 2011, 11(8): 72?73.

[7] AITHAL V, KEI J, DRISCOLL C, et al. Sweep frequency impedance measures in Australian aboriginal and Caucasian neonates [J]. International Journal of Pediatric Otorhinolaryngology, 2015, 79(7): 1024?1029.

[8] 章宇杰,支敏.基于FPGA的DDS实现[J].电子与封装,2013(10):31?32.

ZHANG Yujie, ZHI Min. DDS implementation based on FPGA [J]. Electronics & packaging, 2013(10): 31?32.

[9] 周阳,周美娇,黄波,等.基于C#的串口通信系统的研究与设计[J].电子测量技术,2015(7):135?140.

ZHOU Yang, ZHOU Meijiao, HUANG Bo, et al. The research and design of serial communication system based on C# [J]. Electronic measurement technology, 2015(7): 135?140.

[10] 卜春芬.C#后台处理与多线程技术的应用[J].昆明学院学报,2010,32(3):82?85.

BU Chunfen. The practical application of C# background processing and multi?threading technology [J]. Journal of Kunming University, 2010, 32(3): 82?85.