EtherCAT时钟同步技术的研究*

2018-06-07韩文泽

李 享,何 方,韩文泽

(1.中国科学院大学,北京 100049;2.中国科学院 沈阳计算技术研究所 高档数控国家工程研究中心,沈阳 110171;3.沈阳高精数控智能技术股份有限公司,沈阳 110171)

0 引言

随着工业控制领域对速度、实时性等要求的逐渐提高,传统的现场总线已经难以满足需求,多种实时工业以太网现场总线已经投入使用并得到了日益的重视。其中由德国Beckhoff自动化公司提出的EtherCAT技术,完全符合以太网标准,支持多种拓扑结构,高速、高效率、实时性好,较其他的实时工业以太网现场总线协议有明显的优势,已被广泛应用于工业控制领域。

EtherCAT利用分布时钟机制,在实时性方面具有明显的优势[1-3]。目前很多同步方案中主站选用了实时操作系统,由于主站延时函数误差较大,产生了较严重的丢包现象[4]。本文重点研究了分布时钟技术中嵌入式主站的实现方案,优点在于主站实时性能好、精度高,同时该方案可以直接插入初始化流程中,不影响原有的主站软件。

1 EtherCAT技术原理

EtherCAT数据帧通过特殊的帧类型0x88A4,直接使用以太网数据帧传输,充分利用了以太网的全双工特性[1]。单个以太网帧最多可以进行1486字节的过程数据交换,耗时仅为300μs,100个伺服轴的通讯也仅需100μs,分布时钟技术使得轴的同步偏差小于1μs[2]。如图1所示,在逻辑上,EtherCAT网段内所有从站设备构成一个开口的环形总线[1,5]。主站可直接发送以太网数据帧,并在另一端接收处理后的数据帧。

图1 EtherCAT运行原理

这样设计的好处在于,主站可以轻易地获取从站拓扑结构,精确地测量各从站的传输延时等信息。分布时钟技术即以此设计为基础。

2 EtherCAT分布时钟机制分析

EtherCAT支持的分布时钟机制参考了IEEE1588标准,使得所有从站都同步于同一个时钟,使用相同的系统时间,用来控制各个设备的同步执行。与主站相连的第一个支持分布时钟的从站被用作参考从站,以参考从站时钟来同步其他从站设备及主站时钟[4,6]。

分布时钟初始化时首先需要测量参考从站到其他设备之间的传输延时,同时计算出其他设备时钟与参考时钟之间的初始偏移量,并将其写入各从站。分布时钟初始化流程如图2所示。

主站首先使用APRD命令读所有从站的0x0008~0x0009,获得从站DC特征信息,判断从站是否支持64位或32位分布时钟;读0x0110~0x0111,判断正在使用的从站端口,获得网段拓扑结构。随后主站发送BWR命令,写所有从站0x0900。

图2 分布时钟初始化流程图

综上所述,从站到参考从站的传输延时为:

从站i本地时钟与参考时钟之间的初始偏移量为:

最后,主站使用ARMW命令,读取参考从站的系统时间寄存器0x0910~0x0917,并将获得的当前系统时间τref_local写入其后的从站。主站需要连续发送ARMW数据帧直至同步性基本满足需求(可以通过读系统时间差寄存器0x092C~0x092F来判断是否满足需求)。从站则据此计算自身的时钟漂移量:

Δτ(i)=τlocal(i)-[τref_local+Toffset(i)+Tdelay(i)]

如果Δτ(i)>0,说明从站i的本地时钟运行比参考从站时钟快,ESC控制本地时钟减慢运行;如果Δτ(i)<0,说明从站i的本地时钟运行比参考从站时钟慢,ESC控制本地时钟加快运行[1,10]。

综上可以看出,系统运行后,主站仅需要周期性发送ARMW数据帧实时调整主从站同步情况。因此,控制主站发送ARMW数据帧的时刻对于时钟同步至关重要。

3 EtherCAT主站实时性实现

本文设计了一个EtherCAT系统,并在其上实现了EtherCAT分布时钟。系统结构如图3所示。

图3 EtherCAT系统结构

EtherCAT主站在ARM上实现所有EtherCAT的功能,利用FPGA实现PCI总线接口和DPRAM[11]。主站和人机系统间的交互通过PCI总线完成,主站与从站间通过以太网通信。

为了优化从站同步性能,主站应当保证数据帧先于SYNC0信号一段时间到达从站。从站可以利用这段时间完成数据交换及控制计算,等待SYNC0信号到达后立即执行输出操作。从站的本地周期是由SYNC0信号触发的,为了保证实时性,主站必须使数据帧在SYNC0事件前到达,因此需要保证主站在固定的时间窗口内完成数据帧的发送。

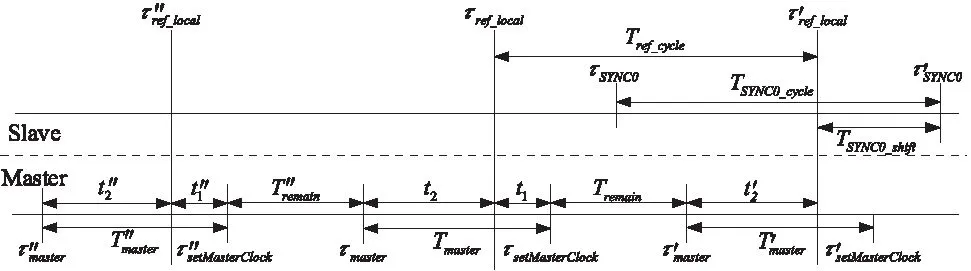

为了达到这一结果,主站需要不断调整自身的定时器,利用主站的本地定时器控制主站发送数据帧时刻,使得从站接收数据帧时刻与从站的SYNC0信号间保持恒定的相位差。主站利用ARM中一组定时器计数器来记录当前时间。为了扩大时钟周期调整范围,计数器的计数上限应该较大。由图4可知,主站应该每个周期计算主站定时器剩余时间,并依据该结果修改主站定时器计数器。

由图4可知,主站定时器的剩余时间为:

综上,需要设定的主站定时器计数器的值为:

其中,Tmax为计数器的计数上限。主站实际上执行Tremain后触发中断,进入下一次定时器事件,与Tmax的大小无关。

图4 分布时钟的主从站通信时序

4 测试结果分析

测试平台如图5所示,采用1个主站6个从站,所有从站均支持分布时钟,即以1号从站为参考从站。

设定SYNC信号周期为2ms,SYNC0偏移为500μs。通过采集参考从站周期运行开始时间寄存器(0x0990)、本地系统时间寄存器(0x0910),计算二者的差值,就可以知道实际的SYNC0偏移。测试结果如图6所示。

图5 分布时钟测试平台

图6 参考从站的实际SYNC0偏移

由图6可以看出,实际上SYNC0偏移分布在500μs上下,且抖动不大。通过示波器采集参考从站接收ARMW数据帧时刻、SYNC0信号发生时刻也能得到相同结论。如图7所示。

图7中的抖动范围为5.46μs,SYNC0偏移则稳定分布在490μs左右。这与ESC缓存模式有关。主站数据帧到达从站后,首先写入由存储同步管理通道(SyncManager,SM)管理的三个缓存区中的第一个。写成功后,会在SM状态寄存器中设置中断事件请求。这一模式会使中断发生时刻比真实接收数据帧时刻偏晚,导致了测得的SYNC0偏移偏小。

主站选用了实时操作系统的同步方案,通常通过增加系统延时来调整主站发送数据帧的时间[4]。这种方案使用的延时函数通常误差较大时钟分辨率往往在百微秒量级,导致SYNC0抖动范围大。当延时过长时,主站会在SYNC0信号产生后发送数据帧,从站不能处理而频繁产生丢包。本方案直接调整主站定时器计数器,在主站时钟频率为204MHz的情况下,系统时间的分辨率仅为4.9ns,SYNC0抖动范围很小。由图7可以看出,主站可以保证在SYNC0事件前完成数据帧的发送。实际测试中,系统长时间连续运行,未出现丢包现象。可以认为主站实时性的需要得到了保证。

图7 参考从站收帧与2号从站SYNC0信号发生时刻

用示波器采集参考从站和2号从站的SYNC信号发生时刻,如图8所示。图中可以看出,两个从站的SYNC发生时刻的误差在30ns以下,SYNC信号的抖动范围为16.2ns。可以认为从站的同步性得到了保证。

图8 参考从站与2号从站SYNC0信号发生时刻

针对不同SYNC信号周期(2ms、3ms、5ms、10ms),系统进入运行阶段后,每60个周期采集一次2号从站的系统时间差寄存器的值。对于每组采集到的2000个数据,去除符号位后,统计结果如表1所示。

表1 不同时钟周期下2号从站系统时间差寄存器值的统计结果

从表中可以看出,在一定范围内,无论时钟周期如何变化,从站的时钟平均误差都在同一区域内。但是如果时钟周期变大,从站时钟的误差抖动也会增大。这是因为在下一次同步前,从站独立运行的时间变长了,与参考时钟出现较大误差的机率也提升了。所以主站的时钟周期应当尽可能小。

为了验证发送ARMW数据帧的时间间隔对时钟同步的影响,将主站改成每周期发送2次ARMW数据帧。在4ms的时钟周期下,采集2号从站的系统时间差寄存器的值,与2ms同步1次的结果进行对比。对比结果如表2所示。

表2 2ms同步1次与4ms同步2次下2号从站的系统时间差寄存器值的统计结果对比

与2ms同步1次相比,4ms同步2次在同步的频率上是一致的。但是发送ARMW数据帧的时间间隔会随传输时间的变化而变。从表中可以看出,4ms同步2次时误差的平均值与波动都变大了。这表明,发送ARMW数据帧的时间间隔的稳定性对同步效果影响较大。所以主站应当尽可能保证发帧间隔的稳定。与主站选用了实时操作系统的同步方案[4]相比,本文提出的方案在发帧间隔的稳定性上有明显的改善,能够获得更好的时钟同步效果。

5 结束语

本文基于ARM平台,重点对EtherCAT时钟同步机制进行了研究,详细探究了主站保证实时性的实现方案,并进行了仿真测试。测试结果证明了该方案下EtherCAT时钟同步的误差满足实时性的需求。同时,测试了SYNC信号周期、发送ARMW数据帧的时间间隔的稳定性对时钟同步效果的影响。对进一步优化主站同步方案有重要意义。

[参考文献]

[1] 郇极,刘艳强.工业以太网现场总线EtherCAT驱动程序设计及应用[M].北京:北京航空航天大学出版社,2010.

[2] 樊留群.实时以太网及运动控制总线技术[M].上海:同济大学出版社,2009.

[3] CENA G, BERTOLOTTI I C, SCANZIO S, et al. Evaluation of EtherCAT Distributed Clock Performance[J]. IEEE Transactions on Industrial Informatics,2012,8(1):20-29.

[4] 刘辉.高速工业以太网时钟同步技术的研究[D].深圳:哈尔滨工业大学,2014.

[5] ETG.1000.4S(R)v1.0.2,EtherCAT Specification-Part 4:Data Link Layer protocols specification[S]. 2013.

[6] 李启宗,周侗.一种面向运动控制领域的时钟同步算法的分析与NCNET网络实现[J].仪器仪表学报,2010,31(S2):198-201.

[7] 戴俊良,王文格.EtherCAT网络控制中从站间传输延时研究[J].工程设计学报,2014, 21(5):494-498.

[8] 胡国传,沈杰,刘彬,等.基于PROFINET IO的延迟和抖动研究[J].仪器仪表学报,2011, 32(9):2153-2160.

[9] 汪雅楠,谭南林.EtherCAT时钟同步的误差仿真分析[J].自动化技术与应用,2011, 30(7):22-26.

[10] ORFANUS D, INDERGAARD R. Recovery of distributed clock in EtherCAT with redundancy for time-drift sensitive applications[C]//Emerging Technology and Factory Automation. IEEE, 2015:1-4.

[11] 陈灏,宋宝,唐小琦.EtherCAT精确时钟同步技术的实现[J].组合机床与自动化加工技术,2014(5):69-72.