一种低功耗数据路径综合的迭代改进算法∗

2018-05-29潘锋

潘 锋

(四川信息职业技术学院 广元 628040)

1 引言

低功耗是超大规模集成电路(VLSI)设计的重要指标[1]。在电力消耗中最节省的往往是在更高层次的设计中[2]。本文将重点放在行为合成过程中,将其作为一个设计的行为描述,并生成一个实现指定行为的寄存器传输级(RTL)电路[3]。行为综合可以细分为几个任务,包括模块选择、时钟选择、调度和分配。其中,这些任务相互作用,单独解决每个任务可能会影响设计的质量。文献[4]中给出了动力优化方面的开拓性工作,它使用数据路径复制和流水线来支持电源电压伸缩。文献[5]中提出了使用多种变换来降低功耗的方法。同时,正确的模块选择[6]、调度和分配[7~8]也被利用在电力消耗减少中。虽然上述所有方法都执行了一些行为合成任务的子集,通过减少供电电压或减少开关电容来降低功耗,但很少有人考虑各种任务的相互作用所涉及的权衡。

本文提出了一种用于低功耗数据路径合成的迭代改进算法,该算法执行调度、时钟选择、模块选择和资源分配,目标是减少功耗。并且它可以同时执行这些任务,从而探索这些任务相互依存性。

2 理论基础

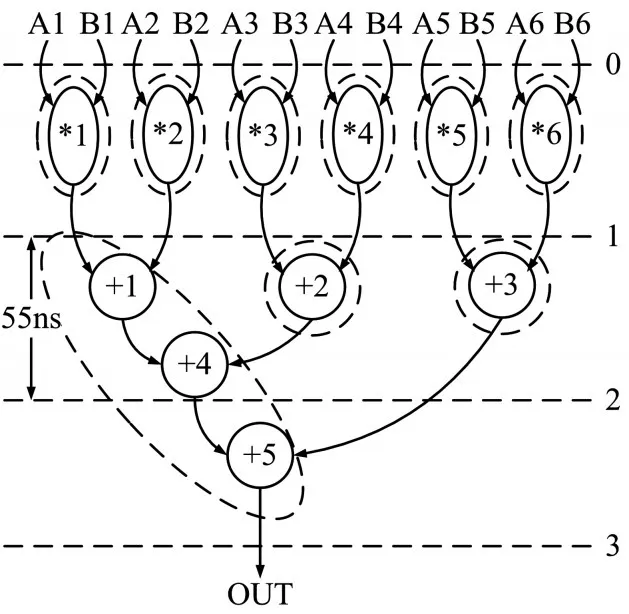

行为描述可以编译成一个控制数据流图(CD⁃FG),它是一个有向图,由算术、逻辑、比较操作、延迟操作符、特殊的分支、合并、循环入口和出口组成顶点,它们代表控制流结构[9]。CDFG包含数据控制,它表示数据控制操作之间的关系[10]。图1中所示的CDFG为两个向量点积的计算。

图1 CDFG时间表与任务的点积计算

在本研究中数据控制的行为描述在数字信号和图像处理应用中是很常见的。这些描述的两个重要特征是:1)它们主要包括算术运算,如加法、乘法和延迟运算符等[11];2)输入采样周期的约束在下一次输入样例到达之前处理输入的速度是固定的,但是处理输入样本的速度并不比要求的速度快[12]。

平均开关电源在CMOS技术的中占主导地位的功耗为

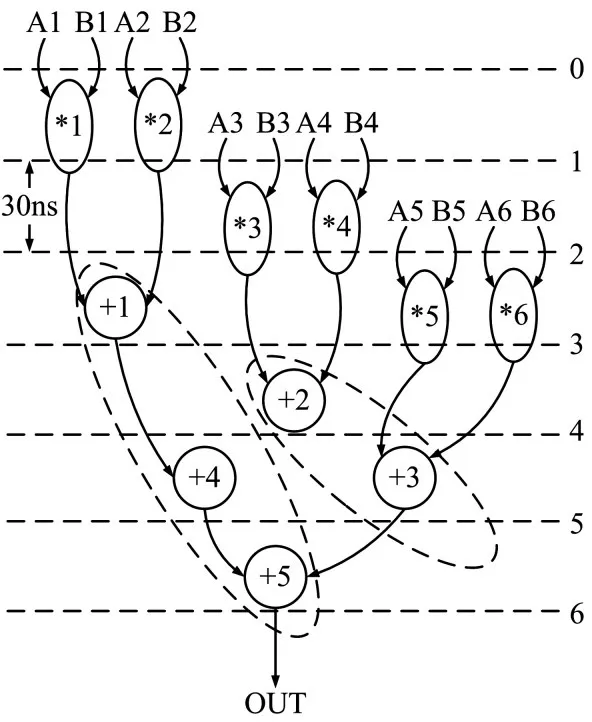

其中,CL为门电路输出电容,Vdd是电源电压,N是周期T操作期间门输出的过渡数,电力消耗方程表明,由于其二次贡献[13],供电电压Vdd对功耗有很强的影响,与此同时,电路的延迟会增加。CMOS的门延迟可以表示为

其中,Vth为设备的阈值电压,k是依赖于栅极技术和晶体管尺寸的常数。因此,只有当延迟降级不会导致延迟超过指定的约束,或者使用其他方法来防止延迟降级时,才执行Vdd扩展。物理电容CL和过渡活动N的乘积称为交换电容,开关电容项的影响虽然不像供应电压那样剧烈,但也可以用于降低功耗。

2.1 调度操作

调度过程决定了CDFG的循环周期行为,它将CDFG中的每个操作分配给一个或多个周期进行控制步骤。图1显示了示例CDFG的进度信息。标记为数字的水平虚线表示时钟的边缘,即控制步骤之间的边界。其中,+4将与+1、+2相同的控制步骤中执行,且时钟周期为55ns。这种链锁技术[14]使得“多环”进行一种互补的模式,即单个操作需要多个控制步骤来执行。结构流水线指的是在数据路径中使用流水线执行单元。显然,时钟周期的选择影响到操作的控制步骤分配,而在CDFG中每个操作的延迟也是如此。这些值分别由时钟选择和模块选择任务决定,在调度、模块选择和时钟选择之间建立相互依赖关系。在同一控制步骤中活动操作(变量)必须分配给不同的功能单元(寄存器)。例如,操作*1到*6必须由独立的功能单元来执行。由于调度影响了处理输入样本的速率,且也影响了减少Vdd的可能性。另一方面,调度影响交换电容,因为它限制了资源共享的可能性。

2.2 模块选择

模块选择指的是在CDFG中选择每一项操作的过程,即执行它的功能单元类型。为了充分探索设计空间,需要有不同的功能单元模块库存在多个模块能够执行每个操作(例如脉冲进位加法器、超前进位加法器,选择加法器和阵列乘法器等[15])。

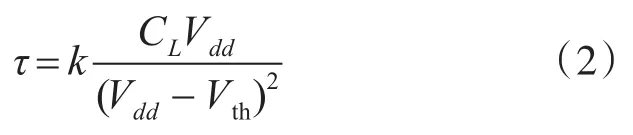

通过使用模块选择来执行区域、延迟和功率三者间的关系。模块选择与时钟选择、调度和资源共享交互。在图2中,由于模块选择被改变,时钟周期也改为30ns。在模块选择期间被分配给不同功能单元的操作不能共享相同资源。本研究的算法将考虑交互作用的影响,并且综合数据路径。

图2 备用调度分配模式

2.3 时钟选择

时钟选择是指控制器/数据路径电路选择合适的时钟周期过程。时钟周期Tclk,本文将CDFG的执行时间等同于输入采样周期Ts,时钟周期为Tclk时,控制步骤的数量为

其中,表示小于或等于x的最大整数。选择时钟周期后,根据控制步骤计算各功能单元模块的延迟。

由于时钟粒度在松弛因子的作用下可能会小于功能单元而被完全利用[16],这将导致CDFG执行所需的时间增加。在最大限度地减少功耗的情况下,松弛的时钟粒度可以引起两种不良影响:1)样本周期不能满足CDFG对Vdd的约束;2)导致具有更高开关容量的数据路径。因此,从能源消耗的角度来看,在降低功耗时,单一目标松弛最小化的方法不能直接适用。为了降低功耗,在选择时钟周期的情况时,要尽量减少时钟粒度的松弛性

2.4 资源共享

资源共享是指使用相同的硬件资源(功能单元或寄存器)执行不同的操作或多个变量存储。资源共享严重影响功耗数据路径中的电容和开关活动。其中,资源共享倾向于减少物理电容,但增加了数据路径上的平均切换活动。稀疏共享架构的平均开关活动较低,但物理电容较高。本研究使用资源共享对开关电容信号统计的影响。

假设库中的函数单元具有切换电容的一些模型,因此,给定一对输入向量可以计算出功能单元中交换的电容。这个过程可以使用随机功率分析模型来实现。由用户提供或者根据已知的输入特性生成输入序列对CDFG进行功能模拟。在执行功能模拟时,使用CDFG中变量所取的值更新交换电容矩阵的数据结构。其中,交换电容矩阵将交换电容成本与可映射到同一资源的每一对操作相关联,并为其在库中的每个功能单元模块创建一个单独的切换电容矩阵。同时,还要考虑功能单元模块、波纹进位加法器和加法运算的综合作用。

3 改进算法

利用调度、时钟选择、模块选择和资源共享进行一种复杂的方式交互,以确定数据路径的功耗。由于功耗最小化问题的计算复杂且不易得到最优解或精确解,因此,本研究开发一种有效的启发式方法用于执行上述任务,以最大限度地减少功耗,目的使得Vdd扩展和交换电容减少。利用程序估计最小电压Vmin,并由用户设置Vmin和Vmax(5V)之间的电压间隔△V。对于Vdd和电子密度图CSTEPS的组合生成一个满足样本周期约束的初始值,通过调用迭代改进算法对数据路径进行合成,目的是在当前Vdd和时钟周期内合成满足采样周期约束的数据通路,并且具有最小的开关电容。在所有候选电源电压和时钟周期被修正后,最优方案Best_DP包含最终的解决方案。低功率合成方法记作SCALP。

3.1 电源电压修正

电源电压Vdd修正的目的是识别出候选供应电压,这不会导致数据路径的最低功率。本文所使用的Vdd修正方法是基于对当前Vdd的交换电容约束。通过将CDFG中的每一个操作映射到具有最低开关电容的功能单元模块,并执行模块选择完成并行架构来实现数据路径。由于并行架构通常接近最低的开关电容结构,因此计算过程中通常乘以一个修正系数λ(0≤λ≤1)来降低当前Vdd中数据路径所消耗的能量,在本文中使用了λ取0.8。如果这样计算的界限大于最好的解决方案,那么可以对当前的Vdd进行修正。

3.2 时钟周期修正

给定一个理想的采样周期Ts,对于时钟周期Tclk满足如下条件:

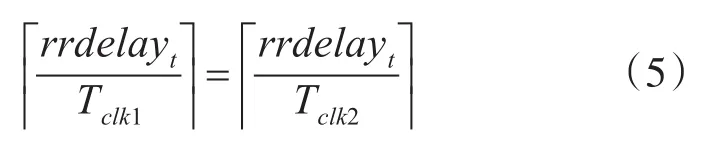

将候选时钟周期的集合限制在有限的集合中,考虑两个候选时钟周期Tclk1和Tclk2,使得Tclk1<Tclk2。对于数据路径库中的每个功能单元模块t,令rrdelayt表示寄存器之间的传输延迟,则

如果操作链接采用最大链接系数k,则式(5)计算的条件不仅对所有功能部件模块适用,也可用于所有链接到k功能单元的组合模块。

4 实验分析

本文使用C++编程语言实现研究中所描述的SCALP方法。利用该方法从数字信号处理方面对SCALP进行综合评价。SCALP输入初始化CDFG和样本周期,输出数据路径和控制器以共同实现CDFG所指定的行为。用于组合控制器和数据路径的网表使用逻辑合成工具SIS将其映射到MSU标准单元库中。最后使用OCT软件中的标准单元格布局和路由工具来获得组合控制器和数据路径的布局。Switch模拟器在模拟运行过程中记录交换电容,并用来执行布局中提取的交换机模拟。

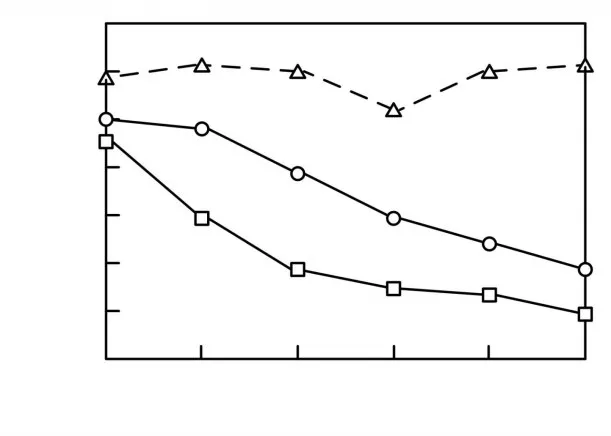

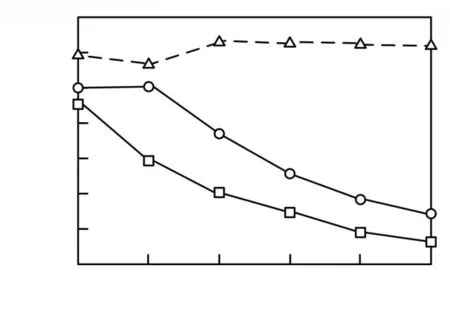

将每个基准对应从1.0~3.5的松弛因子各种可能值。对于每个基准和松弛因子,由SCALP生成的能量优化体系结构,通过Vdd扩展的优化架构,使用与SCALP相似的方法进行区域优化。每个供应电压的优化体系结构按样本周期约束程度进行伸缩。由SCALP计算的控制器和电路数据路径产生消耗的功率,见曲线S-POWER。Vdd放缩区域优化架构,见曲线A-POWER。由SCALP生成的控制器和数据路径合成布局区域,见曲线S-AREA。三者的对比如图3和图4所示。

图3 利用WDF滤波器进行实验

图4 利用Elliptic滤波器进行实验

在图3和图4中,WDF是一种数字FIR滤波器。Elliptic是一种五阶椭圆滤波器。面积曲线用虚线绘制,功率曲线用实线绘制。曲线表明:由SCALP合成的电路比优化电路的功率低7倍,电路消耗的功率比优化后的功率低2.3倍,且合成电路的开销小于41%。从数值的平均角度观察,在松弛因子分别为 1.0、1.5、2.0、2.5、3.0和 3.5条件下,SCALP计算出的数据路径占区域面积分别为16%、24%、27%、24%、27%和27%。在128MB内存的SPARC上,CPU运行SCALP的时间小于20分钟。

5 结语

本文从调度操作、模块选择、时钟选择和资源分配四个任务对数据控制行为进行了描述,并以减少电力消耗为目的,提出了一种高效的迭代改进算法。与之前的研究不同,本文还考虑了这些任务之间的交互作用,通过修正电源电压和时钟周期两个因素,改进了交换电容产生功耗的数据路径计算,实验结果证明了算法的有效性。

参考文献

[1]庞志勇,谭洪舟,陈弟虎.一种改进的低成本自适应双三次插值算法及VLSI实现[J].自动化学报,2013,39(04):407-417.

[2]朱文兴,程泓.VLSI电路划分问题的分散搜索算法[J].电子学报,2012,40(06):1207-1212.

[3]李艳,张东晓,于芳.RTL综合中FPGA片上RAM工艺映射[J].电子学报,2016,44(11):2660-2667.

[4]张露予,王博文,翁玲,等.螺旋磁场作用下磁致伸缩位移传感器的输出电压模型及实验[J].电工技术学报,2015,30(12):21-26.

[5]林志堂,郭昌坚,张朋涛.无线通信技术的低功耗处理技术研究[J].机电工程技术.2017(02):209-212.

[6]杜世民,夏银水,黄诚,等.一种有效的面向软模块的VLSI布图规划算法[J].计算机工程与应用,2014,50(04):50-56,68.

[7]陶钧,仇悦,沈海斌.传感器网络中图像小波处理的低存储硬件实现[J].传感器与微系统,2013,32(09):16-20.

[8]路伟,余宁梅,南江涵,等.并行可配置的HEVC熵编码的 VLSI结构[J].计算机工程与应用,2014,50(03):121-124,144.

[9]朱小茹,王兴伟,张爽,等.基于SDN和接触图的空间信息网络路由机制[J].计算机科学与探索,2017(08):1-8.

[10]张骏,陈实,郭岳东.基于Honeypot主动防御系统的数据控制设计[J].电脑与信息技术,2014,22(04):25-28.

[11]Sengupta A.Soft IP Core Design Resiliency Against Ter⁃restrial Transient Faults for CE Products[J].IEEE Con⁃sumer Electronics Magazine,2016,5(4):129-131.

[12]张珠庭.云计算数据控制层数据库模型与节点构建研究[J].数字技术与应用,2013(12):39-40.

[13]赵轩.基于二叉树算法数据控制层数据库模型构建[J].计算机光盘软件与应用,2013,16(19):157-158.

[14]McIVER W R,CARTER H R,HARVEY A L,et al.Use of social attraction to restore Ashy Storm-Petrels Oceanodroma homochroa at Orizaba Rock,Santa Cruz Is⁃land,California[J].Marine Ornithology,2016,44:99-112.

[15]姚茂群,张立彬,耿亮.电流型CMOS脉冲D触发器设计[J].电子与信息学报,2014,36(09):2278-2282.

[16]陈锐,杨海钢,王飞,等.基于粗粒度可重构阵列结构的多标准离散余弦变换设计[J].电子与信息学报,2015,37(01):206-213.