多路光纤传输中的数据处理与时序控制研究

2018-05-23孔文青李紫航宋万杰

孔文青,李紫航,宋万杰

(西安电子科技大学 雷达信号处理国家重点实验室, 陕西 西安 710000)

数字相控阵雷达因为由多个阵列天线组成使其具有多波束形成的能力,能够实现多目标搜索、跟踪,完成空时自适应处理、自适应空间滤波等功能,以及出色的抗干扰能力,因而得到广泛的应用[1]。而光纤是现代通信网络中传输信息的最佳媒介[2-3],因此,光纤传输已经成为数字相控阵雷达通信系统中的主体。

一方面,数字相控阵雷达要求传输数据的通道数多、数据量大;另一方面,基于FPGA的多路数据处理过程时序复杂、控制难度大,会导致多路数据传输不同步且不稳定[4-6],所以对多路光纤传输中的数据处理与时序控制进行研究具有重大的意义。该研究不仅可以使多路雷达回波数据同步稳定的发送至信号处理系统进行后续处理,还可使相应数据准确无误的发送至采集系统进行存储。

本文以多路雷达回波数据采集系统为研究对象,利用10根光纤将40路经雷达天线接收到的回波数据下传至DDR进行乒乓缓存[7-8],再对数据结构调整后通过PCI稳定无误的存储到上位机硬盘[9-10],整个数据传输过程利用FIFO组完成数据处理与时序控制。

1 多路雷达回波数据采集系统架构

多路雷达回波数据采集系统架构如图1所示。

在图1的系统中共有10根光纤,每根携带4路I、Q交替的雷达回波数据进入光纤接口[11];标注1的流程表示,FPGA对40路16位的数据进行处理与时序控制,转为1路位宽256位的数据并乒乓缓存至两片DDR芯片;标注2的流程表示,从DDR中乒乓读出先前缓存的数据,经FPGA进行数据处理和时序控制转为1路高16位为I,低16位为Q的32位数据,保证原40路数据经PCI可交替存储至硬盘。其中,光纤传输的数据格式为:

……

图1 多路雷达回波数据采集系统架构图

2 基于FPGA的数据处理与时序控制设计

2.1 多路光纤与DDR间的同步时序控制

高速光纤通道数据是通过光纤模块,将光信号转换为电信号传输的[12-13]。多路光纤传输时,由于每路信号光电转换过程不能保证完全一致、PCB布局布线存在差异、外界影响等因素,导致光信号传输时间不同,因此通过控制多路光纤使数据同步且平稳无误传输尤为重要。

根据多路雷达回波数据采集系统的应用要求,结合Altera公司的光纤IP Core设置特点[14],这里将Channels数量设置为10,Deserializer Block Width 设置为Double, 每个光纤通道传递的数据位宽为16,且设置好其它的控制信号后可以得知,每路光纤都有独立的时钟、控制检测信号、错误检测信号等。

2.1.1 光纤到DDR的同步时序控制

多路光纤作为输入接口,考虑到温度和电压波动容易造成输入阻抗变化,并且多路光纤之间容易存在扰动,本文引进高级片内匹配(OCT)技术,在FPGA的Assignment Editor中添加 OCT 100 Ω对光纤的Input Termination进行约束,以达到多路光纤数据稳定输入的目的。

另一方面,由于DDR要求位宽为256位的数据作为输入,所以为了充分利用DDR存储空间且读写方便,光纤与DDR间添加FIFO组完成跨时钟域转换和数据结构转换,如图2所示,此做法使多路光纤不同步问题得到良好的解决。

图2 光纤到DDR间FIFO组

图2中共10个Fiber_FIFO,即每个光纤通道对应1个。Fiber_FIFO的写数据即为每路光纤位宽为16的传输数据,写使能由每路光纤位宽为2的接收控制检测信号或非得到,Fiber_FIFO的读使能由乒乓DDR的写使能控制,读时钟为DDR的工作时钟phy_clk,读出的数据拼成160位且高[255:160]位补零之后乒乓缓存至DDR,该设置说明原10路并行的16位光纤数据经FIFO组转为了1路160位数据。

为了验证数据的正确性和稳定性,数据乒乓缓存至DDR的同时也将被送到数据检错模块,其中,检错步骤如下:

步骤1将多路光纤输出的理论数据缓存至RAM区;

步骤2传输数据被送入数据检错模块的同时读取相应RAM值;

步骤3传输数据与理论数据进行异或,完成比较操作。若结果error=0则表示数据传输正确,反之,错误。

在SignalTap仿真工具触发error信号状态下,经30 min循环测试,error信号没有拉高,由此可以得出结论,以上设计方法可使多路光纤数据同步且平稳传输。

2.1.2 DDR到光纤的同步时序控制

为了更好的研究多路光纤数据传输的过程,本文也将10路光纤作为输出端进行了研究和设计,其中,10路光纤传输的数据相同,且循环传输AA55 55AA BB44 44BB CC66 66CC DD77 77DD 0001 0002 0003 …… 00FF。

由于DDR读出的数据为256位的数据,低160位有效。一般情况下,为了达到数据对齐的目的,将该160位的数据经一个FIFO完成跨时钟域和数据缓存,然后用和光纤时钟频率相同的时钟从FIFO中读出数据,再每16位分配给一根光纤,完成多路光纤的传输。

以上设计方案虽然看似简单,但却会因为时钟不匹配造成多路数据传输不稳定,SignalTap采到光纤接收端数据检错模块的error信号会立即拉高。通过分析相应数据可知,该数据大多出现了移位现象。

为了避免上述问题的发生,应对DDR读出的160位数据以每16位为一组写入对应的FIFO,组成DDR到光纤的FIFO组。每个FIFO的读时钟为每路光纤所对应的tx_clkout[x],读使能根据实际情况中的数据接收要求由该tx_clkout[x]产生。以光纤1的传输为例,其仿真结果如图3所示。

图3 光纤1的传输过程仿真图

上面 SignalTap仿真图的采集时钟为tx_clkout[0],其中tx_datain[15:0]代表将要传输到光纤1的数据,pule0作为光纤1的触发信号由对应FIFO的读使能产生。可以看出,触发信号拉高的下一个时钟光纤数据开始发送,符合光纤发送数据要求,且数据与要求发送的光纤数据保持一致。其次,在SignalTap触发光纤接收端数据检错模块的error信号状态下,对每路光纤数据经30 min循环测试,error信号都没有拉高,所以,在DDR到光纤间添加FIFO组保证了多路光纤数据传输的同步与稳定。

2.2 DDR到PCI的多路数据处理与时序控制

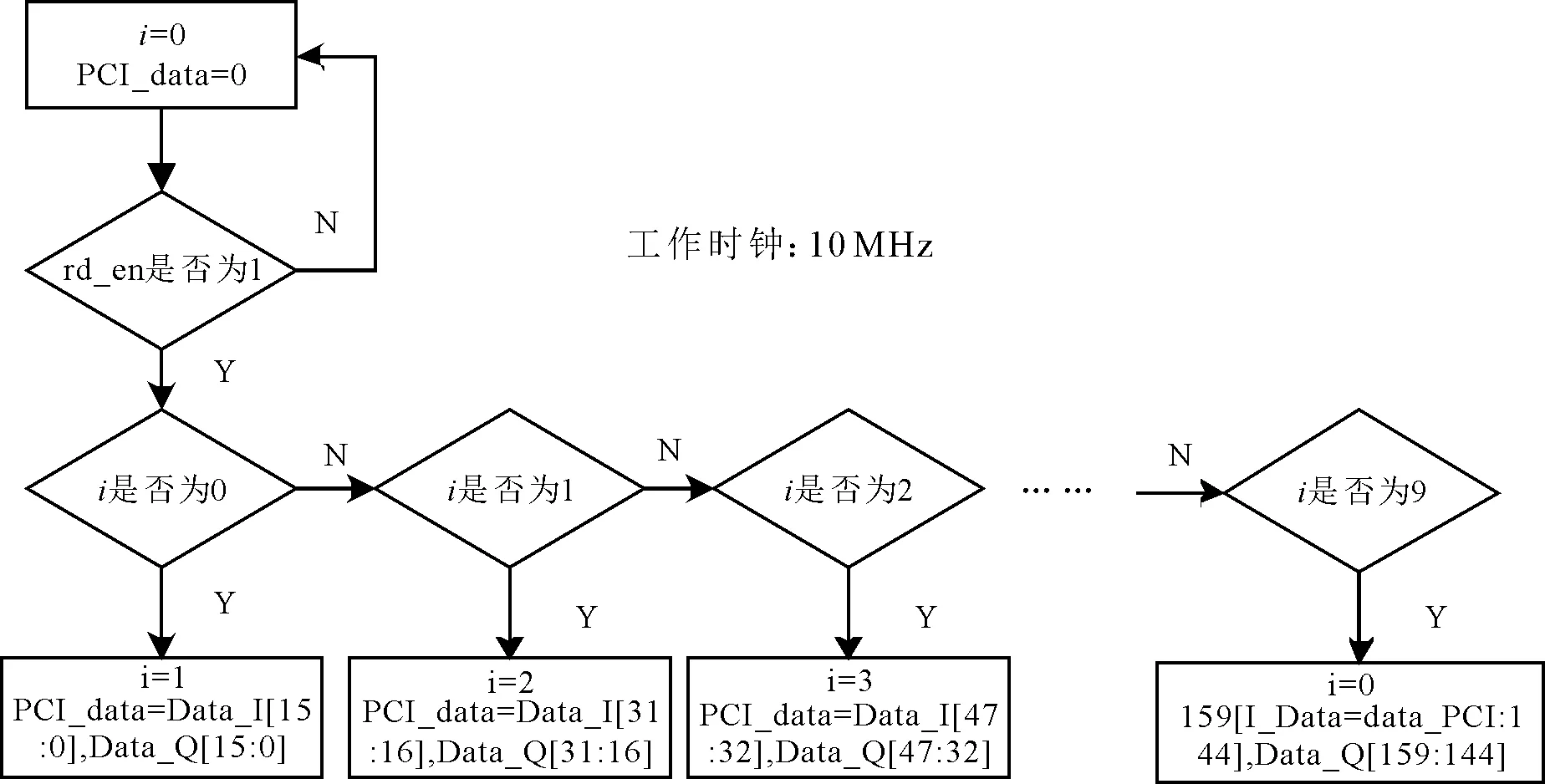

为了使40路雷达回波数据能以高16位为I,低16位为Q的格式交替存储至硬盘,常用方法是:将DDR读出的160位数据乒乓缓存至两个FIFO;然后用1 MHz时钟从FIFO中同时读出,写作Data_I[159:0],Data_Q[159:0];经数据拼接模块再以10 MHz时钟将位宽32位的数据送至PCI接口前的缓存FIFO;最后完成数据存储过程,数据拼接流程如图4所示。

图4 数据拼接模块流程图

一般来说,图4中的读使能rd_en受PCI接口前的缓存FIFO的空满信号控制,也就意味着产生空满信号的时钟只能有两种情况,一种是10 MHz,一种是PCI接口时钟33 MHz[15],而这两种时钟并不能与使用rd_en的时钟clk_1M相匹配。所以采用以上设计方案来转换数据格式,不仅因为引入1 MHz和10 MHz两个时钟而使电路变得复杂,还使控制使能变得困难,导致数据传输不稳定。

为了解决上述问题,本文在DDR与PCI间添加FIFO组模块完成跨时钟域转换和数据结构转换,如图5所示。

采用状态机实现DDR_FIFO的读写控制,图6(a)为DDR_FIFO写使能状态机,该状态机严格控制在phy_clk时钟域。图6(b)为DDR_FIFO读使能状态机,该状态机严格控制在PCI接口的工作时钟clk_33M时钟域。

如图5所示,将原本位宽160的数据划分为10个16位的数据分别缓存入对应的DDR_FIFO,又在图6的状态机转换形式下产生DDR_FIFO的写使能和读使能,使DDR_FIFO分为数据I组和数据Q组,其仿真结果如图7所示。

从图3和图4可以看出0001h为I,0002h为Q,为方便研究,本文将光纤输出直接与光纤输入连接。其次,如图7所示,将rd_en_reg作为状态选择信号,在其对应状态下分别把data_a,data_b,……data_j赋值给PCI_data[31:0],则从图中可以看出,10路光纤数据都为00010002h,所以得出结论,在DDR与PCI间添加FIFO组模块可以使40路雷达回波数据能以高16位为I,低16位为Q的格式交替存储至硬盘,同时,通过读取硬盘中的数据可知,该方法可以保证数据准确无误,所以,该方法不仅实现了数据格式的转换,还解决了时序不稳定的问题。

图5 DDR与PCI间FIFO组模块

图6 DDR_FIFO写、读使能状态机

图7 经DDR与PCI间FIFO组模块后的数据仿真图

3 结束语

多路光纤传输接口是高速、复杂而严格的控制逻辑和时序接口,要正确实现需要非常细致的工作。利用设置FIFO组以及控制相应的读写使能,完成多路光纤数据的同步与数据结构的改变,避免了因数据要求而引入复杂时序建立数据转换模块导致时序错乱、数据不稳定等问题。FIFO组可保证读写使能、数据和读写时钟同源,避免跨时钟域导致传输不稳定的问题发生。

参考文献

[1] 陈伯孝. 现代雷达系统分析与设计[M].西安:西安电子科技大学出版社, 2012.

[2] 马向玲,杨辉,王海玲,等. 基于FPGA的多路数据光纤传输系统设计与实现[J]. 计算机测量与控制, 2011,19(2): 363-366.

[3] 杜建华,瞿海娜. 基于光纤通道的数据采集系统设计[J]. 电子技术设计与应用, 2013(6): 41-43.

[4] 候朝勇,胡学浩,庄童. 基于FPGA的多路同步实时数据采集系统[J]. 电子技术应用,2009 (10): 168-171.

[5] 韩西宁,许晖,焦留芳. 基于FPGA的同步数据采集处理系统的设计与实现[J]. 电子技术应用, 2009(1): 89-91.

[6] 杨隆梓,段星辉,魏焕东,等. 基于FPGA的多通道同步数据采集系统[J]. 科学技术与工程,2008, 8(6): 1466-1469.

[7] 马灵,杨俊峰,宋克柱,等. 地震数据采集中基于FPGA的多DDR SDRAM控制器设计[J]. 中国科学技术大学学报, 2010.40(9): 939-945.

[8] 王淑静,史忠科. 乒乓缓存及其在DSP视频实时处理系统中的应用[J]. 工业仪表与自动化装置, 2008(1): 42-45.

[9] 胡菲,卢益明. 基于FPGA的PCI接口控制器设计与实现[J]. 电子科技,2002(4): 34-37.

[10] 马鸣锦,朱剑冰,何红旗,等. PCI、PCI-X和PCI Express 的原理及体系结构[M]. 北京: 清华大学出版社, 2007.

[11] 孙高俊,刘志英. 基于FPGA的雷达IQ光纤数据采集及传输系统[J].电子科技,2016,29(4): 169-172.

[12] 刘志英,孙高俊,吴关.光纤传输技术在雷达信号记录重演系统中的应用[J].电子科技,2012, 25(3):104-106.

[13] 吕迎春,谭庆贵,谢军,等. 光纤通道数据采集存储系统设计与实现[J]. 航空电子技术,2014.45(3): 17-21.

[14] Alter Corporation. Stratix IV device handbook 2012[M]. TX,USA: Altera Corporation, 2012.

[15] Mohit Arora. 硬件架构的艺术—数字电路的设计方法与技术[M].李海东,来萍,师谦,等,译.北京:机械工业出版社, 2014.