一种基于FPGA的PCM检查器的实现

2018-05-17单文军罗霄李文华

单文军,罗霄,李文华

(西安远方航空发展技术总公司陕西西安710089)

航空遥测技术是融合了传感、采集、通信和数据处理为一体的综合技术,覆盖了飞行试测试中的机载测试、遥测传输、数据处理等环节,在飞行测试领域具有重要的作用和地位,数据检测的准确性,直接决定了遥测信息的质量[1-3]。当前,我国航空事业的高速发展,视频图像测量在飞机试飞中的得到了广泛应用,航空遥测数据的传输速率已接近10 Mb/s,甚至更高,这些急剧增加的数据量对检测设备提出了更高的要求[4-5]。PCM(脉冲编码调制)检测就是为了确保数据检测的准确性,其将连续的模拟信号转化为可处理的数字化信号,便于计算机进行处理。然而,飞机上传统的机载PCM数据流检查均需通过PCMCIA转接卡与笔记本电脑连接才能完成检测,造成使用不方便,成本高[6-8];为提高科研试飞效率,迫切需要能够实时检查前级设备输出的高速PCM数据且方便与PC机通讯的新型PCM数据流便携式检查设备。

针对上述问题,文中研制了一款新型PCM数据流检查设备,支持可编程选择的PCM帧格式与输入码型(NRZ-L、NRZ-M、BΦ-L、BΦ-M),其采用FPGA(现场可编程门阵列)来完成高速PCM数据的接收和同步。同时,采用USB通信接口,将检测到的数据发送到上位机上,即插即拔,方便大量存储,并且支持实时回看。并通过上位机软件便携支持实时回看,完成了位速率最高可达10 Mb/s的小型化、高可靠、便携式PCM数据流检查器。

1 PCM数据流检查器系统设计

1.1 系统设计思路

PCM能够将连续模拟的信号通过抽样、量化、误差化和编码等环节变换成离散的数字信息[9],是这款检查器的研制的理论依据。在本设计中,系统的设计思路如下:PCM数据流检查器将采集来自前端的PCM数据流发送设备,在FPGA内部进行PCM数据流的同步与缓存后,数据通过USB2.0传输到上位机进行检测。PCM数据流检查器由硬件设计与上位机软件设计两部分组成,硬件部分依据事先编程好的帧格式及同步信息,完成了串行PCM数据的接收、同步和缓存,并通过USB2.0发送至PC机。用户则可以直接通过上位机软件观察数据信息。

1.2 系统设计

根据以上设计思路,结合设计和实践经验,设计了PCM数据流检查器的总体设计框图,如图1所示。

图1 PCM数据流检查器总体设计框图

PCM数据流检查器主要由7部分构成:差分转单端模块、串并转换模块、同步字检测模块、时钟生成模块、主控模块、USB2.0控制器模块以及上位机模块。检查器接收具有一路PCM数据和一路位时钟的差分信号,通过差分转单端芯片转换为一路数据信号和一路时钟信号;外部SRAM从FLASH中读取用户所配置的同步检测模块信息,通过串并转换后的并行数据在检测成功后发往FIFO进行数据缓存;同时,把缓存到的并行数据通过USB2.0控制器发往上位机中,方便用户检查数据。

2 PCM数据流检查器硬件设计

2.1 基于FPGA系统硬件设计实现

由系统整体设计可以看出,同步字检测[11-12]是PCM数据检查器的核心,根据同步字、子帧计数和全帧计数,将输入的并行数据和FLASH中寄存定义的预置同步信息进行比较,当发现输入数据中有同步字且与预设值相同时将设置其状态位,并且同时发送状态标志位给主控模块。通过以上同步字检测和子帧长度检测,则认为该数据流同步,然后将同步标志位发送至FIFO缓存,使其做好发送数据准备,同时向上位机发出做好发送数据准备的指令,最后将数据通过USB2.0控制器送往上位机进行显示。

在充分考虑成本和满足设备工作的前提下,本次设计的FPGA芯片选取的是Altera公司的EP3C40F324C8芯片,其具有丰富的硬件资源,外围硬件电路包括SRAM、USB2.0控制器、电平转换芯片等[13],芯片工作电压为3.3 V,在待机的情况下,功耗非常低。FPGA逻辑电路设计包含有串并转换模块、同步信息检测模块、时钟产生逻辑模块、FIFO数据缓存模块和主控模块。串并转换模块主要用于接收外部PCM数据流进行串行数据到十六位并行数据的转换,为之后的数据解调、识别和判断做准备;同步信息检测模块用于将解调后的数据根据预置的同步字、子帧长度以及全帧长度与本次检测数据的结果进行同步信息比对,若信息比对一致则向FIFO缓存发出同步标志信号;FIFO数据缓存是在数据流进行同步信息检测的同时对缓存数据,等待同步信号,准备将缓存数据发送至USB2.0控制器;主控模块则主要用于控制该检查器的工作。

2.2 USB2.0控制器设计

本文采用CYPRESS公司的CY7C68013作为USB接口芯片,设计实现处理器和上位机的直接通过编写它的固件程序,设置它的工作模式、端口状态等[14]。CY7C68013为USB接口芯片,系统+5 V电源由主机的USB接口提供,CY7C68013所需的电源为+3.3 V。

USB2.0接口设计包括接口的硬件设计、控制器芯片CY7C68013的固件开发、上位机驱动编程加载软件开发3大部分内容[15-16],在这部分的设计中,主要参考了芯片CY7C68013的EZ-USB开发套件,其中CY7C68013的固件程序通过KEILC软件编写、编译形成用于加载的*.IIC文件,通过开发套件里的EZ-USB interface软件下载进与芯片CY7C68013配套使用的EEPROM芯片,通过CY7C68013的固件程序设置了用于USB通讯的四个端口(EP2、EP4、EP6、EP8),其中 EP2、EP6为输入端口,EP4、EP8为输出端口,EP2、EP4用于上位机和采集器之间传递命令和应答信息,EP6、EP8用于上位机和主控模块之间传递数据。

2.3 电平转换模块设计

因为FPGA的I/O口电平标准是3.3 V而USB采用的是5 V直流供电,针对不同的电平标准需要进行5 V到3.3 V的电平转换。本文选择了线性稳压器AS1117作为电平转换芯片,AS1117提供了完善的过压保护和过流保护功能,并且工作环境温度范围极宽(-50~150℃),同时,产品生产中应用了先进的修正技术,确保输出电压和参考源精度在±1%范围内。

AS1117是低压差的三端线性稳压器,外围应用电路只需要两个电容和负载即可正常工作(固定电压输出版本)。芯片内部包括了启动电路,偏置电路,电压基准电路等模块组成。此外当芯片内部结温过高(高于140℃)或负载电流过大时(大于1.4 A)会进入过流和过热保护模式,大大提升了整个系统的安全。

3 系统软件设计

系统软件设计分为PCM检查器SOPC系统软件设计和PCM检查器上位机软件设计。

3.1 SOPC系统软件设计

SOPC即片上可编程系统,SOPC系统的软件设计属于采集器的底层软件,它必须和SOPC的硬件结合才能构成完整的SOPC系统,所以它的设计与硬件设计密不可分。为了完成硬件系统的控制调度,在FPGA内生成了NiosⅡ嵌入式处理器,这是一种Altera公司推出的采用哈佛结构的具有32位指令集的第二代片上可编程软核处理器,其最大的优势是灵活性和可裁剪性。Nois中软件设计包括了关于系统初始化设计,PCM时钟采样设计和USB控制器的软件部分设计,通过结合外部硬件来实现PCM数据流的检查。

3.2 上位机软件设计

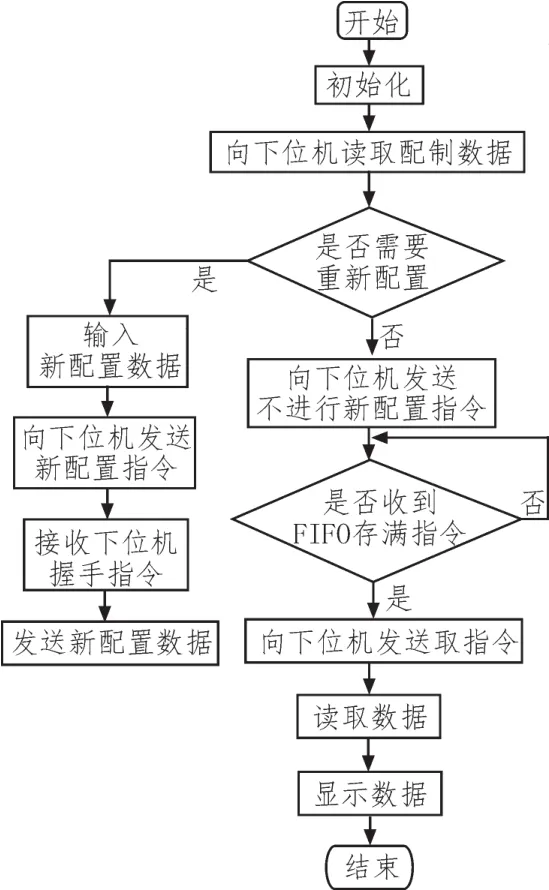

PCM检查器的上位机主要是用来与设备通过USB进行通讯、接收并存储PCM数据的。经过不断的设计优化,上位机软件流程如图2所示。

由图2可知,上位机软件通过连接、配置、同步、采集、存储来完成对PCM数据进行的检查。上位机软件每次运行时,都会判断是否需要重新配置所检查的帧格式,配置完成后则循环读取硬件FIFO的满标志位,当此位置位后上位机读出当前FIFO中存储的数据并做存储或实时显示。软件使用时,当PCM检查器通过USB电缆连接上PC机后,红色电源灯变亮,表明设备供电正常。上位机软件界面上有连接、配置、同步、记录、暂停等按钮。当检查器红灯亮起后,上电PCM输出设备使其开始工作,单击软件界面上连接按钮则软件初始化完成,设备与PC机连接正常。根据PCM数据流输出设备的PCM帧格式配置PCM检查器格式,当需要改变PCM帧格式或同步信息时,修改后单击配置按钮,否则配置为默认格式(同步头:FE6B AB40,帧格式:16×512,ID字256),配置成功后单击同步按钮,若同步成功,PCM检查器绿色的同步灯变亮,同时上位机软件中灰色的同步灯也会变成绿色,如果PCM检查器上位机软件界面中绿色的同步灯没有点亮,并且软件会提醒同步超时,表明所配置帧格式与实际PCM数据流不相符,需要确定前端PCM数据输出设备的帧格式后重新配置。同步完成后,单击记录就可以记录并回看所检查的PCM数据,软件界面同时显示了记录时间与存储文件的大小。PCM数据流检查器会监测PCM数据的同步字、命令字、数据块长度等信息。若一致则会输出错误信息。若数据不符合PCM帧结构,PCM检查器不会工作。

图2 PCM检查器软件流程图

4 结果与验证

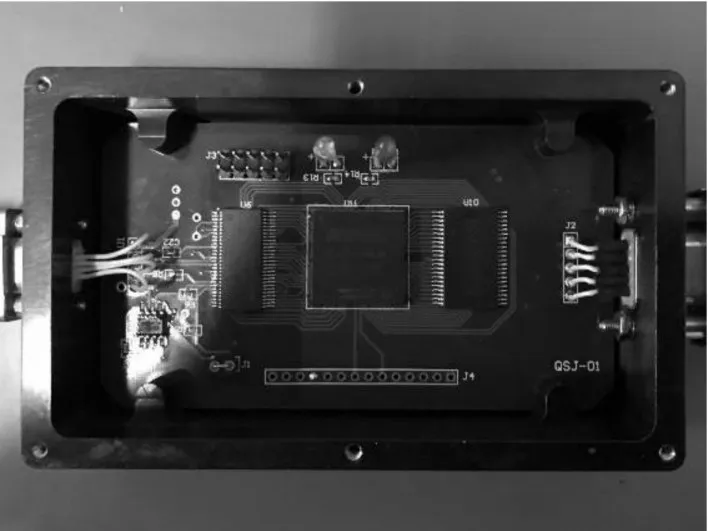

根据上两节介绍的硬件设计和软件设计,我们基于FPGA研制出这款PCM[17-19]数据流检查器。由于核心电路均采用工业级表贴器件,所以具有非常小的体积,长宽高依次为20 cm、8 cm和5 cm,并且适合在相对严苛和狭小的环境下工作。图3为便携式PCM数据流检查器的外形图。可以看出,USB2.0接口即作为与上位机软件的通信接口又是整个系统的供电电源,使用时差分的PCM数据和PCM位时钟在经过电平转换后首先进入FPGA芯片,通过时钟同步及数据流解码后PCM数据被存入FIFO缓存,当FIFO满标志置位后,PCM数据通过USB2.0控制接口发往PC机,进而实现与上位机的通讯与数据的实时检查与回看。

图3 PCM检查器外形结构图

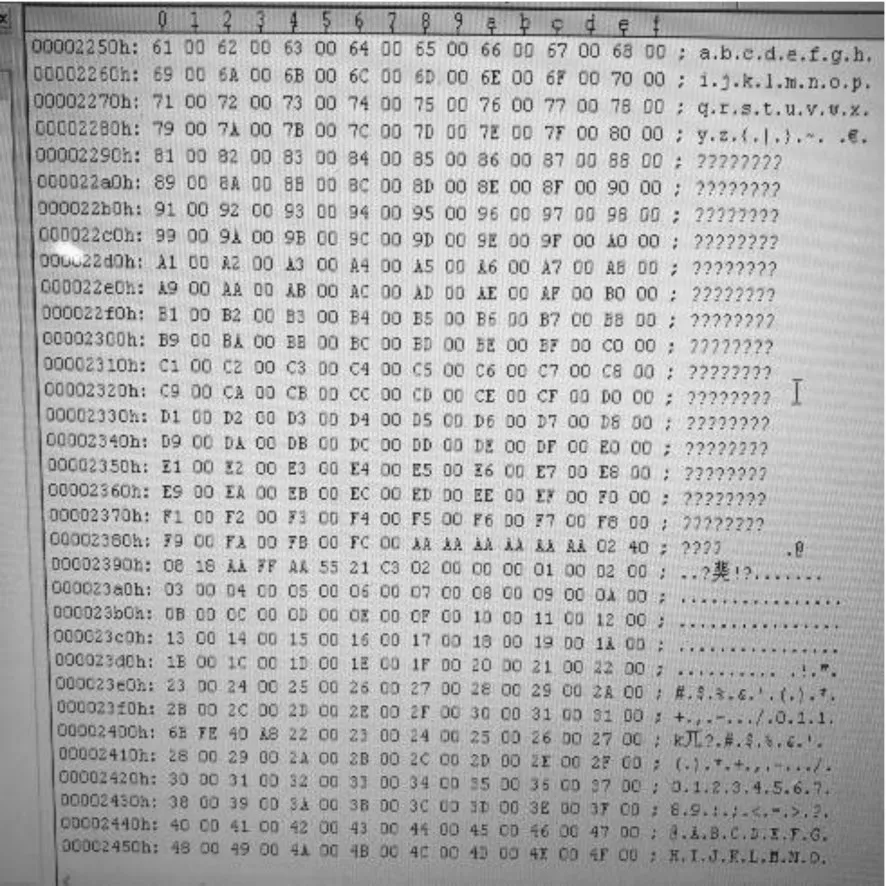

通过检查PCM数据流发生器所产生的帧结构可变的PCM码流以及长达12小时的拷机工作后,证明本次设计的产品完全满足设计要求。同时,为了保证高可靠性,依次进行了相应的常温试验、高低温试验、功能振动及冲击试验。产品均工作正常。更重要的是,为了验证PCM数据流检查器能否切实的在机载测试中使用,我们通过飞行试验检查了国产大型运输机飞控采集器输出的PCM码流。通过数十架次飞行前的地面检查,在对数据的解算处理后,并未发现错误与异常。图4为子帧识别号的连续性检查。图5为通过回看功能实现的PCM数据回看。数十次高可靠的数据流检测,证明我们设计的产品符合要求。

图4 子帧识别号连续性检查

图5 上位机PCM数据回看

5 结束语

本文完成一种具有高可靠、高速率、便携式的PCM数据流检查器的设计与实现。该设计针对传统PCM数据流检查器的不方便连接,体积过大等劣势进行了改进设计,同时,提供了方便与PC机连接的USB2.0接口,并采用USB直接供电。进行了大量的外场试飞试验,对飞控采集器前端的PCM输出数据的检查,并未发现错误与异常,充分证明了此种PCM数据流检查器的优越性和可靠性。

参考文献:

[1]杨廷梧,田宝泉.飞行试验新型遥测机载网络采集与记录系统架构[J].测控技术,2013,32(5):59-63.

[2]袁炳南,霍朝晖,白效贤.航空飞行试验遥测标准概况[J].测控技术,2010,29(11):10-14.

[3]党凡.航空飞行试验遥测技术的发展趋势展望与应对[J].通讯世界,2015(9):68-69.

[4]杨廷梧,王云山,腾斌.飞行试验遥测机载测试技术的发展与应用[J].测控技术,2013,32(14):5-8.

[5]支高飞,谷士鹏,吕鹏涛,等.机载测试系统的体系架构与应用前景[J].信息系统工程,2016(4):38.

[6]张跃飞,郝耀峰,孟尚,等.基于NiosⅡ软核的PCM遥测信号源设计[J].单片机与嵌入式系统应用,2016(7):54-56.

[7]苏淑靖,何青.基于FPGA的通用PCM测试系统设计[J].电子技术应用,2015,41(4):29-31.

[8]王闯,任勇峰,李辉景.遥测PCM数据收发接口模块设计[J].电子器件,2016,39(4):861-865.

[9]田宝泉,李国星.机载PCM数据流实时监控显示系统的设计[J].科学技术与工程,2013,13(19):5724-5727.

[10]夏利利,刘冰,周江,等.PCM遥测帧同步技术性能分析[J].电讯技术,2014,54(6):803-807.

[11]张小威,苏淑靖.可变帧结构的PCM遥测帧同步器设计[J].计算机测量与控制,2015,23(10):3476-3477.

[12]谢秀峰,苏淑靖.基于FPGA的通用PCM接收解码电路的设计[J].电子器件,2015(3):543-547.

[13]Altera,CycloneIIIDeviceHandbookVolume1,2012.

[14]陈七寨主,珍贵资料-cy7c68013中文手册.http://wenku.baidu.com/link?url=tfGL65HejDftGSBJkgT QSExeFtZcDZLXbpK3WmMOBxSdguEetlOvPjaHP 1BP7Zqn2qEb_9Ef8hDYis1nqt-ttMm98L55CnRY QYI3QHkoPKi.2013.

[15]赵林,孟令军,于磊,等.基于CY7C68013A的USB2.0高速接口设计[J].电子技术应用,2014,40(1):131-133.

[16]张莉,周雪纯,张乐.基于USB2.0接口的PCM数据采集器设计与实现[J].电子设计工程,2015(8):78-80.

[17]王丽君,李萌.基于FPGA的简易电子琴设计[J].电子科技,2017,30(5):62-64.

[18]杨延飞,雷倩倩,王春兰.基于边界扫描技术的FPGA延时故障检测[J].纺织高校基础科学学报,2017,30(3):396-401.

[19]欧阳文华.基于PCM和SDH技术的双传输多通道接入网络方案设计[J].电力信息与通信技术,2016(4):91-95.