基于动态加载技术的无人作战平台设备数据安全设计

2018-05-08董杰

董杰

摘要 本文以无人作战平台电子设备数据信息安全为应用背景,提出一种基于RS485串行接口和CPLD的FPGA程序远程动态加载设计方案。该方案中FPGA程序数据分为两个版本并通过不同方式进行加载:普通程序本地存储,上电直接加载用于保证设备一般功能的正常使用;核心程序外部存储,需要时通过远程动态加载,利用FPGA基于SRAM结构的易失性,实现重要程序数据断电自动清除,有效确保电子设备中重要数据的安全。

【关键词】无人作战平台 数据安全 RS485 串行接口 FPGA远程动态配置

1 引言

无人作战平台能够在危险复杂环境中执行情报监视与侦察、目标攻击、通信中继和电子干扰等任务,在军事领域应用越来越广泛。然而,由于其作战区域广闊,执行任务复杂多样,对全天时、高速通信链路的依赖较高,从而存在着失控和被敌截获风险。为了保证我方信息安全,除了增强平台本身的自主性和抗欺骗等能力之外,其搭载的任务载荷设备必须具备重要数据自动销毁功能。

传统的数据自毁方案一般是通过多种形式进行数据失控监测,在满足自毁触发条件时,通过软件、硬件、物理等多种自毁方式,对设备非易失性存储器中的程序、数据或存储器本身进行破坏,保证信息安全,但其自毁功能的实现是基于设备本身及其外围通信、电源等保障电路均可正常工作,在无人作战平台上,由于其任务环境的复杂性,很可能会出现电源中断、通信失联等突发性故障,若采用上述自毁方案,则存在数据自毁功能失效的风险。

利用器件本身基于SRAM结构的易失性实现数据断电自动清除,是设备实现自动销密的一种切实可行的实现方案,其突出的优点是可靠性高、电路结构简单,不需要额外的状态监测和电源保障电路,特别适用于对设备小型化要求较高的应用场合。

本文针对某无人作战平台任务载荷设备,利用FPGA基于SRAM结构的易失性(断电即丢失逻辑数据),设计了一种通过RS485串口进行FPGA程序远程动态加载、断电自动清除的方案。依据设备需要完成的功能,将软件程序分为基本和核心两个版本,任务载荷设备上的非易失性存储器中只存放基本版程序数据,保证设备在一般使用情况下,加电后基本功能可正常工作。核心版程序数据则保存在专用的数据加载设备中,当执行的作战任务需要使用核心功能时,在任务准备阶段,由数据加载设备通过RS485串行接口对任务设备进行核心版程序远程动态加载,当设备断电后,核心版程序数据自动清除,从而可保证了我方重要信息安全。

由于任务设备断电后核心程序数据即会自动清除,因此在每次执行任务前需对核心程序进行远程动态加载,这一过程需要占用任务准备时间,因此在设计过程中,必须考虑动态加载过程的操作便捷性、加载耗时和加载成功率。

2 硬件电路设计

系统设备在硬件组成上可分为数据加载设备和平台任务设备两部分,其硬件设计原理框图见图1。

数据加载设备是我方基地保障设备的组成部分,存储核心功能程序数据,并在需要时对平台任务设备进行程序注入。平台任务设备配置于无人作战平台上,其程序远程加载配置电路主要由FPGA、CPLD、基本功能程序存储器和电源储能/滤波电路组成。

任务设备与数据加载设备之间的通信采用RS-485串行通信接口,利用差分线形式传输。该接口具备较强的抗干扰性能和较高的传输速率,最大通信速率可达lOMbps,在点对点传输模式下,IMbps传输速率下可靠传输距离可达150m。由于设备间的通信流程单一,均由数据加载设备发起,任务设备被动响应,为简化接口连线,通信采用半双工模式,数据的收发共用一组差分线。

在本设计方案中,为实现CPLD对FPGA的加载配置控制,除常规的配置管脚外.还增加了CpuSt信号,该信号由FPGA的microblaze软核应用程序控制,当软核应用程序正常运行后,将该信号置高。增加该信号是由于当FPGA设计中配置了microblaze软核时,其配置加载过程除了常规的配置复位、初始化、加载配置数据和器件启动外,还存在一个软核应用程序启动过程,而此过程是在DONE信号被拉高之后进行,因此,CPLD在加载完配置数据后,除需检测DONE电平外,还要检测CpuSt信号,在CpuSt置高前,持续输出CCLK时钟,以保证用户的软核程序的正常启动运行。

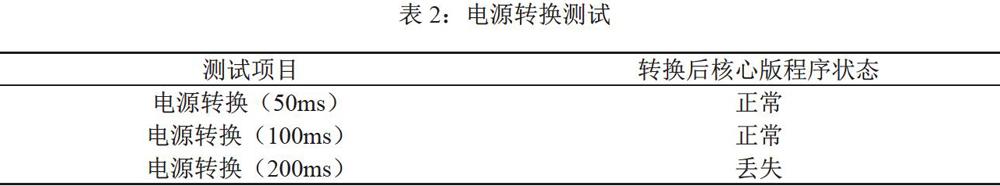

电源储能/滤波电路保证当核心版程序注入完成后,设备不会因突发电源干扰或平台电源切换导致核心版程序意外丢失。

3 远程加载逻辑设计

CPLD作为任务载荷设备的FPGA加载流程的核心控制器件,完成串行数据收发、加载指令解析、FPGA程序加载控制等功能。FPGA的加载配置流程分为FPGA上电加载配置流程和远程加载配置流程,工作流程示意图如图2。

任务设备上电后,CPLD即启动FPGA上电加载配置流程,从PROM中加载民用版程序,在执行完FPGA的基本配置加载过程后,继续保持CCLK时钟输出,保证MicroBlaze软核启动。上电加载时序逻辑如图3。

FPGA上电加载配置的工作步骤如下:

(1) CPLD上电复位后,控制PROG B输出宽度为500ns的负脉冲,清除FPGA配置存储器,同时控制PROM RST为低电平,对PROM进行复位;

(2)在PROG B负脉冲结束后,等待一段时间,将INIT B置高,同时结束对PROM的复位并打开PROM使能,打开CCLK时钟,此时,FPGA在CCLK时钟作用下,从PROM中加载配置数据;

(3)此后,CPLD实时检测INIT B、DONE和CpuSt信号的状态,当配置数据输出完毕,CRC校验正确后,DONE信号变高,此时可将PROM CE信号拉高关闭PROM使能,并继续保持CCLK时钟输出,当MicroBlaze软核启动完成后,CpuSt信号变高,结束CPLD上电加载流程;

(4)如果配置数据输出完毕,CRC校验错误,FPGA会将INIT B拉低,CPLD检测到INIT B下降沿后,CPLD进行全局复位,并重新开始上电加载流程。

当任务设备上电加载配置完成后,CPLD转入等待接收远程加载指令状态。当收到地面保障设备发送的远程加载启动命令后,进行FPGA程序远程加载配置,时序逻辑见图4。

FPGA程序远程加载配置的工作步骤如下:

(1)收到远程加载启动命令后,首先控制PROG B输出宽度为500ns的负脉冲,清除FPGA配置存储器,负脉冲结束后,等待一段时间,将INIT B置高,此时,通过串口发送加载启动确认回传,并打开加载超时计数器

(2)此后,每收到1帧串口数据,将数据按比特位倒序后输出,同时产生1个CCLK时钟,并将超时计数器清零;

(3) CPLD实时检测INIT B、DONE和CpuSt信号的状态,当配置数据输出完毕,CRC校验正确后,DONE信号变高,此时将CCLK时钟连续输出,当MicroBlaze软核启动完成后,CpuSt信号变高,结束CPLD上电加载流程;

(4)当CPLD检测到INIT B下降沿或者超时计数器溢出时,CPLD进行全局复位,并重新开始上电加载流程。

为防止加载过程意外中断而导致CPLD加载逻辑异常,在加载过程中需要进行异常超时判断处理,当连续一段时间未收到加载数据或加载状态未发生变化,则CPLD自动退出远程加载流程并复位,重新开始上电加载流程,确保远程加载因意外中断后,任务设备可迅速恢复其初始状态。

4 实际应用表现

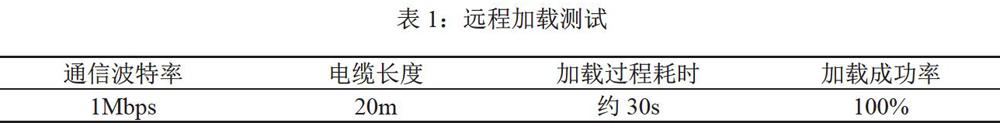

任务设备FPGA采用spartan-6系列低功耗器件XC6LX75,其配置bit流文件大小为19719712bit,在串行通信傳输过程中报文按8bit数据位组成1个字节传输,加上lbit起始位和lbit停止位,共lObit,因此,加载过程中实际传输的bit流大小为24649640bit,在IMbps传输速率下,完成一次远程加载的时间约为25s。

在试验室环境下,我们分别进行了远程加载测试和电源转换测试,测试结果分别见表l和表2。

5 结束语

本文给出了一种利用器件本身基于SRAM结构的易失性实现数据断电自动销毁的方案,在该方案中,一般程序数据本地存储,核心程序数据远程加载,可实现重要数据在设备断电后自动清除,能有效保障无人作战平台电子设备重要数据信息安全;同时,在一般应用场合或设备异常断电重启后,亦可保障设备基本功能的使用。本设计方案已在工程实践中得到验证,远程动态加载工作方式有效、可靠,可广泛应用于各种无人平台搭载的电子设备上。

参考文献

[1]李瑜,张文玉,无人作战平台指挥控制技术[J].指挥信息系统与技术,2011(06).

[2]卢正添,李涛,胡晓勤,赵奎,曾金全,彭凌西,一种数据自毁方法[J].计算机应用研究,2009 (01).

[3]李璟,刘宏伟,舒燕君,马闯,关键领域嵌入式容错机自毁功能[J],清华大学学报(自然科学版),2011 (SI).

[4]刘祥,宋克柱,张嗣峰,基于串行通信的远程FPGA在线配置[J].核电子学与探测技术,2010,30 (06):774-777.

[5]李燕春,基于CPLD的FPGA快速动态重构设计[J].电讯技术,2008,48 (07):87-89.

[6] Spartan-6 FPGA Configuration UserGuide[Z].X ilinx Inc, 2011.