LabVIEW辅助设计数字滤波器及FPGA实现

2018-05-07张文涛张鹏蛟

张文涛,张鹏蛟,赵 鹏

(长安大学,陕西 西安 0300511)

在辐照加速器低电平控制系统中,从加速腔中采集的信号受到外界的干扰信号的影响,为保证整个控制系统正常运行,并保证整个系统最低要求的精度,因此具有高精度、实时的数字滤波器的设计被提出来。数字滤波器的实质是对数字信号的运算处理,从而改变原始信号,完成滤波处理,得到要求的信号。通常模拟滤波器对滤波器元件精度要求比较严格,而且后面调试也比较耗时,且可靠性较低,相比起来,数字滤波器的可靠性和稳定性都很高,且容易调节,即只要改变滤波器的参数就可以很方便的改变滤波器的性能,直到达到要求[1]。

早期,为了解决滤波器的实时性和高计算速率问题,通常的办法是采用专用的高速数据处理芯片和汇编语言来完成程序编写,但是这样,一方面对硬件成本要求提高,另一方面设计周期会延长,并且芯片的存储量也对滤波器的设计有不小的影响。而大型可编程门阵列(FPGA)具有高速运算速度,大的存储量,可编程,用户易操作,从而大大地节省了设计成本和缩短设计周期。通过FPGA和LabView的联合使用,进一步提高设计速度和可靠性[2]。

1 FIR滤波器的原理

FIR滤波器,也就是有限冲击响应滤波器,字面上不难理解,也就是说,该滤波器一个单位响应脉冲是有限的。详细地来讲,FIR滤波器其突出特点是使其单位取样响应h(n)是一个N点长的有限长序列0~N-1.这样滤波器的输出y(n)可表示为输入序列x(n)与单位取样响应h(n)的线性卷积。其表达式如下。

从上面系统函数不难发现,FIR滤波器的极点只存在原点上,这使得FIR系统具有全局稳定性。另外分析其函数右边组成可知FIR滤波器可以看成加法器和乘法器组合而成,每个乘法器都有一个操作系数,也就是通常所说的抽头次数,这些抽头系数可以通过相关软件计算获得。这也是这种滤波器结构被人们称为“抽头延迟线结构”的原因。

1.1 FIR滤波器结构选择

大体来讲,根据不同场合要求有四种FIR的基本结构,根据不同的要求来供选择,即直接型、快速卷积型、频率取样型和级联型四种滤波结构。考虑到实现的复杂性,运算的存储量和FPGA实现的难易程度,因此,这里选择直接型FIR滤波器结构。FIR滤波器的输出y(n)可表示为输入序列x(n)单位取样响应h(n)的线性卷积,根据式(1)和(2)可以很容易得出FIR滤波器的直接型结构(假设滤波器的单位取样响应为M+1点长的有限序如图1所示[3]。

其系统函数为

图1 直接型FIR滤波结构

通过上面结构来看,就M+1阶的FIR滤波器,要有M+1个乘法运算单元和M个用来的延时单元,另外还要一个加法运算单元用来整合。由于通过FPGA完成上述结构过程中,乘法运算所耗器件资源要比加减法等运算所耗费资源多得多。因此在实际情况实现时,需要最大程度降低乘法运算量。由FIR滤波器相关结构特点,很容易知道,只有单位取样响应具有对称特性的FIR滤波器才具有线性相位特性,所以,一般都会使用具有线性相位特性结构的滤波器来实现FIR滤波器,着重点就是其对称特性,这样就省去了很大一部分器件资源。

根据FIR滤波器的幅度特性,可以将滤波器分成四种不同的结构,根据不同的结构,也分别对应了相应的直接型FIR滤波器基本结构。对于第一种结构,即M是偶数,且单位取样响应为偶对称的情况,对其系统输入与输出关系式如下所示。

同样的方法,也可以得出其它几种结构系统的输入与输出响应关系。对于第二种结构,即M是奇数,单位取样响应为偶对称的情况,系统输入与输出关系式如下所示

第三种结构,即M是偶数,单位取样响应为奇对称的情况,系统输入与输出关系式如下所示。

第四种结构,即M是奇数,单位取样响应为奇对称的情况,系统输入与输出关系式如下所示

根据式(3)、式(4)、式(5)、式(6),可以分别画出响应的实现结构,这里给出第二种对称机构的FIR滤波器结构如图2所示。

图2 线性相位FIR滤波器的直线型结构

通过观察图1和图2所示的两种滤波器结构不难分析可以得出,对于相同阶数的系统,使用线性相位的滤波器要比使用非线性相位的FIR滤波器所需要的乘法运算操作至少降低了一半,这样一来就可以很有效的降低对FPGA内部资源的使用。

1.2 FIR数字滤波器设计

FIR滤波器抽头系数h(i)设计方法有多种,有窗函数法(从时域角度出发)、频率取样法(从频域角度出发)、最优设计方法(等波纹切比雪夫逼近法),其中窗函数法设计最简便。Kaiser窗是一种可调窗,是利用I0(x)即等零阶贝塞尔函数构成的,Kaiser窗函数的表达式为。

式中,I0(x)是第一类变形贝塞尔函数;β是窗函数的形状参数,可以自由选择。改变β值可以调节主瓣宽度和旁瓣电平,β=0时相当于矩形窗,其典型值为4~9[4].

2 滤波器设计的前仿真

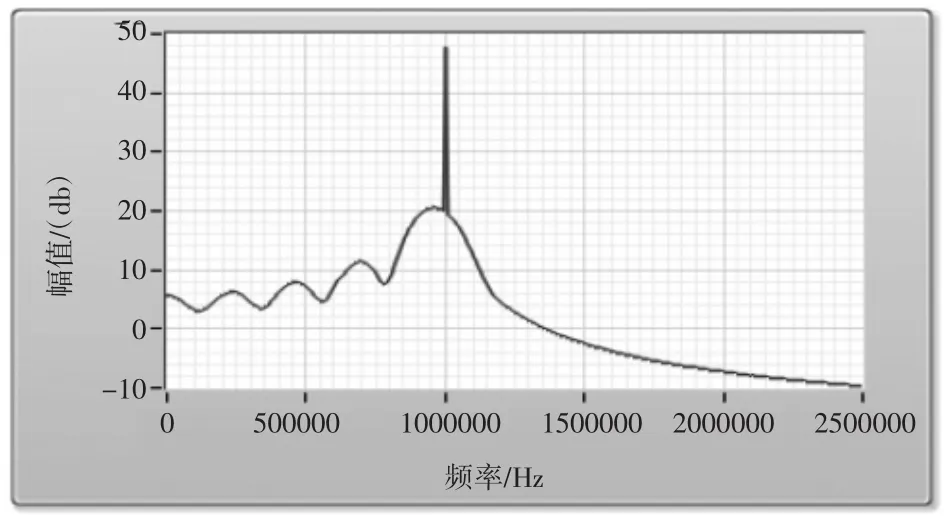

LabView有图形化表示的脉冲函数和正弦函数,强大的数据分析模块、图形语言和交互界面。程序编制模块由下而上,层层调用子程序,设计的交互界面调试方便。本设计待处理的信号是一个1 MHz正弦信号和2 MHz正弦信号的叠加信号,采样率为32 MHz,滤波器阶数为64阶。图3滤波器设计的频谱图。

图3 FIR滤波器的频谱图

从图3可以看到,显然1 MHz信号在通带内,而2 MHz信号在通带以外,被衰减掉了。下面图4、5和6是滤波器通过叠加信号之后的频谱图和时域波形,很明显2 MHz信号被有效地滤除掉了。

图4 LabVIEW中叠加信号通过滤波器的频谱图

图5 LabVIEW中叠加信号通过滤波器前的时域图

图6 LabVIEW中叠加信号通过滤波器后的时域图

3 通过FPGA的滤波器实现

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。本次设计采用的是Altera公司Cyclone IVE系列芯片,利用QuartusⅡ11.0编辑环境进行设计,QuartusⅡ11.0编辑软件中提供了大量现成可直接调用的IP核如加法器、乘法器等,大大的缩短了设计所需的时间。图7是具有线性相位的并行FIR滤波器结构图,以此为根据来编写FPGA程序[5]。

图7 具有线性相位的并行FIR滤波器结构

上述并行结构,即并行实现滤波器的累加运算,具体来讲就是将具有对称系数的输入数据进行相加,而后采用多个乘法器并行实现系数与数据的乘法运算,最后将所有乘积结果相加输出。可以看出,这种结构具有最高的运行速度,由于不需要累加运算,因此系统时钟频率可以与数据输出时钟频率一致。

4 FPGA设计实现后仿真测试

本次FIR滤波器FPGA设计仿真测试由Modesim仿真软件来完成,这是因为其有比较友好交互环境,仿真速度快,保护IP核不受影响,并且同时支持VHDL和Verilog HDL语言。仿真结果由图8所示。

图8 FIR滤波设计ModelSim仿真时序图

由图8可以看出,滤波器输入信号(Xin)的波形由于是频率1 MHz和2.1 MHz正弦波的合成信号,从时域上无法明显分辨出1 MHz信号,由于滤波器输出信号(Yout)是经过低通滤波后的信号,可以明显的看出2.1 MHz正弦波信号被滤除,保留了1 MHz正弦波信号,输出信号起始处波形是一小段直流分量,这是由于FIR滤波器运算时产生的固有延时造成。根据FIR滤波器原理,长度为N的滤波器,滤波延时为N/2个数据周期。

将上述滤波器输出信号上传给LabView,经过处理可得到图9.

图9 LabVIEW接收FPGA输出数据的时域图

由此可以通过LabView对比FPGA设计FIR滤波前后数据以达到对比的效果

5 结束语

本次设计首先通过LabView完成FIR滤波器设计的前期仿真,并得到FPGA设计所需要的抽头系数,然后使用VerilogHDL硬件描述语言完成FPGA的设计,接着将从FPGA输出的数据传输到LabView中,实现上位机和下位机的友好交互,已达到对滤波效果的实时检测。通过上述仿真结果证实上述方案的可行性。

参考文献:

[1]杜 勇.数字滤波器的MATLAB与FPGA实现[M].北京:电子工业出版社,2015:105-144

[2]姜碧琼,卢博友,雷永锋,等.基于LabVIEW7.0的数字滤波器设计[J].微计算机信息,2008,24(10):173-174.

[3]李泽明,李锦明.FIR数字滤波器的MATLAB辅助设计及FPGA实现[D].太原:中北大学,2013.

[4]蔡 兴,唐 求.基于LabVIEW的多采样率数字滤波器1/3倍频程计算方法[D].长沙:湖南大学,2015.

[5]夏雨文.Verilog数字系统设计教程[M].3版.北京:北京航空航天大学出版社,2013:97-110.