一种低抖动快锁定的时钟数据恢复电路设计

2018-04-19胡腾飞

胡腾飞,方 毅,黄 鲁

(1. 中国科学技术大学 电子科学与技术系,安徽 合肥 230027;2. 中国科学技术大学 信息科学技术实验中心,安徽 合肥 230027)

0 引言

时钟数据恢复电路(CDR)广泛应用于各类串行通信中,如微波通信[1]、光纤通信[2]、以太网等。时钟数据恢复电路主要通过调整时钟与数据的相对相位关系,从带有噪声的信号中恢复出“干净”的时钟与信号,通常要求电路具有恢复数据抖动小、锁定时间短、抖动尖峰低等性能。

基于锁相环与延迟锁相环混合技术[3]的时钟数据恢复电路相对于传统基于二阶锁相环结构的电路,可以有效解决抖动抑制与锁定时间之间的矛盾,实现零抖动尖峰。它利用延迟锁相环(DLL)调节输入数据相位实现快速锁定;通过锁相环(PLL)实现小的传输带宽,降低恢复时钟与数据的抖动;并且闭环传输函数无零点,实现零抖动尖峰。

1 时钟数据恢复电路的整体结构

基于传统二阶锁相环技术的时钟数据恢复电路的结构如图1所示,主要由鉴相器(PD)、电荷泵(CP)、低通滤波器(LPF)、压控振荡器(VCO)四个模块组成。鉴相器识别出数据与时钟的相位差,电荷泵将其转化为充放电时间差,环路滤波器生成VCO控制电压,调节压控振荡器的输出频率,以使时钟的边沿对准数据的中心。

图1 基于二阶锁相环结构的数据时钟恢复电路

通过分析其小信号模型,可以得出其抖动传输函数:

(1)

其中KD是鉴相器与电荷泵的增益,Kvco是压控振荡器的增益。

根据式(1)容易知道它有一个零点和两个极点,零点与低频主极点位置接近,两者影响相互抵消,因此抖动传输带宽实际上由高频极点确定。由于抑制数据抖动需要小的抖动传输带宽,而快速锁定需要大的抖动传输带宽,因此两者相互冲突。此外,零点先于低频极点出现,于是该频段处的增益会大于1,出现抖动尖峰[4],此频段处数据抖动被放大以致影响系统性能。

基于锁相环与延迟锁相环(D/PLL)混合技术的数据时钟恢复电路结构如图2所示,它由两个环路构成:压控延时线(VCDL)、鉴相器(PD)、电荷泵(CP)、环路滤波器(LPF)组成延迟锁相环(DLL)环路;压控振荡器(VCO)、鉴相器(PD)、电荷泵(CP)、环路滤波器(LPF)组成锁相环(PLL)环路。当数据领先于时钟时,系统提高压控振荡器的频率并增加压控延迟链的延迟,前者加快时钟的相位,后者延迟数据的相位,最终消除两者的相位差。

图2 基于延迟锁相环与锁相环结构的时钟数据恢复电路

通过分析其小信号模型,可以得出其抖动传输函数:

(2)

其中KD是鉴相器与电荷泵的增益,Kvcdl是压控延迟线增益,Kvco是压控振荡器增益。

根据式(2),它有两个极点而没有零点,当ωp1<<ωp2时,可以推导出两个极点分别为:

(3)

其中ωp1为低频主极点,ωp2为高频次极点。

由于没有零点的影响,式(2)的闭环传输函数的抖动传输带宽由主极点ωp1决定,锁定速度则与次极点ωp2有关。明显看出,可以单独设置2个极点,分别改变传输带宽和锁定时间。倘若式(1)和式(2)具有相同的极点分布,则式(2)电路有更低的输出抖动,且无抖动尖峰。根据式(3),通过增大DLL中压控延迟线的增益Kvcdl,降低PLL中压控振荡器的增益Kvco,可以减小ωp1并增大ωp2,于是数据的输出抖动得以减小,而锁定速度得以加快。

总之,相对于传统的二阶锁相环结构,基于锁相环与延迟锁相环复合技术的时钟数据恢复电路,通过分别设计两个极点的方法,很好地平衡了锁定速度与输出抖动的折中关系,增加了设计的自由度。这样就有效解决了传统结构中抖动抑制与锁定时间矛盾的问题。

2 主要模块设计

2.1 鉴相器

鉴相器的主要功能是将时钟跳边沿调整到最佳采样点处,由于伪随机数据(PRBS)会出现连续的0或1,不适用鉴频鉴相器,因此本文采用了改进的Hogge鉴相器[3],如图3所示。它同时利用时钟信号高、低电平的宽度,而不仅仅是利用单个电平宽度(高电平或低电平),来减小时钟占空比对输出的影响;此外,对于改进的Hogge鉴相器,数据即使长时间没有跳变,恢复好的时钟也不会滑离最佳采样点,比普通的Hogge鉴相器具有更好的噪声性能。

图3 Hogge鉴相器

当电路锁定时,Hogge鉴相器的各信号时序波形如图4所示,其中Vout是环路滤波器上的控制电压。从图中可以看到,采样过程中环路滤波器净积累电荷为零,所以Vout保持稳定。

图4 Hogge鉴相器各信号时序波形图

2.2 压控振荡器

压控振荡器用于产生时钟,它的相位噪声性能直接影响恢复出来的时钟性能。本文采用了3级延迟单元构成压控振荡器。

图5 压控振荡器的延迟单元

压控延时单元采用对称负载结构[5],如图5所示,它包括两组对称负载M1~M4、差分输入对管M5和M6、偏置电流源M7。通过调节偏置电流和控制电压VBP,可以改变对称负载的等效阻抗,进而改变延时单元的延时。

基于对称负载结构的延迟单元可以更好地抑制共模信号噪声,此外,连接每个延迟单元的尾节点,可以减小电源噪声的影响。VCO的相位噪声仿真曲线如图6所示,1 MHz处的相位噪声约为-103 dBc/Hz。

图6 VCO相位噪声曲线

2.3 压控延迟线

压控延时线用于对输入数据产生延时,通过改变控制电压可以快速调整输入数据的边沿,实现数据的快速锁定。本文采用了30级延迟单元构成压控延时线,以使延时调节范围覆盖压控振荡器的调谐范围,保证整个系统成功锁定。

压控延时单元采用的是带对称负载的伪差分结构,如图7所示,它包括一对差分管MP1与MP2、一对对称负载管MN1-MN2与MN5-MN6、交叉耦合管MN3-MN4。其中对称负载有助于提高单元延迟随控制电压变化的线性度,交叉耦合管可以加快输出电平的翻转速度,使数据边沿更加陡峭。通过调节偏置电压VBN,可以改变对称负载阻值的大小,最终改变延迟单元的延迟时间。

图7 压控延迟线的延迟单元

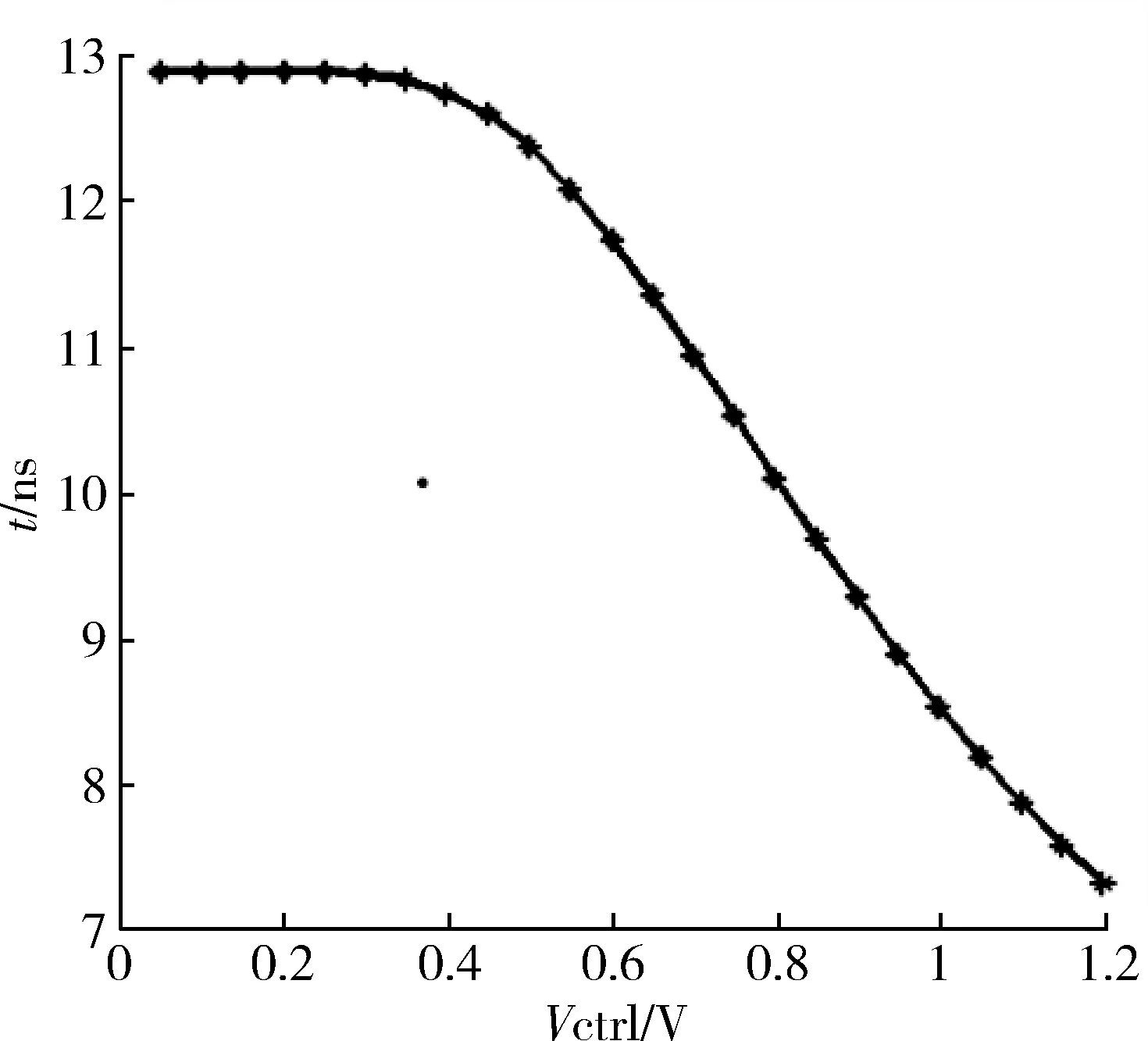

压控延时线的延时随控制电压变化的仿真图如图8所示,在0.4~1.2 V之间有良好的线性度。

图8 延时与控制电压的关系

2.4 电荷泵

电荷泵由鉴相器的输出控制着上、下电流源的通断,从而改变环路滤波器上的控制电压,以调整压控延时线的延时与压控振荡器的振荡频率,实现数据的锁定。本文采用了低噪声、高匹配度的电荷泵[6]。

原理图如图9所示,反馈晶体管Mfp和Mfn的栅极与输出Vout相连,当Vout电压上升,Mfn的导通电阻减小,复制到Msn的电流降低,而Mfp的导通电阻增大,复制到Msp的电流升高,抵消沟道调制效应,增加了充放电电流的匹配性。电容C用来抑制由于时钟馈通导致的栅极电压抖动,加快开关速度。Mdn和Mdp用来消除a点和b点在开关Msp和Mdp时闭合状态的累积电荷。

图9 电荷泵

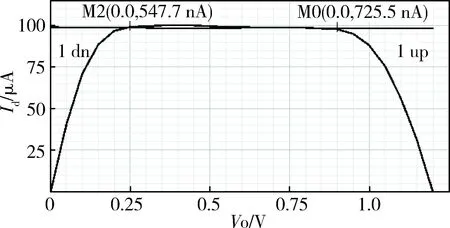

电荷泵充放电电流的匹配曲线如图10所示,可以看到电流在0.25~0.9 V之间匹配性良好。

图10 上下电流源匹配曲线

3 仿真结果和比较

时钟数据恢复电路在TSMC 0.13 μm CMOS工艺下设计,面积大约为0.15 mm2。

本文采用Cadence下的Spectre模块对电路进行后仿真,图11给出了时钟数据恢复系统锁定时的伪随机数据与时钟信号的波形图,可以看到时钟的上升沿正好对准信号的中心,电路恢复出数据与时钟。图12给出了输入信号与输出信号的眼图对比,输入数据与输出数据的峰峰值抖动分别约为374 ps与39 ps,可以看到电路有效地抑制了数据中的抖动。

图11 时钟与信号锁定图

图12 输入与输出数据抖动眼图

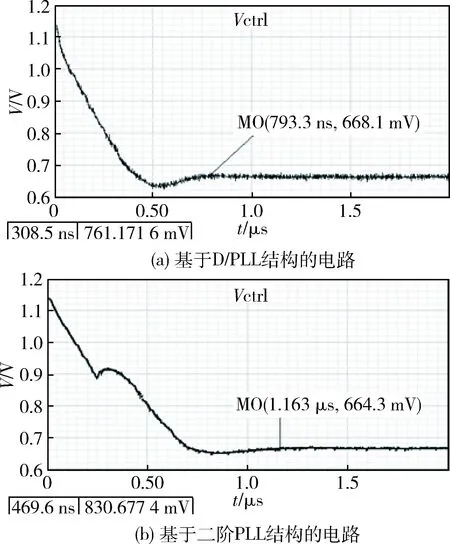

图13给出了在时钟的输出抖动一致的前提下时,基于D/PLL结构与基于二阶PLL结构的电路锁定时间仿真图,锁定时间分别为0.793 μs与1.163 μs,可以计算得到本文结构提高了约32%。

图13 时钟数据恢复电路的锁定时间

本文设计的时钟数据恢复电路与其他电路性能设计对比如表1所示,本设计具有较小的相对抖动,功率与面积适中。

表1 本设计和其他设计比较

4 结论

本文基于TSMC 0.13 μm的工艺,设计了一种锁相环与延迟锁相环混合技术的时钟数据恢复电路。仿真结果表明它具有适中的功耗与面积和良好的抖动性能,相对基于传统二阶PLL结构的电路提高了锁定速度。

[1] 张丽,徐妍,马丽珍,等.一种基于FPGA的微波时钟恢复的设计与实现[J].微型机与应用,2016,35(5):81-83.

[2] RAZAVI B. Challenges in the design high-speed clock and data recovery circuits[J]. IEEE Communications Magazine, 2002, 40(8): 94-101.

[3] LEE T H, BULZACCHELLI J F, et al. A 155-MHz clock recovery delay-and phase-locked loop [J]. IEEE Journal of Solid-State Circuits, 1992, 27(12): 1736-1746.

[4] YANG R J, CHAO K H, HWU S C, et al. A 155.52 Mbps-3.125 Gbps continuous-rate clock and data recovery circuit [J]. IEEE Journal of Solid-State Circuits, 2006, 41(6): 1380-1390.

[5] MANEATIS J G, KIM J, MCCLATCHIE I. Self-biased high-bandwidth low-jitter 1-to-4096 multiplier clock generator PLL[J]. IEEE Journal of Solid-State Circuits, 2003, 38(11): 1795-1803.

[6] YOSHIMURA T, IWADE S, MAKINO H. Analysis of pull-in range limit by charge pump mismatch in a linear phase-locked loop [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2013, 60(4): 896-907.

[7] LEE S K, KIM Y S, HA H,et al. A 650 Mb/s-to-8 Gb/s reference-less CDR circuit with automatic acquisition of data rate [C].2009 IEEE International Solid-State Circuits Conference-Digest of Technical Papers. IEEE, 2009: 184-185,185 a.

[8] INTI R, YIN W, ELSHAZLY A. A 0.5-to-2.5 Gb/s reference-less half-rate digital CDR with unlimited frequency acquisition range and improved input duty-cycle error tolerance [J]. IEEE Journal of Solid-State Circuits, 2011, 46(12): 3150-3162.

[9] PARK M J, KIM H, SON S. A 5-Gbps 1.7 pJ/bit dither-less CDR with optimal phase interval detection [C]. Proceedings of the IEEE 2012 Custom Integrated Circuits Conference. IEEE, 2012: 1-4.