SoC FPGA在声波测井仪器中的软硬件协同设计

2018-04-11,,,

,,,

(1.清华大学 自动化系,北京 100084;2.中海油服油田技术研究院)

引 言

声波测井仪器作为声波测井的主要工具,在设计时由于井下高温、井径限制等不利因素的存在,需要具有较低的功耗、较小的体积以及大批量数据的快速处理能力[1-2]。早期设计时由于受到电子器件的限制,仪器内部数据采集和处理电路普遍采用了DSP+FPGA的多核架构[3],该架构虽然具有很大的灵活性和较强的数据处理能力,但缺点是高功耗、电路复杂、集成度低,并且降低了仪器整体可靠性。随着测井温度的不断提高,对电路的功耗和集成度要求越来越高,采用多核架构设计的电路难以满足要求。

随着电子技术的发展,具有更高集成度和更低功耗的SoC(System on Chip)芯片被越来越多地应用到嵌入式系统设计中,为提高系统可靠性和降低功耗发挥了重要的作用。例如Microsemi推出的SmartFusion2系列SoC FPGA就是一种集微处理器子系统MSS(Microcontroller Subsystem)和FPGA资源(FPGA Fabric)于一体的低功耗、高集成度芯片[4],将其用于声波测井数据采集和处理电路设计可以极大地降低功耗和提高集成度。

采用SoC FPGA设计系统,各功能模块既可以通过MSS包含的ARM微处理器用软件实现,也可以通过FPGA资源用硬件实现。硬件实现的特点是运算速度快、时序控制精确,但是设计复杂、占用资源多且灵活性差;软件实现的特点是灵活性好、不占用FPGA资源,但是数据处理效率低。因此设计中如何兼顾系统的功能和性能要求(例如低功耗、资源占有小、处理时间短等)而采用不同的软硬件实现方法成为难点,对该设计方法的研究也被称为软硬件协同设计[5]。

本文首先将系统按照所完成的任务划分为若干子模块,然后通过讨论分析各模块任务特点、资源占用和处理时间均衡来确定模块的最佳实现方式,最后对系统的数据存储配置和低功耗设计进行了优化。

1 声波测井仪器电路结构及SoC FPGA内模块划分

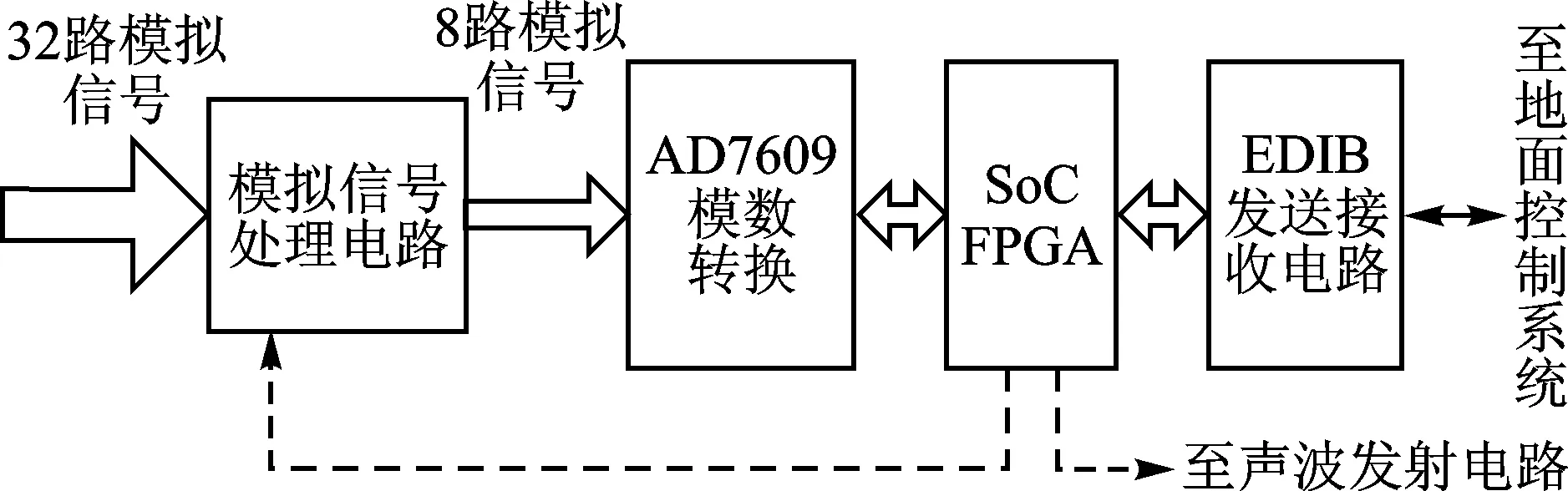

图1是设计的耐高温声波测井电路结构简化图,SoC FPGA作为仪器的核心芯片与AD7609模数转换、EDIB发送接收电路共同构成数据采集处理系统,主要功能包括与地面控制系统的通信、采集流程控制、数据采集控制、数字信号处理和对模拟信号处理电路及声波发射电路的控制。数据采集和处理系统严格按照地面控制系统的指令执行测井任务。在收到采集指令后,首先对其它电路的参数进行设置,然后按设定的流程进行声波信号的发射、采集和数字化处理,最后将打包压缩的数据发送至地面控制系统。

图1 仪器内部电路结构简化图

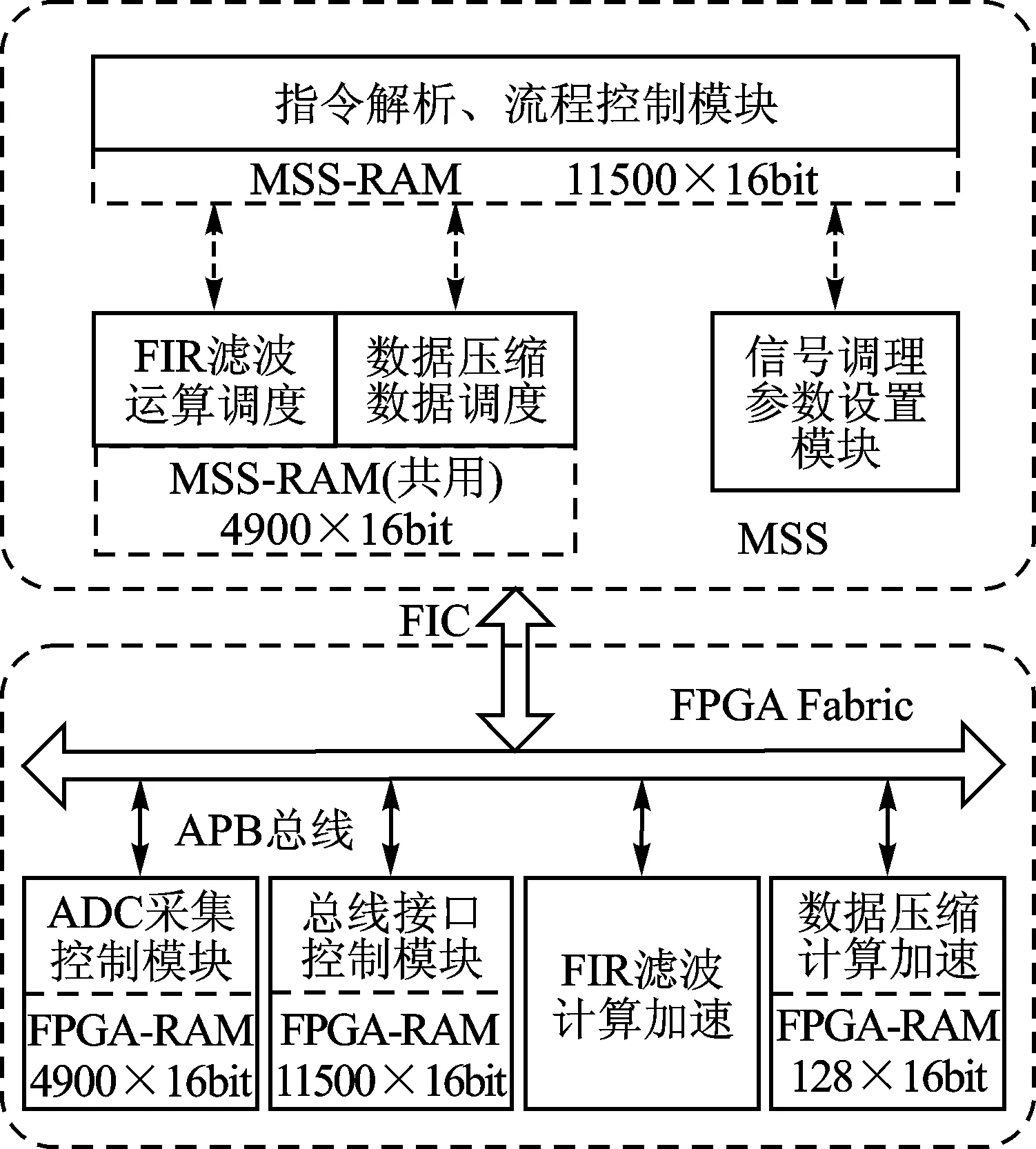

按照系统所完成的任务,可将SoC FPGA任务划分为6个模块,如图2所示,各模块关键工作步骤如下:

① 指令解析和流程控制:地面控制系统下发的指令分为参数设置和采集控制两大类,数据采集处理系统接收到指令后首先对指令类型进行判断,然后按照指令内容完成参数设置和采集控制。

② 信号调理参数设置:按照指令对声波发射电路和模拟信号处理电路参数进行设置,包括声波发射器激发选择、声波信号模拟处理电路各通道增益设置和滤波带宽选择等。

③ ADC采集控制:完成ADC采集控制和结果读取。对于ADC的采集控制既要满足采样率、采样延迟和采样点数要求,还要在规定时间内完成8通道同步采集结果的读取和最大值提取。由于受ADC硬件接口特性和最短采集时间的限制,所以对数据传输总线的控制时序要求较高。

④ FIR (Finite Impulse Response)数字滤波:模拟信号经过ADC转换后变成数字信号,FIR滤波可以进一步滤除数字信号中包含的噪声。

⑤ 数据压缩:由于声波测井仪器和地面控制系统之间的数据传输总线带宽有限,因此为了提高仪器的测井效率,需要减少数据的传送时间,为此对上传数据进行压缩以减少传输数据量。

⑥ EDIB(Elis Downhole Instrument Bus)总线数据传输[6]:由于从地面控制系统下发的指令和数据采集处理系统上传的数据都经过该总线传输,因此总线接口控制必须具有较高的可靠性和较强的数据处理能力。总线接口控制模块在底层控制上要求能实现对数据的曼彻斯特编解码并以规定速率高速串行收发,在顶层控制上实现数据接收后的及时处理和数据发送时的自动操作。

图2 数据采集处理系统软件功能模块划分

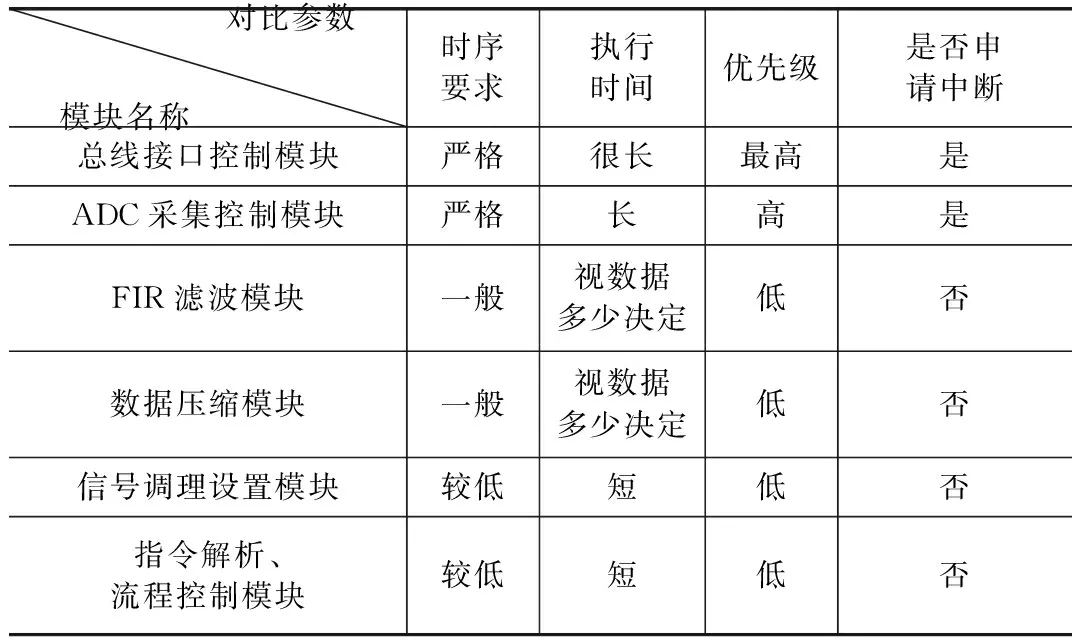

在各模块完成的任务中,既有精确的时序控制,比如ADC采集控制模块和总线接口控制模块,也有复杂的条件判断,比如流程控制模块和信号调理设置模块。表1按照时序要求、执行时间、优先级和是否申请中断4个方面将各模块的任务特点进行了对比。

表1 模块任务特点对比

通过对比分析可知:①对于ADC采集控制模块和总线接口控制模块,如果以软件方式实现,不仅难以满足8通道同步ADC采集和总线编码高速收发的严格时序要求,而且由于两个模块执行时间长,会导致对微处理器的长时间独占,无法满足系统整体的处理速度要求。因此这两个子模块应该由FPGA实现,这样既可以实现严格的时序控制,又能满足数据处理的性能要求。② 流程控制模块和信号调理设置模块属于复杂条件判断任务模块,在执行时对时序要求不是很严格,用软件方式实现最合适。③ FIR滤波模块和数据压缩模块都属于数字信号处理模块,既可以通过软件方式实现,也可以通过硬件方式实现,单从表1对比无法确定最佳实现方式,还需要通过对资源消耗和处理时间的分析后才能确定。

另外,在声波数据采集处理系统系统中,由于要实现8通道声波信号的实时采集和大量数字信号的处理,需要较多的SRAM作为数据缓存。在SoC FPGA内部,由于FPGA资源和MSS两部分都集成了丰富的SRAM,因此如何在设计中有效平衡各自SRAM的使用,也成为提高系统集成度、优化数据带宽和资源利用率的一个重要环节。

2 根据资源占用和处理时间均衡的设计

2.1 FIR滤波模块和数据压缩模块的设计

使用SoC FPGA内FPGA硬件或ARM微处理器软件设计数字信号处理模块时,主要区别在处理时间、资源消耗和设计难度三个方面。硬件在处理过程中通过调用乘积累加单元和对数据的并行计算可以成倍地将时间缩短,但缺点是较多的资源占用和较高的功耗,而且采用硬件设计时需要进行严格的仿真和测试,一旦设计完成,不容易修改。软件完成数字信号处理时,算法设计灵活简单,但缺点是运算速度慢、执行效率低。

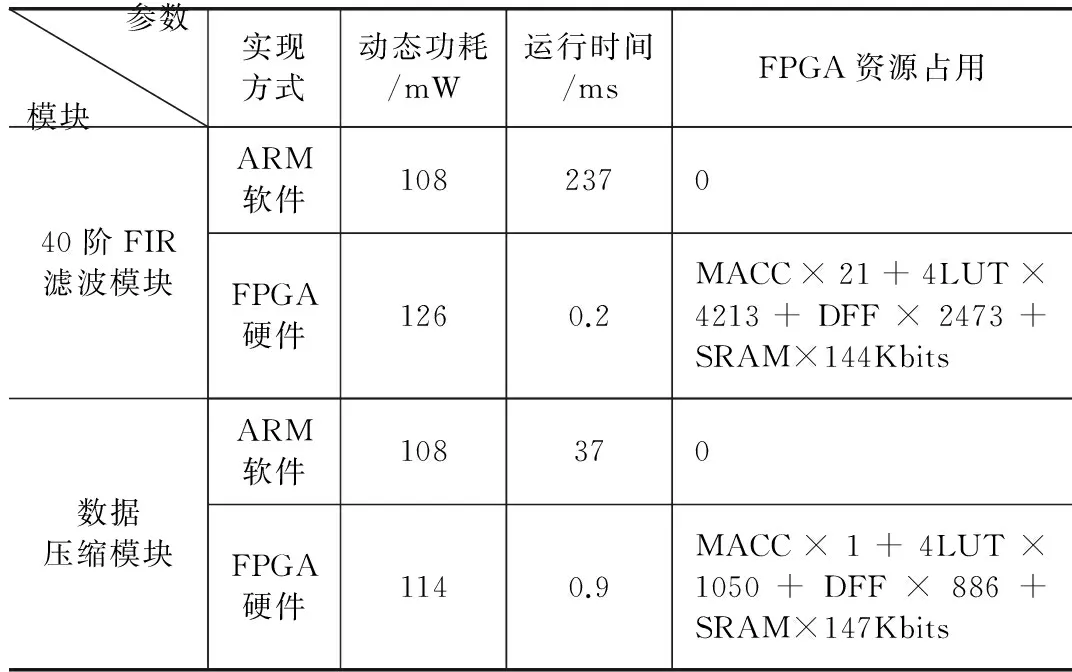

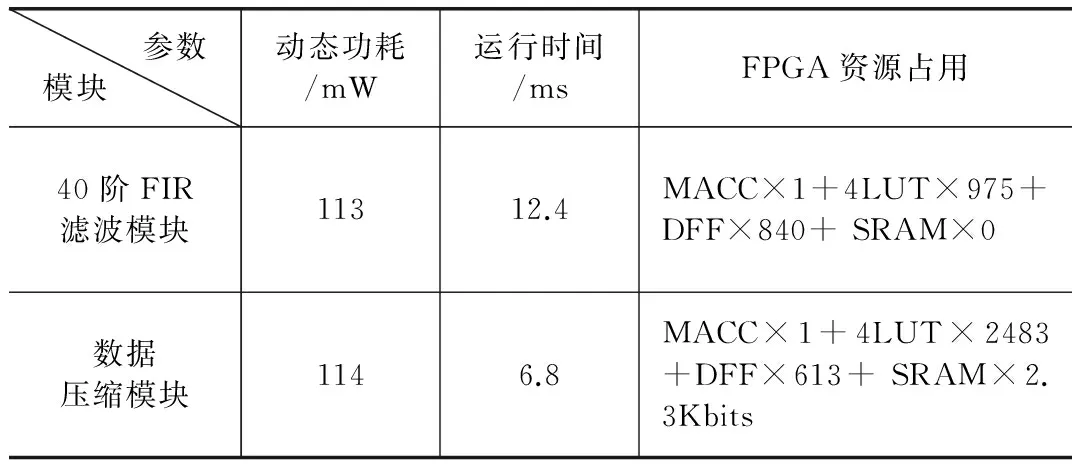

为了确定FIR滤波模块和数据压缩模块采用不同方式实现下的运行时间、资源占用和功耗,分别设计了硬件模块和软件程序进行对比测试,见表2。其中硬件模块基于Verilog设计,软件使用C语言编程。测试芯片为SmartFusion2系列的M2S010TQ144,其中微处理器工作时钟为100 MHz,FPGA驱动时钟为24 MHz,测试数据为4 800个半字(16位有符号数),功耗通过Microsemi提供的功耗计算器(Power Calculater)计算得到。FPGA资源占用包括乘积累加单元MACC(Multiply-accumulate)、4输入LUT(4-input LUT)、DFF(Flip-Flop)和SRAM(Static Random Access Memory)。

表2 软硬件不同实现方式下的参数对比

从表2参数可知,两个模块采用硬件实现的运行时间都在1 ms以内,远低于软件实现的时间,但是对FPGA资源占用较多,尤其是FIR滤波模块,MACC占用达到95.5%,4LUT+DFF占用达到28%,并且两个模块都需要大量SRAM。从参考文献 [7]和软件的估算结果可知,更多的资源占用意味着更高的功耗和更多的发热。

当模块使用软件实现时,虽然不占用FPGA资源,但是运行时间太长。在一个采集周期内,留给FIR滤波和数据压缩的时间通常为20~30 ms,从表2所列运行时间可知,软件实现方式无法满足要求。

由以上分析可知,当模块采用单一软件或硬件方式实现时,都存在明显不足。设计时如果能将软硬件实现方法结合起来,可能会得到更优化的结果,实现资源占用和处理时间的均衡。通过对两个模块数据处理过程分析可知,FIR滤波模块主要进行移位和乘加运算,且每次运算过程完全相同。数据压缩模块虽然计算量小,但是对数据的调度复杂。为此采用软硬件结合的思路重新设计了FIR滤波模块和数据压缩模块。系统结构如图3所示,由微处理器负责FIR滤波模块的运算调度和数据压缩模块的数据调度,FPGA则实现对乘加运算和数据移位操作的加速,二者通过FIC(Fabric Interface Controllers)和APB(Advanced Peripheral Bus)总线实现高速数据交换。

图3 采用软硬件结合后的系统结构

表3是采用软硬件结合思想设计的FIR滤波模块和数据压缩模块对于运行时间、动态功耗和FPGA资源占用的对比。

表3 软硬件结合方式下的参数对比

采用软硬件结合思想设计模块后,缺点是运行时间比FPGA实现方式有所增加,但是仍然满足系统的时间要求,优点是对FPGA 资源占用明显减少。 FIR滤波模块在使用一个乘法器的情况下,通过将计算过程串行化,对资源占用降低至FPGA实现的27%。数据压缩模块通过ARM完成数据调度和存储后,内部SRAM资源的占用降低至原来的1.6%。尽管资源占用减少带来的功耗降低并不明显,但为设计中芯片的选型降低了指标要求,进而降低了成本。

2.2 SRAM资源分配设计

通常DSP和ARM由于内部集成SRAM容量有限,当处理大量数据时,需要外扩存储芯片以满足存储要求。而SoC FPGA器件在微处理器子系统和FPGA内都含有较多SRAM,只要合理安排使用,便可在不使用片外存储的情况下满足较大容量数据缓存的应用。对于FPGA内部的SRAM,优点是读写速度快、容量大,适合作为FPGA硬件模块的高速数据缓存,缺点是读写接口控制需要占用额外资源且SRAM自身存在功耗。对于微处理器系统内包含的SRAM,既可用于微处理器执行代码和数据的存储,也可作为用户数据的缓存。

结合各模块对数据缓存的需求及采集系统内数据交换的特点,对SRAM分配方式进行了合理设计,如图3所示,具体方式如下:

① ADC采集控制模块和总线接口控制模块使用FPGA内部的SRAM,以保证数据的高带宽和稳定性。这两个模块对数据缓存都有特殊要求,ADC采集控制模块为了完成8通道同步采样,必须保证在单个采集周期内将从ADC读出的串行数据按并行格式写入缓存中。总线接口控制模块为了保证数据在高速串行传输过程中不间断,必须保证读取缓存数据的及时准确。

② FIR滤波模块和数据压缩模块共用微处理器子系统内部SRAM作为数据缓存以降低资源占用,同时在FPGA内部分配少量SRAM以满足加速运算对带宽的要求。

③ 信号调理设置和流程控制模块使用微处理器子系统内部SRAM作为数据缓存。

3 低功耗优化设计

3.1 进入低功耗模式

数据采集处理系统工作时有固定的采样周期,在采样周期内各个模块并不是处于连续工作状态,而是按照流程控制模块的调配进行工作,因此可以设定不工作的模块进入低功耗模式以降低系统功耗。

例如ADC采集控制模块,在不同配置参数下最长工作周期为62.4 ms,最短1.66 ms。该模块工作时,除负责流程控制的微处理器进行轮询操作外,其它模块都处于停止状态。当ADC采集控制模块结束工作后,微处理器才会读取采集数据并进行后续处理。长时间的轮询操作对系统来说意味着功率的消耗。实际上,SmartFusion2芯片中的微处理器可以通过进入休眠状态来降低功耗[8],并且以中断方式快速唤醒。基于微处理器这一特点,可以在设计中为ADC采集控制模块添加至微处理器的中断信号,当ADC采集控制模块工作时,微处理器进入休眠状态,当工作结束后再以中断方式唤醒微处理器。

与微处理器工作状态相反的是ADC转换器AD7609,在当前数据采集周期结束后至下个周期开始前,该芯片都不需要工作。由于AD7609芯片具有低功耗模式,可以通过控制STBY*和RANGE引脚设置是否进入待机或关断模式。因此设计中可以通过微处理器控制芯片的工作状态。其余模块也可采用上述类似方法降低系统功耗。

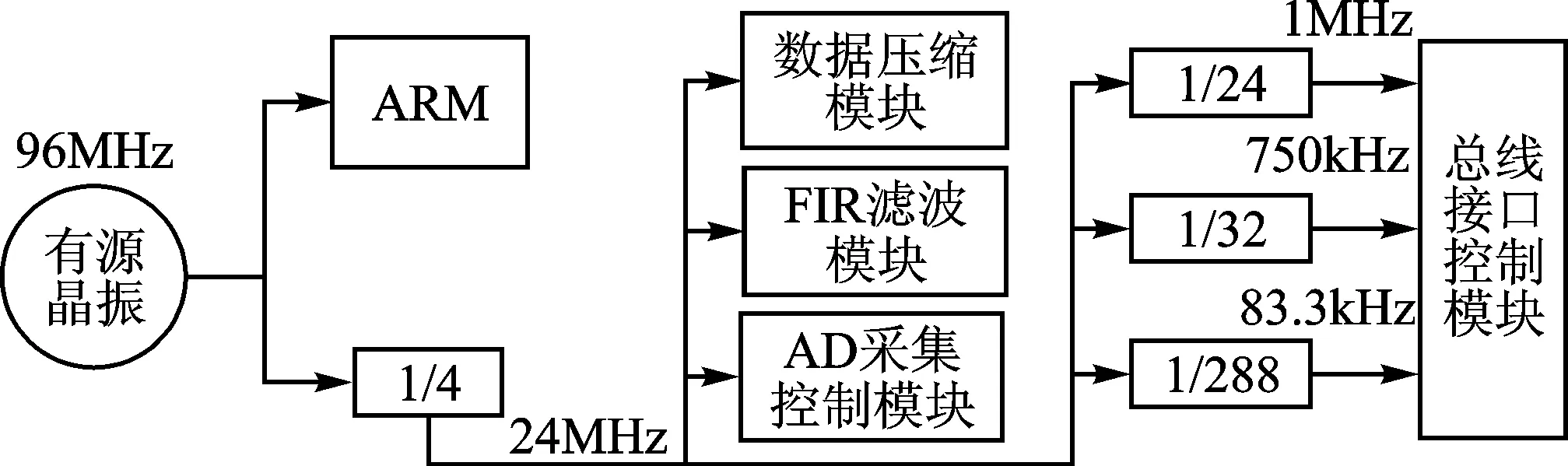

3.2 合理分配系统时钟

SoC FPGA芯片工作时,内部各模块需要不同频率的时钟驱动。例如,ADC采集控制模块需要24 MHz时钟,总线接口控制模块需要1 MHz、750 kHz和83.3 kHz三路时钟。虽然SoC FPGA内部已经嵌入的硬件锁相环模块可以精确输出4路频率和相位不同的时钟,但是该模块的使用会增大系统功耗。

通过对各模块时钟需求的分析,发现有两个特点:一是各路时钟没有相位要求,二是低频率时钟和高频率时钟成倍数关系。为此对系统中的时钟进行合理分配,如图4所示。通过使用96 MHz有源晶振作为系统时钟源,既可以保证时钟的稳定性,又可以满足微处理器子系统对于高频率时钟的需求。对于低频率时钟,则通过分频模块对高频时钟分频得到。

图4 SoC FPGA系统时钟分配

结 语

[1] 佚名.极端井况下的测压取样技术[J].国外测井技术,2015(5):58-68.

[2] 臧德福,王树松,郭红旗.高温测井仪器研制[J].石油管材与仪器,2010,24(2):1-2.[3]李苏,李辉,李春楠,等.数字声波测井的数据采集与处理电路设计[J].电子测试,2011(12):5-7.

[4] Microsemi Corporation.Microsemi Introduces Next-generation SmartFusion2 SoC FPGA with Breakthrough Capabilities in Security,Reliability and Low Power,2012.

[5] 张丹,董雷刚,祝裕璞,等.基于SOPC嵌入式系统中软硬件协同设计方法研究[J].大庆师范学院学报,2012,32(6):40-44.

[6] 黄理琴.声波测井仪器测试系统的实现[D].成都:电子科技大学,2008:11-13.

[7] Belhadj H,Aggrawal V,Pradhan A,et al.Power-Aware FPGA Design[J].2009.

[8] Microsemi公司.利用SmartFusion2 FPGA器件实现低功耗设计[J].今日电子,2013(4):33-34.

张利伟(硕士研究生),主要研究领域为检测与电子技术;叶朝辉(副教授),主要研究领域为检测与电子技术。