基于0.18μm CMOS工艺的0.1-2 GHz宽带功率放大器芯片

2018-04-11成都嘉纳海威科技有限责任公司邬海峰

成都嘉纳海威科技有限责任公司 邬海峰

天津城建大学 朱 琳

青海民族大学 林 倩

1.引言

近几十年来,覆盖VHF至UHF频段的射频收发系统在卫星广播、航天器通信、射频识别、全球定位等的军用与民用通信电子装备中发挥了巨大价值[1]-[3]。由于电子装备正在向着小型化、高集成度、轻量化、多功能和低成本等方向发展,因此系统迫切需要射频收发机前端中功率放大器(PA)芯片具备宽带放大的功能。所以,实现上述频段的宽带、低成本的CMOS PA可以有效地支持电子装备的研发与应用。

高功率、宽带射频CMOS PA设计具有较大的挑战性。首先,CMOS工艺的低击穿电压和高膝点电压等[1]-[2]限制了PA的功率输出能力;其次,宽带匹配电路的设计难度较大。一般来说,实现宽带PA的常规方法包括分布式和平衡式放大结构[3],但是,分布式放大器的效率偏低并占用较大的芯片面积,芯片成本高[5];平衡放大器则需要采用90°移相的耦合器,其带宽较窄且不宜采用片上电路实现[3]。其他方法如采用变压器匹配和RLC等匹配网络不可避免采用片上感性器件,所以也占用较大的芯片面积[3]-[5],成本难以降低。

“晶体管堆叠法”就是一种有望解决上述设计难题的技术,它采用顺次串联连接晶体管的结构,来实现高电压摆幅和高输出负载阻抗,从而克服低击穿电压限制并具有极佳的宽带输出特性,它的高输出阻抗可以直接被设计为50 Ω的标准阻抗,从而避免采用电感或者变压器等来匹配,大大降低了芯片面积[5]。

本文介绍了一种双级、四晶体管堆叠宽带CMOS PA。结合负反馈技术和阻性匹配技术,该CMOS PA具有极宽的功率输出特性且占用较小的芯片面积。经过商用0.18 μm的CMOS工艺流片后,该双级PA的测试结果实现了覆盖0.1–2 GHz频段的180%的相对带宽、18.1±0.6 dB的增益和平坦度、20 dBm的饱和输出功率、优于-10.5 dB和-12.6 dB的输入与输出匹配和12%的功率附加效率(PAE)。该PA仅占用0.52 mm2面积。据作者所知,这是实现满足上述指标CMOS PA中面积最小的芯片。

2.电路设计

本文提出的双级、四堆叠结构PA如图1所示,其中四个场效应晶体管(M1–M4或M5–M8)按照从漏极到源极的方式自直流馈电点顺次连接到地。其中,双级放大结构用于提升PA的功率增益,四堆叠结构用于增大输出功率和输出阻抗,从而增强电路的宽带功率输出能力。理想情况下四堆叠结构总电压摆幅是单个晶体管的四倍而电流不变。因此,根据欧姆定律可知四堆叠结构的功率输出能力和输出负载阻抗是单个晶体管的四倍。输入串联电阻(R1)和负反馈电阻(R12)用于改善电路的输入与级间匹配特性;负反馈电阻(R13)用于改善电路的级间与输出匹配特性;电阻分压网络(R2–R6,R7–R11)为堆叠结构的四个晶体管提供恰当的栅极偏置电压。尽管堆叠结构放大器是潜在不稳定的,但是电阻分压网络、阻性匹配和反馈网络却可以改善电路的稳定性。栅极外加电容(C3–C5, C7–C9)用于调节堆叠晶体管间的最佳负载匹配阻抗;输入电容(C2&C6)用于实现电路的阻抗匹配和隔直功能。图1中虚线框内的器件均为片上元件,隔直电容(C1&C10)和馈电电感(L1&L2)采用片外器件。

图1 双级四堆叠结构PA电路原理图

堆叠结构中以第二级放大器为例,四个堆叠晶体管的尺寸和工作状态在理想情况下是一样的;每个堆叠晶体管在饱和区的静态漏极电流Ids=1/2μnCoxW/ L(Vgs-Vth)2。其中,μn为迁移率、Cox为单位表面面积的栅电容、W为晶体管栅宽、L为栅长、Vgs为栅电、Vth为阈值电压,因此可得Ids约为80 mA。单级晶体管的最佳负载阻抗为,Zopt=(Vds-Vknee)/Ids。其中,Vds为漏源电压,Vknee为膝点电压、Ids为漏源电流。当Vds-Vknee为1 V时,可得Zopt为12.5 Ω。因此,四堆叠结构的总输出最佳负载阻抗为50 Ω,它不需要额外的输出匹配网络就可以实现堆叠结构的50 Ω最佳负载阻抗匹配,由此大大节省了面积并降低了输出网络的设计难度。当工作频率远远小于晶体管特征频率ft时,该双级放大器在50 Ω输入与输出阻抗下的小信号电压增益为:Av=50RLgm1gm2/((1+RL/R12)(1+ 50/R12)),RL=R13/(1+gm2/(sC6(R8+1/sC7)||R7+ 1)50||R11))。其中,gm1和gm2是一二级放大器的跨导。通过增大串联电阻(R1)的值可以改善输入阻抗的宽带匹配响应并提升电路稳定性,牺牲电路的增益和噪声特性。反馈电阻(R12&R13)降低电路的低频增益,改善高频特性,改善电路的宽频响应。通过优化R12的大小可以获得S21增益平坦度、输入与输出匹配指标的良好折中的设计,R1和R13可采用类似的方法确定。当选取R12=200 Ω时,在0.1–2 GHz内可以获得优于-12 dB的输入匹配,和24±1 dB的增益平坦度。

3.实验结果

采用0.18μm CMOS工艺流片后,本文提出的双级四堆叠PA芯片如图2所示。利用一个隔直耦合器、两个偏置器和四个直流探针等器件,该PA测试了在片小信号S参数、连续波和三阶交调。

图2 双级四堆叠PA芯片照片(0.52 mm2)

双级PA的交流小信号S参数测试结果如图3所示。该PA在0.1–2 GHz内达到了18.1±0.6 dB的增益及平坦度、优于-10.5 dB的输入匹配(S11)和优于-10.5 dB的输出匹配(S22)。PA的小信号增益在实测中恶化约6 dB,这是由于芯片通过DC-probe接地时产生的寄生电感等参数所导致的。但S21的增益平坦度却得到了一定程度的改善,这是由于电路仿真设计中高频增益比低频增益更高,在电路实测中高频部分的增益恶化现象比低频段更严重,因此补偿了高频的高增益设计余量,由此改善了电路的增益平坦度。Kf系数在测试中大于1,表明该PA电路是稳定的。

图3 交流小信号S参数测试结果

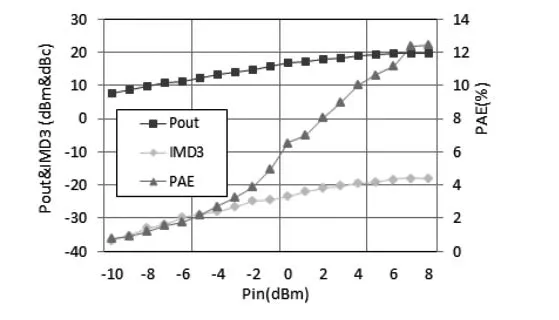

双级PA在900 MHz时的连续波测试如图4所示,该PA实现了20 dBm的饱和输出功率、12%的PAE和0 dBm输入时优于-25 dBc的三阶交调(IMD3)。

图4 900 MHz连续波输出功率和PAE

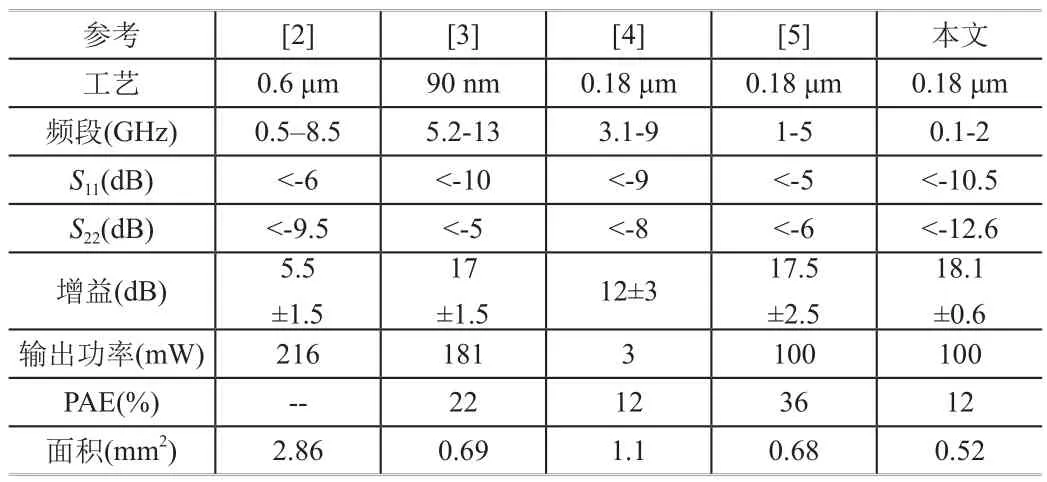

表1展示了本文提出的CMOS PA与文献中的CMOS PA特性指标的比较。本文提出的CMOS PA具有极佳的增益平坦度指标、良好的宽带输入与输出匹配,并且占用很小的芯片面积。实测结果显示该PA适合VHF和UHF频段的低成本应用。

表1 本文PA与文献中CMOS PA比较

4.结论

本文介绍了一种0.1–2 GHz频段的宽带CMOS PA的设计、加工和实测结果。通过采用双级四晶体管堆叠结构结合电阻匹配和反馈网络,该PA实现了良好的宽带匹配特性、增益和增益平坦度等指标,并且该PA芯片占用很小的芯片面积,大大节省了设计成本。该设计表明了采用堆叠结构结合电阻反馈网络的方法是一种有望在很小的芯片面积内实现超宽带CMOS PA的设计方法。

[1]H.F.Wu,Q.F.Cheng,X.G.Li,andH.P.Fu,“Analysisanddesignofanultra-bro adbandstackedpoweramplifierinCMOStechnology,”IEEETransactionsonCircuits andSystemsII:ExpressBriefs,63(1),49-53,Jan.2016.

[2]H.T.AhnandD.J.Allstot,“A0.5–8.5GHzfullydifferentialCMOSdistr ibutedamplifier,”IEEEJ.Solid-StateCircuits,vol.37,pp.985–993,Aug.2002.

[3]H.Wang,C.Sideris,andA.Hajimiri,“ACMOSbroadbandpoweram plifierwithatransformer-basedhigh-orderoutputmatchingnetwork,”IEE EJ.SolidStateCircuits,vol.45,no.12,pp.2709–2722,Dec.2010.

[4]H.C.Hsu,Z.W.Wang,andG.K.Ma,“AlowpowerCMOSfull-bandU WBpoweramplifierusingwidebandRLCmatchingmethod,”inElectronDevic esandSolid-StateCircuitsConf.Dig.Tech.Papers,Dec.2005,pp.233-236.

[5]P.C.Huang,Z.M.Tsai,K.Y.Lin,andH.Wang,“Ahigh-efficiency,b roadbandCMOSpoweramplifierforcognitiveradioapplications,”IEEETra ns.Microw.TheoryTech.,vol.58,pp.3556–3565,Dec.2010.