自动测试设备测试接口板可靠性的评审方法与要求

2018-04-03张明杰黄姣英

高 成,张明杰,黄姣英

(北京航空航天大学 可靠性与系统工程学院,北京 100191)

随着制造工艺的进步,集成电路的集成度和设计复杂度迅猛提升,测试也越来越复杂,如今集成电路基本依靠自动测试设备(automatic test equipment,ATE)完成,评测ATE测试的可靠性成为目前集成电路评测中的瓶颈问题,也是鉴定检验中的测试难题。

接口板的可靠性直接影响着测试程序运行的正确性,因此,测试接口板(device interface board,DIB)可靠性评审是测试程序评审的重要环节[1]。按照军用电子元器件科研项目鉴定检验程序的要求,单片集成电路提交鉴定检验时必须提供测试夹具接口板。但由于缺少对研制单位提供的测试夹具接口板进行评价和确认的相关标准、规范、方法等依据,使得检验机构无法对研制单位提交的申请材料进行有效确认,并且也无法对测试结果进行确定性评价。因此,当前大规模集成电路鉴定检验中,电性能测试环节存在测试不全面、结果不准确、考核不一致的问题。

目前,国内外在印制电路板(PCB)设计和信号完整性研究方面取得了较多成果。国外关于单板信号完整性问题的研究已较为成熟,如TOLESCU等[2]对差分线进行研究,提取了其分布参数并建立耦合线模型;随后RUBIN[3]提取和测量了差分线的特性阻抗等参数;PANTIC-TANNER等[4]研究了电源线对信号线的串扰影响,提出了减小走线并行长度、增加走线距离等减小串扰的方法;HSU等[5]通过预布局和布局后的质量检验,有效减小了串扰影响;SEUNGYOUNG等[6]分析了差分线的衰减和时延,特别是阻抗匹配等基本的信号完整性问题。国内研究中于学萍等[7]研究了割裂地对信号线间串扰的影响,提出了保护带屏蔽干扰线的方法;宋占海等[8]研究了垂直交叉线之间串扰的影响;张建新[9]采用隔离带法来减小串扰,并针对某一有信号完整性问题的电路板,选取频率为50 MHz的关键时钟网络进行分析,用终端匹配法减小反射。

笔者通过分析印制电路板设计和制作过程对测试接口板可靠性的影响,提取影响接口板可靠性的因素,确定测试接口板可靠性的评审要素,提出自动测试设备测试接口板可靠性的评审要求。

1 测试接口板可靠性的影响因素分析

1.1 设计因素

(1)测试接口板层数。大多数的混合信号测试接口板由6~10层的PCB形成。不同被测设备(device under test,DUT)的测试接口板中布线层有着很大的区别。内层一般来说是用来接地和连接电源,还有一些非关键性的信号;而外层则用来处理关键信号,由于外层较为关键且易于观察,故必要时可以在测试过程中增加一些测试点。

(2)测试接口板材料。测试接口板可以由很多种材料制成。互联材料一般是铜,绝缘层材料一般是FR4玻璃丝。其中,玻璃丝价格低,且拥有优良的电学性能,其频率可以达到几百兆赫,当频率达到1GHz时,就需要Telfon或Cynate ester等材料。Telfon拥有良好的微波特性,包括较低的信号损失和较低的绝缘成份,但硬度不够强;Cynate ester则拥有很高的频率和强度。因此,将这两种材料混合,得到的新材料的性能介于两者之间。

(3)测试接口板接地和电源布线设计。接地点是在一个电子系统中各种接地的电子连接和物理安置。接地是进行高频、小信号器件测试中必须且较难掌握的测试接口板设计技术。接地不好会导致电压下降、电感跳变、电容串扰、通频带改变等问题,从而影响测量精度或产生噪声。获得合适接地点的一个方法是密切注意测试接口板和测试中通过路径、连线和平面的电流,尤其是在接地连接处由阻抗下降引发的直流测量误差。

在一个混合信号测试中,电源供给使用一个典型的4线卡尔文结构进行连接。每一个卡尔文连接包括加电高电位(HF)、加电低电位(LF)或接地电流回路、测量高电位(HS)、测量低电位(LS)4根独立线。测量低电位线与DGS相当。因此所有供给可使用一个单一的DGS线作为测量低电位的参考标准。

接地面在测试接口板中的所有接地点中提供了低电感连接。类似地,为减小所有电源结点间的系列电感,电源层可按一定路线输送电源。电源和接地层可以分成若干部分,每一部分携带不同的信号,如+12V、+5V、-5V,而不需要为每一个电源供给提供独立的PCB层。

在一个混合信号的测试接口板中,一般至少有两个独立的接地层。其中一个层为传输线路径传递数字信号地,这个层遵从于由数字信号引起的快速变化的电流。因此,该层显示出由于电流和其自身电感相互作用引起相对较大的电压尖刺,在测试接口板体系中,这个地层常常被称为DGND(数字地);另一个层为模拟信号使用的AGND(模拟地)[10]。

(4)测试接口板主要元器件选用。测试接口板元器件的选用要使元器件的性能、指标、封装形式满足测试接口板的设计要求,更重要的是要考虑元器件的温度漂移、时间漂移、参数分布差异可能对测试接口板造成的影响,尽可能选用小体积封装、温度漂移小的元器件。同时也要注意元器件的温度范围,必须在被测集成电路三温测试条件下能够稳定工作。

测试接口板上的DUT引脚和电路,在测试工作时有可能使用端测试插头或电流接触器组件进行暂时连结。值得注意的是插头和电流接触器组件适配座的金属连结表现出额外的电阻、自感系数和接地电容,尤其在高频下,有时插头和接触器甚至会引起测量失败。因此适配座是否可用对于集成电路测试也十分重要,除了不能对器件造成损伤等基本要求外,适配座应满足待测器件的耐电压、电流、频率等工作条件。在测不同封装器件时要更换适配座,适配座的使用次数也应满足要求。

1.2 信号传输完整性影响因素

对于测试速率为100 Mbps以上的专用集成电路测试系统,必须充分考虑信号传输完整性的问题,即从测试板到负载板的信号传输应能够满足测试的要求,而从负载板到被测器件中间的信号传输就是测试用户需要考虑的问题,主要是测试接口板的设计问题[11]。如何实现这个转接过程的信号无失真传输,对整个测试过程至关重要。

信号检测的理想情况是测试系统产生的输出信号无失真地加到被测器件的输入引脚,同时被测器件的输出信号无失真地返回到测试系统的信号输入端子,即整个信号的传输“完整且未受损”,即信号传输的完整性[12]。具有良好完整性的数字信号应是干净、快速跳变信号,具有稳定、有效的电平,准确的时间位置,且没有瞬态变化。

如何更快、更好地提供检测,已经不是简单提高测试系统速率的问题。当测试信号频率增加时,电路板上的走线已不再是简单的导体。在较低的信号频率下,信号传输走线主要表现为阻抗特性;当频率增加时,走线的分布参数电感、电容开始起作用,这些都会对测试信号传输的完整性产生不利影响。

为保证测试接口板传输信号的完整性,测试接口板设计中应注意以下问题:数字信号衰减与同步、建立或保持等时间相关问题,模拟信号的衰减问题,电源和地的变化问题,故障、信号过冲、串扰及多余的噪声问题等,因此需要在连线的屏蔽、驱动保护、传输线的分布参数、终端阻抗匹配、接地和电源设计等方面采取控制措施。

2 测试接口板可靠性评审要素

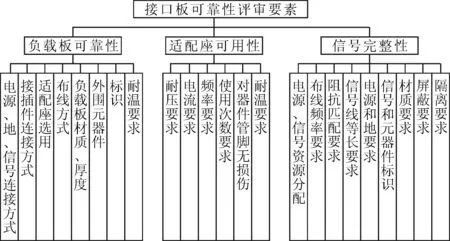

根据对测试接口板可靠性影响因素的分析,可以确定测试接口板可靠性评审要素,如图1所示。评审要素分为2级,第一级要素包括负载板可靠性、适配座可用性和信号完整性3个要素,第一级要素又可细分为若干个底层评审要素,即为ATE测试接口板可靠性评审的最终评审要素。依据涉及内容的不同,每个评审要素确定的评审内容有所不同,最终提炼得到ATE测试接口板可靠性评审方法与要求。评审要求覆盖工艺、材料、电源等设计影响因素,同时还覆盖阻抗匹配、电磁兼容等信号完整性的影响因素。①负载板可靠性。负载板可靠性主要评审接口板的信号、电源等布线布局分布情况,层数、板厚是否符合要求,负载板的设计对测试的影响等。②适配座可用性。适配座的可用性主要关注适配座耐压值、频率、电流、使用次数、耐温等要求。③信号完整性。信号完整性主要关注阻抗匹配、传输线特性、电磁兼容性等多种影响信号传输的因素,以及评审接口板对信号传输过程的影响因素。

图1 接口板可靠性评审要素

3 测试接口板可靠性评审方法与要求

3.1 测试负载板的可靠性评审

(1)电源连接方式。电源个数、电源电压值、电流功耗是否满足器件规范的最大指标要求;每组电源和地之间是否放置滤波电容;对主要工作电压需要有单独的电源层。

(2)地(GND)连接方式。负载板中需要有单独的地层,如果器件存在数字地和模拟地,模拟地和数字地要分开,并通过磁珠或0欧姆电阻进行连接。

(3)信号管脚连接方式。被测信号管脚要与测试系统进行连接,所选测试系统的通道数要满足被测器件的信号管脚数要求。

(4)接插件连接方式。负载板与测试系统进行连接,需要相应的接插件,接插件的性能要满足信号传输的频率和负载要求,同时也要满足一定次数的插拔要求。

(5)适配座选用。适配座要选用测试插座,满足器件最大工作电压、最大功耗、最高工作频率等指标要求,同时也要满足一定次数的测试要求。

(6)布线方式。测试负载板上尽量避免飞线连接的情况,对于大规模集成电路中的同组或同类型信号,在负载板上的布线最好等长或接近等长,以免由于信号线的长度相差太大,导致信号传输延迟不同,影响器件的正常工作,布线拐角尽可能大于90°,也尽量少用90°拐角,走线尽量在焊接面,少用过孔跳线。

(7)负载板材质。当信号的传输频率低于1 GHz时,可以选用FR4制作负载板;当信号的传输频率高于1 GHz时,要选用更高级别的材质,常用的有罗杰斯或其他能满足信号的传输频率的材质。

(8)外围元器件。测试负载板上如果有电阻、电容、继电器、信号转接头、指示灯、按钮开关等元器件,需要满足被测器件的指标要求。

(9)标识。测试负载上要有明显的标识,如器件的型号、器件的放置方向、电源和地等标识,以方便程序调试和生产测试。标识信息已经成为现代元器件管理系统中的重要组成部分[13]。

(10)耐温要求。根据被测器件的最大工作温度范围来确定,满足低温-55 ℃、高温150 ℃的要求。

(11)负载板厚度。负载板厚度要根据适配座要求来定,对于插针式适配座,厚度不能超过针脚长度;对于顶针式适配座,其厚度不能超过定位螺丝长度。

3.2 适配座的可用性评审

(1)耐压要求。适配座应满足器件最大工作电压要求。

(2)电流要求。集成电路的规模越大,工作频率越高,其工作电流也会相应提高。现在部分大规模集成电路的工作电流超过1 A,对适配座的要求也就比较高,普通的适配座难以满足要求,大部分需要进行特殊定制,为了在调试器件时确保器件的正常运行,延长适配座的使用寿命,在适配座上需附有散热装置。

(3)频率要求。为了让器件在高频下能够正常工作,适配座的信号传输要能够满足器件最高工作频率的要求。

(4)使用次数要求。在进行大规模集成电路调试或测试时,需要经常更换电路,适配座需要具有一定次数的使用要求。

(5)对器件管脚无损伤。适配座与被测器件要吻合,确保与器件管脚的接触良好,对器件的管脚无损伤。

(6)耐温要求。根据被测器件的最大工作温度范围来确定,满足低温-55 ℃、高温150 ℃的要求。

3.3 测试接口板信号完整性要求

(1)电源资源分配。根据器件工作电源的个数、电压值、电流功耗要求等,按照测试系统的资源能力对电源进行合理的分配。器件的同组电源可以通过增加电源层的方式连接在一起,不同组但电压值相同的电源可以根据器件要求或系统资源情况决定是否分开连接,电压值不同的电源必须进行分开连接。

(2)信号资源分配。大规模集成电路除了电源和地管脚外,对于其他的信号管脚,需要根据信号的传输频率要求分配到测试系统资源上。

(3)布线频率要求。在进行测试接口板设计时,必须要考虑信号的传输频率,不同级别的传输频率对布线的长度、宽度、甚至PCB板材料的要求都不同。

(4)阻抗匹配要求。为了达到信号传输的完整性,对信号传输线进行阻抗匹配。

(5)信号线的等长要求。同一类型的数据线,要进行等长设计,以减少信号传输时延之差,工作频率越高的器件对信号的等长要求也会越高。同类型的信号线要在同一层进行走线。

(6)电源和地要求。测试接口板都有单独的电源层和地层,在每组电源和地之间都要放置一定数量的去耦电容。

(7)信号和元器件标识。好的测试接口板上对信号和元器件都有清晰的标识,便于焊接和调试。如对于多组电源,清晰的标识可使连接时不会出现器件放置方向混乱的情况,避免在调试或使用过程中出现错误,烧坏器件或测试板。

(8)材质要求。测试接口的材质要求与负载板的要求一致。

(9)屏蔽要求。对于系统电磁干扰较为严重的情况,需要采用屏蔽措施。

(10)隔离要求。对于系统地的噪声较大、系统电压差较大等情况,需要采用隔离技术。

4 结论

针对目前缺乏关于ATE测试接口板可靠性评审方法的问题,分析影响可靠性的因素,提取评审要素,提出从负载板可靠性、适配座可用性和信号完整性3个方面对测试接口板可靠性进行评审的方法,具体评审要求为:①负载板可靠性评审要求包括电源、地、信号管脚及接插件的连接方式,适配座的选用,布线方式,负载板的材质、厚度,外围元器件,标识,耐温要求;②适配座可用性评审要求包括耐压要求、电流要求、频率要求、使用次数要求、对器件管脚无损伤、耐温要求;③信号完整性评审要求包括电源、信号资源分配,布线频率要求,阻抗匹配要求,信号线的等长要求,电源和地要求,信号和元器件标识,材质要求,屏蔽要求,隔离要求。该评审方法和要求可为军用超大规模集成电路鉴定检验提供评测依据,为测试程序的运行提供技术参考,增强鉴定检验中大规模集成电路测试的可控性。

参考文献:

[1]曾峰,巩海洪,曾波.印刷电路板设计与制作[M].北京:北京电子工业出版社,2002:63-96.

[2]TOLESCU A, SVASTA P. Characterization of differential interconnects from time domain reflectometry measurements[C]∥ The 24th International Spring Seminar on Electronics Technology. [S.l.]:IEEE, 2001:298-301.

[3]RUBIN B J.Understanding modeling and measurements of differential transmission lines[C]∥IEEE 10th Topical Meeting on Electrical Performance of Electronic Packaging. [S.l.]:IEEE,2001:313-316.

[4]PANTIC-TANNER Z, SALGADO E, GISIN F. Cross coupling between power and signal traces on printed circuit boards[C]∥1998 IEEE EMC Symposium. [S.l.]:IEEE,1998:624-628.

[5]HSU J, SU T, LI Y L, et al. Fast signal integrity methodology for PCB pre-layout analysis and layout quality check[C]∥2013 IEEE 63rd Electronic Components and Technology Conference. [S.l.]:IEEE, 2013:2012-2017.

[6]SEUNGYOUNG A,LU A C W,WEI F, et al. Effects of process variation on signal integrity for high speed differential signaling on package level[C]∥The 4th Electronics Packaging Technology Conference. [S.l.]:IEEE,2002: 249-253.

[7]于学萍,吕英华,冯晓俊,等.割裂大地对数字信号的影响[J].电波科学学报,2002,17(5):490-494.

[8]宋占海,刘元安,黎淑兰,等.对垂直交叉线中串扰的分析[J].电波科学学报,2003,18(4):457-461.

[9]张建新.高速PCB的信号和电源完整性问题研究[D].西安:西安电子科技大学,2012.

[10]GRANBERG T. Digital techniques for high-speed design[M].[S.l.]:[s.n.], 2006:6-23.

[11]曲咏哲,李玉山,闫旭,等.电容耦合连接器及其信号完整性分析[J].西安电子科技大学学报(自然科学版),2011,38(5):159-164.

[12]ZHANG M S, MAO J F, LONG Y L. Power noise suppression using power-and-ground via pairs in multilayered printed circuit boards[J]. IEEE Transactions on Components,Packaging & Manufacturing Technology, 2011,1(3):374-385.

[13]贺晓燕,陈兵,汪慧,等.基于 C/S 结构的元器件管理系统的设计与实现[J].武汉理工大学学报(信息与管理工程版),2015,37(2):143-146.