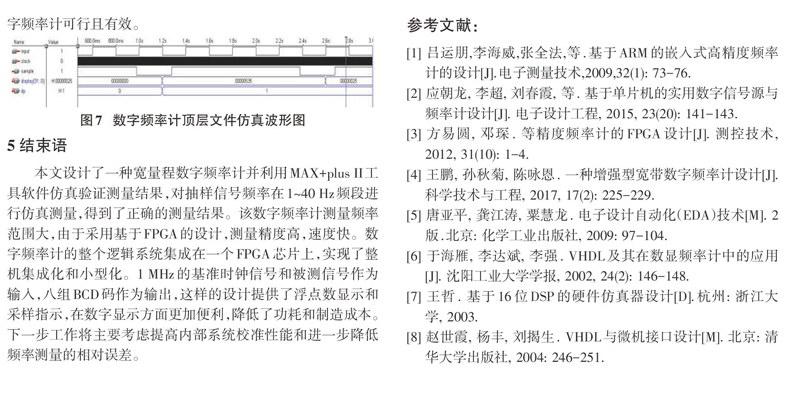

一种宽量程数字频率计的设计与仿真

2018-04-02邱鹏张建德霍瑛

邱鹏 张建德 霍瑛

摘要:为了快速准确获得各种电子信号的频率,设计了一种基于FPGA(Field Programmable Gate Array)的宽量程数字频率计,该频率计运用自顶向下的设计思想,采用将系统按功能划分模块的设计方法。以FPGA为开发平台,通过VHDL语言编程来设计数字频率计各个模块,从而更大限度地满足测量范围、精度和速度的要求。最后,使用MAX+plusII软件仿真数字频率计测量结果,进一步证明了该数字频率计的有效性和可行性。

关键词:频率;数字频率计;FPGA;MAX+plus II;VHDL语言

1背景

在电子通讯系统中,频率是最基本的参数之一,而测量频率是电子测量技术中最常见的参量测量之一,不少物理量的测量都涉及或本身就可转化为频率的测量。基于单元电路或单片机设计的传统频率计无论是在测频范围、精度、操作以及功能上都不十分理想,虽然目前市场上有各种多功能,高精度、高频率的数字频率计,但价格都很昂贵。

2相关研究

频率计的作用是测量被测信号的频率,但是由于被测信号在不同场所所处的频段不同,变化范围不同,同时对测量的精度也有不同的要求,因此产生了不同的频率测量方法。大多数传统数字频率计测量范围小、精度低、速度慢。随着单片机的出现和发展,一定程度上优化了数字频率计的测量功能,但单片机本身存在工作频率以及其他因素的影响,比较适用于低频段测频,而在高频段利用测频的方法,其精度往往会随着被测频率的上升而降低,因此设计一种能在整个测试范围内维持恒定的测试精度及造价低廉的频率计就显得十分必要了,特别是在数字频率计软硬件结合设计中,需要考虑测量周期、频率和占空比等性能因素。FPGA具有以下优点:其单片逻辑门数已达到上百万门,实现的功能越来越强大;不需要设计人员承担芯片投资风险和费用;用户可以反复地编程、擦除、使用,或者在外围电路不动的情况下用不同软件就可以实现不同的功能等。

基于对以上各因素的考虑,在FPGA开发平台上使用VHDL编程语言设计数字頻率计能够有效扩大测量范围、提高测量精度和加快测量速度。

3宽量程数字频率计的设计方案

3.1设计思路

根据设计的要求,需要对数字频率计的测量范围进行划分。首先,频率计的测量范围设定在0.01 Hz-18 MHz之间,整个量程被分成四段的目的是可以给频率计提供测量精度保证,四段量程依次是:甚低频段0.01-0.1 Hz,低频段0.1-1 Hz,中频段1-40 Hz,高频段40 Hz-18 MHz。在高频段使用直接记数法的同时提供八位整数,而在其他频段都采用先测周期再求倒数的方法进行测量,测量结果保留三位有效数字,使用浮点数显示。