高速并行成型滤波器的FPGA实现方法

2018-04-02张志芳沙立伟宋振宇

单 琦 ,张志芳 ,沙立伟 ,张 晔 ,宋振宇

(1.航天恒星科技有限公司北京100086;2.天津航天中为数据系统科技有限公司天津300301;3.北京信威永胜通信技术有限公司北京100193)

现代通信系统中,在信号传输过程与接收过程中,码间串扰(ISI)是造成误码的主要原因之一[1-2]。成型滤波器用来减少码间串扰,提高频带率用率[3-4]。在利用FPGA实现成型滤波设计时,目前常规的做法主要查表法,查表法的基本原理是通过对输入信号与单位冲击响应进行线性卷积来实现数据的成型,查找法预先将信号所有可能的成型后的基带波形样本值存储起来[5-6],随着成型滤波器系数的增加,这种卷积运算会占用大量硬件资源,并导致延迟增大,设备成本增加。为了避免过多硬件资源的占用,又提出了分布式算法[7],分布式算法利用ROM查找表,将固定系数的乘累加运算转换成查找表操作,从而避免了乘法运算,查找表后的数据执行的都是简单的加法运算。为了实现高速数据速率的需求,进一步提出了并行的分布式算法[8-10],利用并行结构和滤波器的系数对称性等对于分布式算法进行改进,但是当阶数增大时,无论是分布式算法还是并行分布式算法的查找表规模仍然成指数增加,造成FPGA资源紧张。文献[11]和[12]针对特定调制方式的查找表方法进行了分析,但不具有普适性。

在成型滤波的实现过程中还有一个主要的要求就是数据速率可变,为了能够适应数据速率的变化,目前主要的处理方式是采用插值和抽取相结合的方式实现分数倍采样[13-15],这种方式实现复杂,占用硬件资源较多。文献[16]中利用改变采样时钟的做法实现变速率采样,这种方法需要产生多个采样时钟,系统不够稳定。

基于此,文中提出了一种高速并行成型滤波器的FPGA实现方法,有效降低了系统资源的占用,并且能够灵活适应高速可变数据速率的要求。

1 基于群时延的串行成型滤波器设计

针对目前成型滤波器实现中的问题,文中提出了一种新型的基于群时延结构的查找表算法。成型滤波器采用波形拟合的方法产生,通过简单的查表法来实现。首先用Matlab程序计算出成型滤波的波形数据,调用Matlab函数

其中,rcosine用于生成成型滤波单位脉冲响应波形采样数据,Rate为数据速率,此处可设为1;Fs为采样率,文中设为1024;fir/sqrt表示根升余弦FIR滤波器;alpha为滚降系数[17],范围 0~1;group_delay为群时延[17]。

将生成的系数y经过归一化处理后,放入到FPGA的查找表中。查找表总深度为2*group_delay*Fs/Rate,由此可知,查找表深度与阶数成正比,与目前常规算法的指数式增长相比占用资源很少。

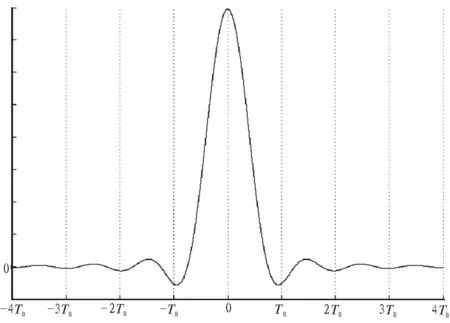

图1 成型滤波波形图

如图1所示,令群时延为4,则前后共有8个码元相关,将(-4TB,4TB)共8个码元周期的波形分为8段,每段长度为一个码元周期TB,将其作为一个查找表的数据,每个采样点的数值量化为12位补码。

根据NCO理论,码元数据时钟相位的生成采用计数器累加的方法实现,时钟相位累加步进值的计算公式为

其中R为符号速率,fclk为系统时钟频率,即FPGA工作时钟频率。每个系统时钟周期内,相位值增加E。设相位累加值s0的初始值为0,经过若干周期的累加后,相位值达到2N时,则生成一个数据读取脉冲data_clkp作为数据源产生模块的读取脉冲,数据源产生模块响应读取脉冲输出一个新的码元符号作为成型滤波的输入数据。将采样率设为1 024,也就是说每个TB时间段内采样1 024个波形点来存储,因此只需取相位累加值s0的高10位phase0(phase0=s0[N-1:N-10])作为查找表的地址,读取对应的滤波数值。

前后8个码元相关,共需8个查找表,每个查找表分别存储(-4TB,-3TB)、(-3TB,-2TB)、(-2TB,-TB)、(-TB,0)、(0,TB)、(TB,2TB)、(2TB,3TB)、(3TB,4TB)时间段内的采样数据,共有8*1 024=8 192个数据。将前后相关的几个码元的成型滤波波形数据相加就得到最终的成型滤波输出。

当数据速率改变时,只需修改式(2)中的符号速率R值就可以实现变速率采样。

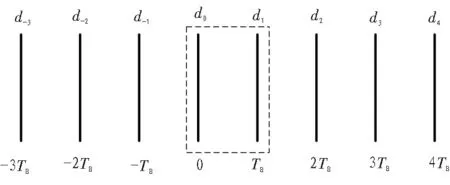

图2 0~TB时间段内输出波形对应数据值

如图 2所示,令di表示在iTB~(i+1)TB时间段内的进入成型滤波器的有效码元,以d4进入成型滤波器的时间段4TB~5TB为例,每个数据用一个脉冲表示,由于群时延的影响,此时输出的波形应该是0(4TB-4TB=0)~TB(5TB-4TB=TB)时间段内的波形数据,以8个脉冲的生成时刻作为各自成型波形的0时刻,在上图中画出各个脉冲的成型波形后,将所有在0~TB范围出现的波形值相加就得到了这个时间段内的成型滤波输出。将所有出现在0~TB范围内的波形列出如下:

d4输出(-4TB,-3TB)的数据

d3输出(-3TB,-2TB)的数据

d2输出(-2TB,-TB)的数据

d1输出(-TB,0)的数据

d0输出(0,TB)的数据

d-1输出(TB,2TB)的数据

d-2输出(2TB,3TB)的数据

d-3输出(3TB,4TB)的数据

成型滤波查找表读出的波形数据是输入数据有效值为“1”时对应的值,若输入数据为“0”,则应对查找表读出的数据取反来得到滤波结果输出,这个处理过程实际上就是用输入数据d4~d-3与查表输出的波形值作乘法,即用d4~d-3加权,可以简单的用对应的d4~d-3的值与成型滤波查找表读出的波形数据相“与”来实现,再将8个经过“与”处理的结果相加就得到0~TB时间段范围内的成型滤波输出。

2 并行成型滤波器实现方法

小节1中所述的成型滤波实现方法只适用于串行输入的情况,成型滤波模块每输入一个码元符号就对应输出一个成型滤波结果,但是随着数据速率的升高,在新一代的数传系统中,符号速率可能达到几百甚至几千兆,如果仍然采用串行方式实现成型滤波波器的设计就显得力不从心。此时要求成型滤波模块一个系统时钟周期输入并行的多个码元符号,并能够产生相应的多个并行成型滤波输出数据。由于成型滤波的群时延特性,多个码元符号之间并不是相互独立的,如小节1中所述,若群时延为4,则每个码元符号都影响着前后4个码元符号的成型滤波输出结果。下面以16路并行成型滤波为例,说明并行成型滤波器的设计方法,更高并行度的成型滤波设计可以以此类推。

在16路并行成型滤波器的设计中,成型滤波模块的输入为来自数据时钟产生模块的16路并行时钟相位值、16路并行数据的数据读取脉冲data_clkp和来自数据源产生模块的16路并行数据。

在并行数据时钟产生模块的设计中,由于每路数据时钟是独立生成的,因此每路时钟相位的累加步进值E的计算方法与串行时一致,与串行的情况不同的是,由于每个系统时钟周期要产生16路不同的相位值,因此各相位累加值s0~s15的初始值initial_phase0~initial_phase15之间的差值为E/16,每个系统时钟周期,各路的相位累加值s0~s15增加E,第16路相位累加值s15经过若干周期的累加后,达到2N时,则生成一个数据时钟脉冲data_clkp作为数据源产生模块的读取脉冲,数据源产生模块响应data_clkp输出并行的16路数据。

在并行成型滤波模块中,由于前后共8个码元相关,因此同时输入的每个码元符号都需要寄存在一个8个元素的移位寄存器数组中,具体来说,若同时输入的是16个并行的码元符号d0_new~d15_new,则16个移位寄存器数组为

其中d0~d15为前一数据读取脉冲送入的16路并行码元符号,d0_new~d15_new为当前时刻数据读取脉冲送入的16路并行码元符号。

在串行处理时,一次处理一个码元,所以时钟相位的值只需要取一个码元周期内的值0~210-1(采样率为210),共10bit的相位信息;在16路并行处理时,一次处理16个码元,那么意味着时钟相位要能够表示16个码元周期内的相位变化,即0~214-1(214=16*210),只有这样才能表示出当前的时钟相位对应16路并行码元中的哪一个。设时钟相位为phase0~phase15(共14位,分别取s0~s15的高14位),则结合并行的移位寄存器组中的数据的移动,FPGA用不同的移位寄存器组计算成型滤波输出波形数据,时钟相位phase0~phase15的高4位用来确定当前的成型滤波结果应该用哪个移位寄存器组来计算,而低10位则用来确定成型滤波结果应该用每个查找表内的具体波形地址,将查表的结果与对应的码元符号相“与”再相加就得到最终的成型滤波结果。

还有一点需要特别说明,由于数据读取脉冲采用的是最后一路相位累加值s15累加到2N时输出的读取脉冲,而第一路相位累加值s0与s15之间相差了15E/16,也就是说s0的读取脉冲与s15的读取脉冲之间最多相差小于一个系统时钟周期,当对应于s15,在数据读取脉冲有效时,已经更新了16路并行数据时,s0此时可能还未累加到2N,而是经过一个系统时钟周期(由于两者相差不到一个E,因此最多经过一个系统时钟周期)后才累加到2N,同理,其他各路相位累加值s1~s14与s15也都有相位差,也可能要经过一个系统时钟周期才达到累加门限,因此在这个读取脉冲内,s0应该采用的成型滤波移位寄存器组的值应该是上一次更新时的值,两组移位寄存器组之间相差了一个系统时钟周期。因此在计算时还要保留移位寄存器组的前一时刻的采样值,这在FPGA中很好实现,只要用系统时钟对于data_array_new0~data_array_new15进行采样即可。设采样后的移位寄存器组为data_array0~data_array15,在成型滤波模块输入的数据读取脉冲(对应s15的数据读取脉冲)有效时,其他各路s0~s14所对应的移位寄存器组应根据s0~s14的最高位来判断,若最高位为0,则移位寄存器组则采用data_array_new0~data_array_new15,否 则 就 采 用data_array0~data_array15作为成型滤波计算时应用的移位寄存器数组。

3 并行成型滤波处理仿真结果

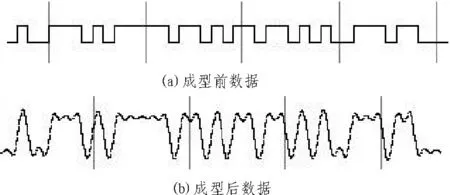

采用上述小节2所述的方法,利用ISE和ModelSim对于并行成型滤波器进行仿真,成型滤波处理前后的数据分别如图3(a)和(b)所示。由图3可以看出,文中所述成型滤波方法能够准确的对于输入数据进行成型滤波处理。

图3 成型滤波仿真结果

4 结 论

文中详细阐述了一种新型的高速并行成型滤波的FPGA实现方法,该方法结合系统的群时延特性,构造成型滤波实现的并行结构,利用数据时钟相位对于查找表进行寻址,能够灵活的实现变速率采样,使该种方法能够适应现代通信系统对于高速可变数据速率的处理要求,具有广泛的应用前景。

参考文献:

[1]孙京蕾.QAM调制技术研究[D].南京:东南大学,2012.

[2]王志远.平方根升余弦滤波器的FPGA实现[J].中国新技术新产品,2012(6):23.

[3]王相龙.多制式宽带通信信号模拟系统软件设计与实现[D].成都:电子科技大学,2014.

[4]季伟,周学军,林海涛,等.基带成形滤波器设计与实现[J].舰船电子工程,2012,32(2):131-133.

[5]牛明.基于脉冲成型的OFDM系统峰均比抑制[J].自动化技术与应用,2016,35(3):42-46.

[6]王顶,刘智朋,赵颐轩.基带成形滤波器的数字设计与实现[J].电子设计工程,2012,20(13):95-97.

[7]李艳萍,周胜源.高速成形滤波器的研究与实现[J].电子设计工程,2012,20(8):103-105.

[8]王战强,王大庆.高速通信QPSK数字调制器设计与实现[J].空间电子技术,2015(6):50-57.

[9]包可佳,唐琦.基于FPGA的高码率QPSK信号产生方法[J].信息通信,2015(9):82-84.

[10]吴凤辉,迟永钢,郑宇希,等.一种改进DA算法的成型滤波器设计[J].哈尔滨工业大学学报,2016,48(5):32-35.

[11]徐兰天.EDGE中8PSK调制的软件实现[J].电子产品世界,2013(10):31-33.

[12]梁尧,周智勋,何丽.一种基于查找表的FIR成型滤波实现装置[J].太赫兹科学与电子信息学报,2015,13(1):102-105.

[13]孙洁朋.多体制通信基带信号产生模块的设计与实现[D].成都:电子科技大学,2014.

[14]卢佳欣,周志刚,王丽云,等.E波段微波传输系统发送滤波模块的FPGA设计[J].高技术通讯,2014,24(9):922-927.

[15]冯佳梅,邹刚,朱南,等.基于可变带宽多速率处理算法的设计与实现[J].数字电子世界,2015(8):325-326,332.

[16]田之俊,段旭.高速可变速率QPSK模拟源设计与实现[J].无线电工程,2015,45(11):77-80.

[17]樊昌信,曹丽娜.通信原理[M].北京:国防工业出版社,2014.