《数字电子技术与逻辑设计》教学及考试方法改革的探索

2018-04-02王睿庭

王睿庭

(天水师范学院 电子信息与电气工程学院,甘肃 天水 741001)

0 引言

《数字电子技术与逻辑设计》是高等院校电子信息类特别是电子信息工程专业学科中一门重要的基础必修课,而目前大部分学校的教学内容仍停留在讲解以74系列器件为核心的手工分析和设计技术,而考试方法也只是传统的试卷答题,殊不知这样其实脱离了科技进步和时代要求,忽略了对于学生实践能力的培养,学生只擅长纸面答题而动手能力很差,从而偏离了最初的教学目标和教学要求,是有悖于我们培养应用型创新人才的。就此,笔者结合本校本专业的教学实际,对电子信息工程专业 《数字电子技术与逻辑设计》这门课做了教学及考试方法改革方面的探索。

1 教学改革

从14级电子信息工程专业开始,《数字电子技术与逻辑设计》这门课设置在大二第3学期,理论授课64学时,实验16学时。笔者对教学内容作了改进,将理论授课的64学时分成两大部分,48学时用于讲解传统数字电子技术的基础知识,重点在逻辑门、逻辑代数、组合逻辑电路的手工分析和设计及典型电路、触发器以及时序逻辑电路的手工分析和设计及典型电路;16学时用于讲解现代自动化设计方法,采用原理图设计和Verilog HDL相结合的设计方法实现组合电路和时序电路的自动化设计。重点使学生掌握原理图输入的设计方法。

2 考试方法改革

摈弃传统试卷答题的考试方法,减少对于传统数字电子技术相关理论的考核,适应时代要求,侧重于考核学生对于现代数字电路自动化设计与分析的能力,旨在培养学生的实践能力,激发创新意识,增强自主创新能力。从14级电子信息工程专业开始,考试拟采用学生分组完成设计并答辩的方式。考试在12周给学生公布设计题目,2人一组,根据题目要求用FPGA开发板完成设计,考试时学生先进行讲解并在开发板上演示,由监考教师提问、学生答辩,最终根据每组设计完成情况及有无创新,组内成员分工及答辩情况评定成绩。

3 设计实例

下面笔者通过一个智力竞赛抢答器的设计实例来说明改革的实施及效果。给学生公布的设计内容和要求如下:

设计一个4人智力竞赛抢答器。设置一个主持人“复位”按钮,主持人复位后,开始抢答,当某一选手首先按下抢答开关时,相应指示灯亮,数码管显示抢答得胜的选手号,此时抢答器不再接受其他输入信号,使除第一抢答者外的按钮不起作用,主持人复位后,重新开始抢答。

扩展功能:

(1)抢答时间有限制,如 10S,抢答成功时伴有声音鸣叫指示;

(2)增加答题环节,具有倒计时及计分功能。

(3)进一步增加至 6人或 8人抢答。

设计题目分为基本要求和扩展功能两部分。只完成基本要求的按及格评分,完成扩展功能越多及自己有创新的得分越高。未实现基本要求的不允许参加考核答辩。

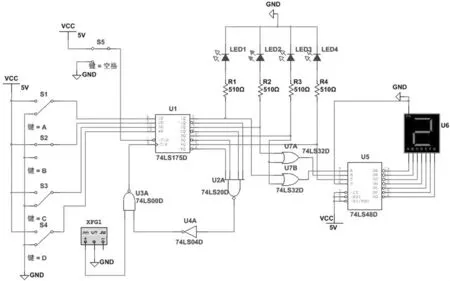

学生接到题目之后便开始查找资料,参阅文献,提出设计方案。要求用到74系列芯片的设计必须用Multisim软件仿真完成。图1所示是用Multisim软件对于4人智力竞赛抢答器的仿真结果。

图1 4人智力竞赛抢答器的Multisim仿真结果

S5为主持人“复位”键,低电平有效,S1至S4对应1~4号选手按键,高电平有效,采用的是74LS175四位寄存器方案。当然,从图中可见,只完成了设计题目的基本要求。

与《数字电子技术与逻辑设计》配套的有《数字电路综合设计》课程设计,为期两周,共计24学时,这是学生能完成相应设计题目的保障。在 《数字电路综合设计》开始会给学生讲解用FPGA开发板实现8位数码管的动态扫描显示、分频的实现及蜂鸣器的用法等知识,后面留给学生时间完成自己的设计题目。

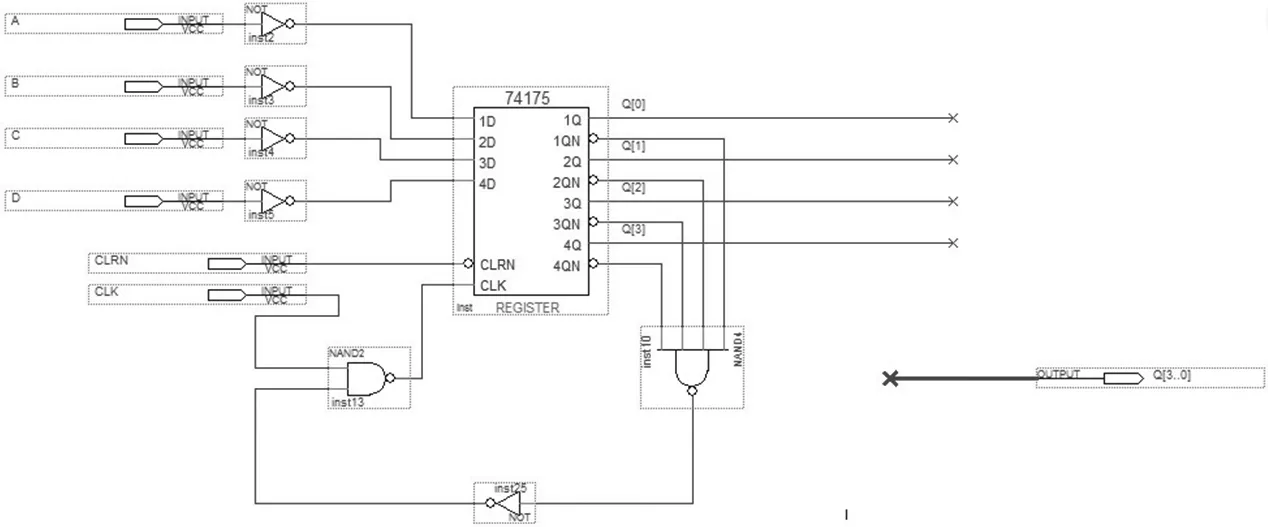

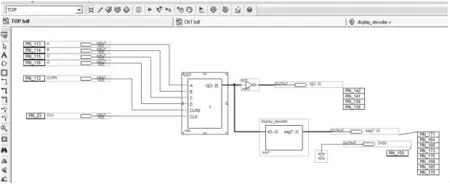

考核的要求之一是必须用QuartusⅡ软件完成设计,并最终下载到开发板上测试验证。学生对于如何将自己的Multisim仿真转到QuartusⅡ软件完成存在或多或少的疑问,这时候,笔者会给学生强调,只需将Multisim下面的按键或单刀双掷开关去掉,输出的LED灯及数码管也去掉,QuartusⅡ下取而代之的是输入输出管脚,因为开发板上面FPGA和开关、LED灯及数码管等等的线已经连好了,我们只需要做的就是分配引脚,就是把你的设计端口对应到某个输入或者输出上。图2所示是QuartusⅡ软件下实现的对应图1 4人智力竞赛抢答器的Multisim仿真的逻辑电路部分,电路得到了大大简化。74系列芯片取而代之的是QuartusⅡ软件下的74系列宏模块。

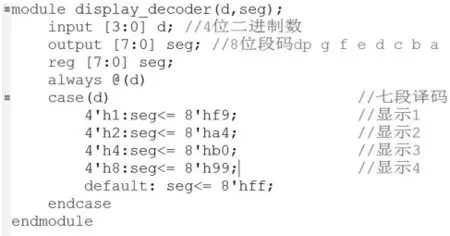

74LS48显示译码器的逻辑功能可以用Verilog HDL很方便地实现,如图3所示。当然,对于Verilog HDL的基础语法知识不必过多去强调,只需要让学生能按照格式去套用,明白case语句的使用方法就可以了。

图2 QuartusⅡ软件下实现4人智力竞赛抢答器

图3 Verilog HDL实现显示译码

图4 4人智力竞赛抢答器顶层电路图

最终完成的顶层设计如图4所示。

可见,本例采用了原理图设计和Verilog HDL相结合的设计方法,这也是推荐给学生最有效、直观便捷的方法。

4 结语

经过三年多教学改革及考试方法改革的探索和实施,目前已初见成效,学生学习的兴趣得到激发,主动性和动手实践能力大大提高,然而,能完成扩展功能设计或自己有创新的学生比较少,还需加强培养学生的创新能力,进一步改进教学。

【参考文献】

[1]潘松,陈龙,黄继业,著.数字电子技术基础(第二版)[M].北京:科学出版社,2014.

[2]宋伟,朱幼莲.“数字电路”课程设计教学改革探索[J].江苏技术师范学院学报,2011,17(8):70-73.

[3]张正明,王丽娟,王红航.关于数字电路设计技术的几点思考与实践[J].数字技术与应用,2012,(9):121-122.

[4]李旭,张为公.基于科研项目的数字电路创新型实验教学改革[J].实验室研究与探索,2015,34(1):168-171,209.

[5]吴杰,杨青胜等.师范院校《数字电子技术》课程教学改革探索[J].湖北师范大学学报(自然科学版),2017,37(4):96-99.