基于光纤通道数据收发系统的设计与实现

2018-03-29高润莲

高润莲 ,周 晴

(1.中国科学院大学北京100190;2.中国科学院国家空间科学中心,北京100190)

随着计算机技术、数据通讯技术和网络技术的发展,信息时代数据量的爆炸增长给存储传输技术的发展提供了良好的机遇,如何对数据进行安全快速远距离的存储、传输、管理以及使用成为了现代通信存储技术的主要要求。而对于航空航天电子系统而言,也同样面临着对数据通信在可靠性、数据吞吐率、实时性等方面越来越高的要求,目前光纤通道通信网络已成为新一代航空电子系统的主流技术[1-2]。

光纤通道作为代替现代航空电子总线的网络,具有高带宽、低延迟、拓扑灵活、长距离传输,支持多种上层协议[3]。目前对于光纤通道的研究只要集中于对协议的研究和协议框架的设计:文献[4]提出一种基于光纤通道接口通用驱动程序的设计方案;文献[5]提出光纤通道现状和发展趋势;文献[6]提出光纤通道与MIL-STD-1553协议兼容性设计方案;文献[7]提出一种光纤通道协议分析与接口卡设计方案。

文中主要讲述基于光纤通道FC-AE-1553协议的数据收发系统的设计,以及各模块作用进行说明。采用Xilinx的Virtex-4实现FC-0、FC-1以及部分的FC-2层的功能,通过上板调试,从而实现点对点数据传输通信,经过实验证明,该数据收发系统方案可行。

1 光纤通道协议架构及帧结构

光纤通道 OSI(OpenSystem Inter-connection)模型分为5层[8-9],分为两个部分:物理和信号层,上层协议层,如图1所示。物理和信号层包括FC-0,FC-1,FC-2层,上层协议层包括FC-3,FC-4层。其中物理层由传输介质、发送机和接收机及其接口组成;编码层采用8B/10B编码;协议层规定了端到端数据块的传输机制;通用服务层提供了一组对FC节点上的多个N端口通用的服务。FC提供支持多种ULP(Upper Layer Protocal)的方法。

光纤通道协议规定在光纤通道中传输的3个级别的数据结构:交换,序列和帧。交换是数据传输的最高层,一次交换表示两个节点之间的一次信息交互过程,可包含一个或多个序列的传输。序列是一个数据报或者分组,一个序列可以包含一个或多个帧。帧是网络中两个节点进行信息交互的基本数据单元。FC-AE-1553帧格式由一个SOF、帧内容和EOF组成[10-11]。帧内容包括帧头、0-2112字节数据字段和32位CRC校验码。另外,光纤通道定义了3种服务类[12]。这些服务类按N端口间通信回路的配置和保持方法,以及系统的传输完整性要求来区分:第1类服务是建立专用连接的服务。这类服务通过在两个N端口间建立连接,保证获得最大带宽;第2类服务是一种按帧大小传输的、带有交换网多路复用帧的无连接服务。如果没有交换网,则这种服务就变成一种特殊的点对点服务。在没有链路错误时,交换网能保证给出交付成功或交付失败的通知;第3类服务是一种按帧大小传输的、带有交换网多路复用帧的无连接服务。第3类服务只支持无确认帧的交付。其中目的N端口在收到有效数据帧时不发送任何确认链路控制帧,所有确认都是由ULP确定和实现的。为了数据的快速传输,本论文采用第3类服务,只支持无确认帧的交付,目的N端口在收到有效数据帧时不发送任何确认链路控制帧。

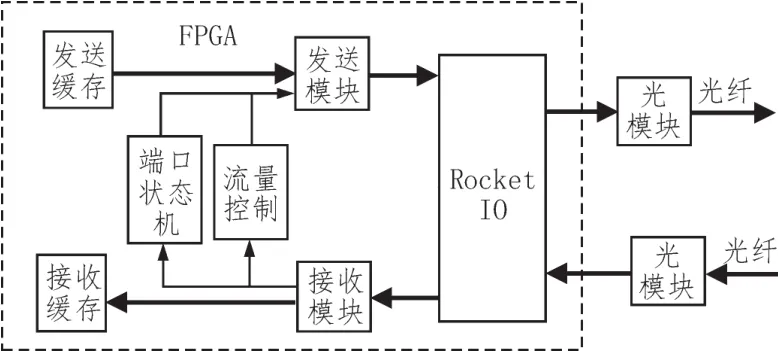

2 系统总体方案设计

本方案是针对1.062 5 Gbps的光纤速率设计的,系统总体方案如图1所示。该系统主要由发送缓存、接收缓存、发送模块、接收模块、端口状态机、流量控制模块和光模块组成,除光模块以外的其他模块都由FPGA完成。本方案FPGA采用Xilinx公司Virtex-4系列的XC4VFX60芯片,该芯片包含16个RocketIO模块。RocketIO为622 Mb/s到6.5 Gb/s波特率的全双工串行收发器[13],可以实现数据的高速串行传输。光模块采用Eoptolink公司的EOLP-1380-10芯片,该芯片支持1.062 5 Gbps到8.5 Gbps的数据传输。参考时钟来自外部晶振,选用的是泰艺公司的OT-M-212.5M的差分晶振,输出波形为方波,输出电压为3.3 V。

图1 光纤通讯控制FPGA

3 系统各模块详细设计

本系统主要由发送模块、接收模块、端口状态机、流量控制模块、RocketIO和光模块组成。发送模块完成组帧、CRC校验、8b/10b编码等功能;接收模块完成逗号检测、8b/10b解码、解帧等功能;端口状态机完成链路状态之间的转换功能;流量控制模块完成两端口之间流量的控制;光模块实现电信号与光信号的相互转换,通过光纤传输光信号。

3.1 发送模块

发送模块具体框图如图2所示。Tx_buffer通过FIFO实现,将要发送的数据输入到发送缓存,通过Tx_control模块来确定端口此时处于发送数据帧、原语序列还是原语信号的状态。其中原语序列来自端口状态机,原语信号来自流量控制模块,帧内容来自发送缓存。当端口状态机处于激活状态时,Tx_control模块控制Tx_buffer的读使能(rd_en)有效,从而将数据从Tx_buffer中读出;CRC32模块用来计算数据的校验码,采用32位数据并行校验的方法[14];EOF_Polarity模块用来计算数据帧结尾的RD值,从而确定EOF的值;Tx_SOF_Select模块用来确定SOF的值,不同的服务类型SOF的值不同。Tx_control将数据组帧,帧格式如图2所示。Demux_32to8模块将32位的数据解复用为8位串行数据,以便数据进行8b/10b编码,将编码后的值送入RocketIO进行并串转换。

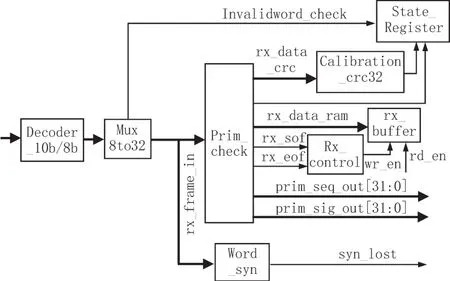

3.2 接收模块

接收模块具体框图如图3所示。接收到的串行数据经过RocketIO的串并转换模块转换为并行数据后,通过Decoder_10b/8b模块进行解码,解码得到的数据经过复用(Mux_8to32)之后送入原语检测模块(Prim_check)和字同步模块(Word_syn)。Prim_check模块的主要功能检测接收到的数据是原语信号、原语序列还是传输的数据,从而送到相应模块进行处理,其中原语信号送到流量控制模块,原语序列送到端口状态机模块,而传输数据送到CRC校验模块(Calibration_crc32)和接收缓存模块(rx_buffer)。另外通过监测数据的帧起始与结束标识符,判断数据帧是否完整及数据帧的长度。Calibration_crc32模块主要负责为将接收的数据(不包括SOF和EOF)进行CRC校验,从而判断数据在传输过程中是否出现错误。rx_buffer模块负责缓存接收到的数据帧(包括SOF和EOF),通过Rx_control模块来控制数据帧的写入。Word_syn模块负责判断硬件模块是否字同步,如果接收端接收到的位流的传输字与发送端发送的传输字一样,那么应实现传输字同步,条件满足时进入同步获取状态,从而使端口状态机(PSM)一直处于激活状态。State_Register模块主要功能是记录每一帧数据帧的长度以及对应的错误类型(如果传输过程中出现错误),主要包括无效传输字、CRC校验错误、无效EOF、数据帧不完整及帧长度溢出这几种错误。

图2 发送模块框图

图3 接收模块框图

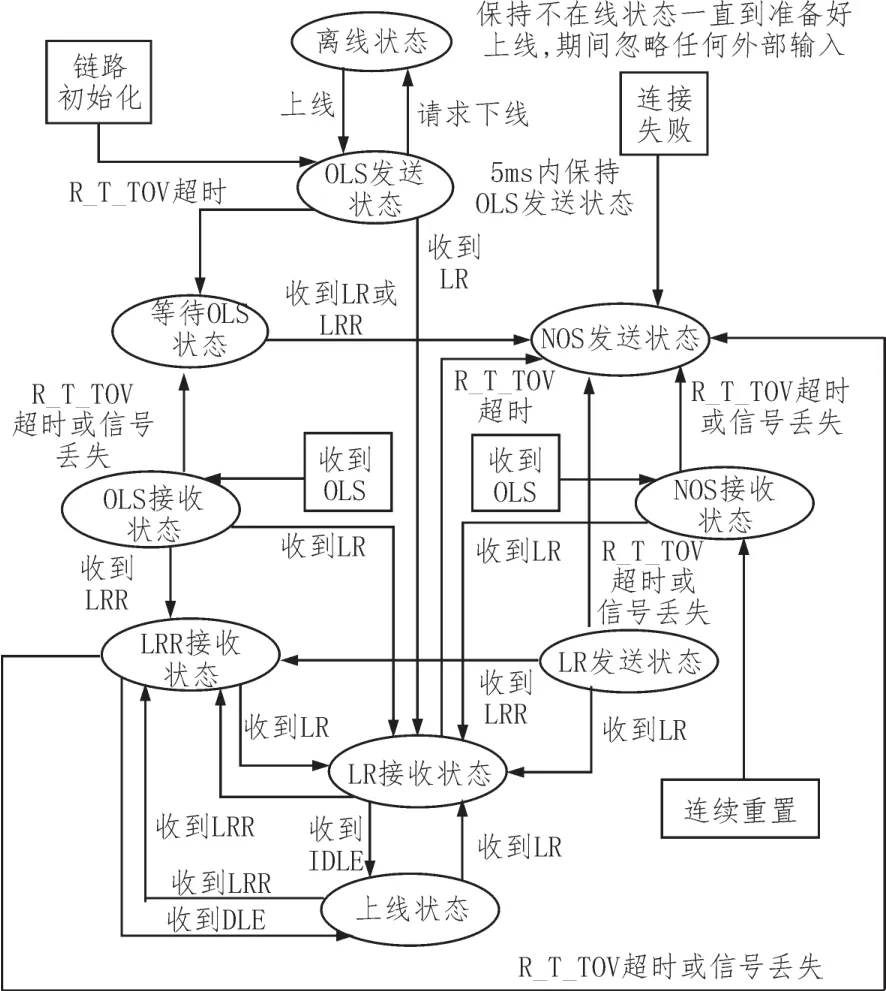

3.3 端口状态机

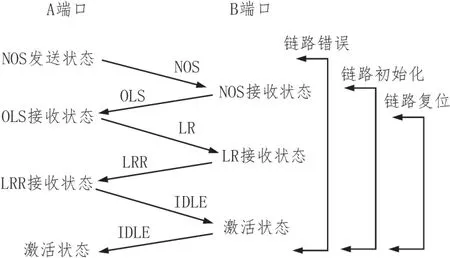

根据FC-AE-1553协议规定,在端口进行正常通信之前,端口状态机要处于激活状态。协议定义了一系列的原语序列用于表示端口状态,并且详细叙述了端口状态机的实现方法。原语序列是一个连续重复发送的有序集,若端口遇到了特殊情况,或一个端口的接收机逻辑碰到了特定的条件,就发送原语序列。如图4为端口状态机的状态转移图[15]。当端口上电或复位后,处于未激活状态,需要通过光纤协议定义的握手机制恢复到激活(上线)状态。光纤通道协议规定使用的原语序列协议有3种,分别为:链路初始化协议、链路失效协议和链路复位协议[16]。当端口检测到同步丢失时间超过R_T_TOV,或不在离线状态时检测到信号丢失时,端口应执行链路失效协议。具体实现步骤如下:1)当A端口中存在链路失效条件时,端口应发送NOS(Not Operational Primitive Sequence)并进入NOS发送状态;2)B端口接收到NOS时,进入NOS接收状态,发送OLS(Offline Primitive Sequence);3)A端口接收到OLS,进入OLS接收状态,发送LR(Link Reset Primitive Sequence);4)B端口接收到LR时,进入LR接收状态 ,发 送 LRR( Link Reset Response Primitive Sequence);5)A端口接收到LRR时,进入LRR接收状态,发送 IDLE(Idle Word);6)B端口接收到IDLE时,退出LR接收状态进入激活状态,A端口在接收到IDLE时,也退出LRR接收状态进入激活状态。同理,链路初始化协议和链路复位协议执行过程如图5所示。图5为这3个原语序列的恢复过程和层次,通过这3层结构端口可以最后达到激活状态[17],从而确保端口之间能够进行数据传输。

图4 端口状态机状态转移图

图5 链路恢复协议的3层结构

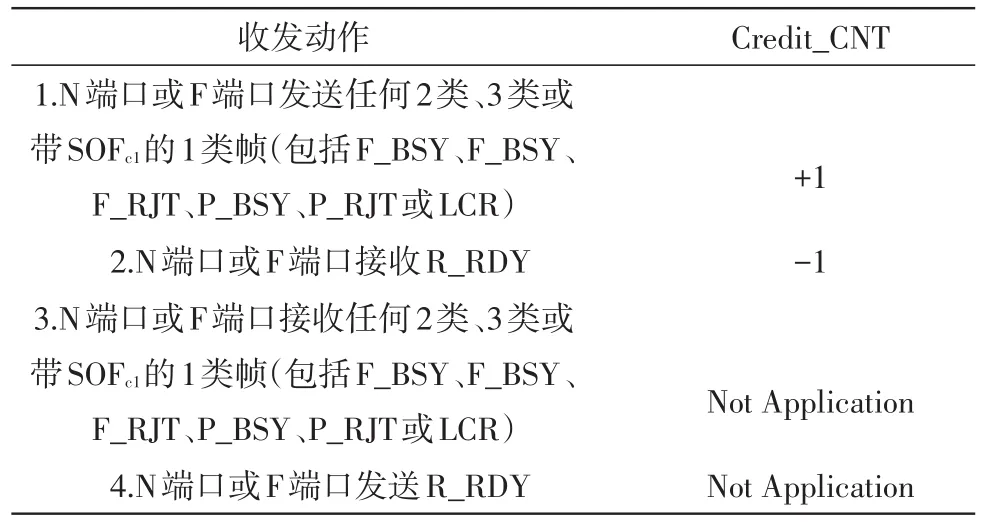

3.4 流量控制模块

流量控制是FC-2层的控制过程,用于跟踪N端口之间、N端口与交换网之间帧的传输。流控制分为端到端流控制和缓冲区到缓冲区流控制。本论文使用第3类帧,只使用缓冲区到缓冲区流控制。缓冲区到缓冲区流量控制管理见表1所示[9]。信用是分配给传输端口的接收缓冲区的数量。信用计数由序列启动方进行管理。首先确定对方的信用即对方可以接收多少帧数据。每发送一帧数据信用计数(Credit_CNT)加1,直到加到信用规定的最大值为止。在这种情况下,信用计数代表序列接收方还没有确认的重要数据帧的数目。当序列启动方接收到来自接收方的

R_RDY(32’hbc954a4a)信号时,信用计数减 1,序列启动方可继续发送数据。

表1 缓冲区到缓冲区流量控制管理

3.5 RocketIO收发器

收发器的工作原理是发送端按照一定的计算规则产生的CRC校验码被插入到准备发送的并行数据中,经过8B/10B编码(8B/10B编码可根据需要选择),写入发送FIFO,然后将其转换成差分信号发送出去[18]。接收端通过接收器接收串行差分信号,在时钟数据恢复电路的作用下,从串行数据流中恢复出时钟信号,该时钟信号用于串/并转换,在comma检测和对齐模块的作用下,将数据对齐进行串并转换,输出的并行数据经过8B/10B解码(可根据需要选择,与发送端选择一致),依据需要用弹性缓冲器实现通道绑定和时钟修正,经过CRC模块校验后并行输出。本方案中只使用RocketIO中的PMA(physical media attachment)部分。

4 仿真结果

本论文对光纤通道数据收发系统光纤通讯控制FPGA进行仿真,通过chipscope抓取波形如图6所示,tx2_top_module模块的frame_out表示发送端发出的数据帧,rx2_module模块的frame_in为接收端接收到的数据帧。由图6(a)可以看出,当有一帧数据从接收FIFO取出后,接收端发送原语信号R_RDY进行原语控制。图(b)(c)为图(a)放大后的时序图,可以看出接收端接收到的数据帧与发送端发送的数据帧完全相同,数据帧由帧头、数据、CRC和帧尾组成。32’hbc95b5b5为空闲信号,每一帧数据之间必须有5个以上的空闲信号。当接收到原语信号R_RDY(32’hbc954a4a) 时 ,信 用 量 计 数credit_cnt_reg减1;当发送端每发送一帧数据,信用量计数credit_cnt_reg加1。通过上板调试表明数据收发系统功能正确,没有出现丢帧或错误的现象,串行时钟频率达到1.062 5 Gb/s。

5 结束语

文中设计并实现了基于光纤通道数据收发系统,完成了FC-AE-1553协议的FC-0、FC-1和部分FC-2层的功能,通过使用RocketIO使数据串行传输速率达到1.062 5 Gb/s,实现点对点传输。与传统1553B总线协议1 Mb的传输速率[19]相比较,在速度上有质的提高。

[1]杨现萍,段亚.FC-AE-1553总线数据处理技术研究[J].现代电子技术,2011,34(12):29-32.

[2]凤雷,冯收,乔家庆,等.FC-AE-1553设备光纤接口电路的设计与实现[J].电子测量技术,2012,35(7):62-65.

[3]田泽,徐文龙,许恒,等.FC光纤通道技术研究综述[J].电子技术应用,2016(9):143-146.

[4]许里,冯国仕,李璞.光纤通道接口通用驱动程序设计与实现[J].通信技术,2014,47(11):1343-1346.

[5]王树占,李娟艳,王佳敏.光纤通信技术的现状及发展趋势[J].电子制作,2015(8):149.

图6 数据收发系统发送与接收数据对比图

[6]曹素芝,张善从.光纤通道与MIL-STD-1553协议的兼容性设计[J].计算机测量与设制,2010,18(7):1624-1626.

[7]张志,翟正军.航空电子光纤通道协议分析与接口卡设计[J].测控技术,2010(2):99-101.

[8]FCIA Editor.GEN 6-Sixth Generation Fibre Channel[S].2014.

[9]ANSI INCITS.Fibre Channel-Physical and Signal Interface(FC-PH)REV4[S].1994.

[10]ANSI INCITS.Fibre Channel-Avionics Enviroment(FC-AE)REV2.4[S],2002.

[11]ANSI INCITS.Fibre Channel-Avionics Enviroment(FC-AE)REV2.6[S],2002.

[12]黄浩益,熊华刚.GJB 6410.1-2008.中华人民共和国军用标准[S].

[13]Virtex-4 RocketIO Multi-Gigabit Transceiver User Guide[M].2008.

[14]杜瑞,张伟功,邓哲,等.新型总线中并行CRC算法的设计与实现[J].计算机工程与设计,2013,34(1):131-135.

[15]冷悦.FC-AE-1553协议的硬件系统设计[D].成都:电子科技大学,2010.

[16]宣亮亮.基于PC机和FPGA的光纤通道接口适配器的研究与实现[D].南昌:南昌航空大学,2010.

[17]凤雷,冯收,乔家庆,等.FC-AE-1553设备光纤接口电路的设计与实现[J].电子测量技术,2012,35(7):62-65.

[18]苏秀妮.基于RocketIO高速串行通信接口的研究与实现[D].西安:西安电子科技大学,2013.

[19]徐贵贤.1553B总线简介及其实现[J].通信技术,2011,44(5):166-168.