一种应用于10 MHz 8位SAR ADC的分段式DAC电路设计

2018-03-29徐韦佳田俊杰李延标许凤慧

徐韦佳,田俊杰,李延标,许凤慧

(1. 中国人民解放军陆军工程大学 理学院,江苏 南京 211101; 2. 中国人民解放军陆军工程大学 通信工程学院,江苏 南京 211101)

0 引言

随着近代集成电路技术的发展,数字通信得到广泛应用,模数转换器(ADC)作为实现模拟信号向数字信号转换的桥梁,得到了快速长足的发展。在诸多不同结构的ADC类型中,逐次逼近型ADC(SAR ADC)具有精度高、尺寸小、功耗低、成本低的特点,广泛应用在图像采集、工业控制、消费电子、信号采集等场合。而数模转换器(DAC)作为高性能SAR ADC的核心器件,其性能对SAR ADC起着至关重要的作用[1]。

当前对DAC的研究主要包括电压按比例缩放DAC、电流按比例缩放DAC、电荷按比例缩放DAC。在SAR ADC中,电压按比例缩放DAC应用最早,由于采用等值电阻串联分压,因此分压精度较高,缺点是输出电容比较大[2]。电流按比例缩放DAC不受寄生电容的影响,所以转换速度快[3],缺点在于电阻值呈指数递增,所需电阻值范围大,造成DAC面积大和电阻失配误差大,从而降低DAC的精度,同时具有非单调性[4]。电荷按比例缩放DAC是当前运用最广泛的DAC结构,兼有采样保持功能和高精度的特点[5],当DAC的位数比较高时,由于电容阵列呈现二进制指数关系递增,电容的取值范围很广,增加了电容的失配,降低了精度的同时还增加了芯片面积,并且由于大电容的充放电时间比较长,很大程度上影响了电路的转换速度[6]。因此,本文在传统电荷按比例缩放DAC结构的基础上,提出一种分段式结构的DAC电路,增加缩放电容CS,工作在10 MHz采样时钟频率下,具有面积小、功耗低的特点,可以实现8位SAR ADC的模数转换。

1 DAC结构的选取

电压按比例缩放DAC具有良好的单调性,但是对于一个8位的DAC,就需要256个电阻和512个开关,造成电路面积非常大。如果采用开关树结构的电压按比例缩放DAC,会造成非线性开关数目更多,从而降低精度[7]。如果采用电流按比例缩放DAC,虽然速度快,但是失配大,不适用于高精度的系统[8]。如果采用R-2R电流按比例缩放DAC,可以满足精度要求,但是速度有限[7],不符合速度要求。由上述分析可知,目前使用范围最广的电荷按比例缩放DAC是最为合适的选择,不但兼有采样保持电路功能,并且功耗很低,精度高,高位具有单调性,所以在8位SAR ADC中决定采用电荷按比例缩放DAC。

然而,电荷按比例缩放DAC虽然具有功耗低、精度高等优点,但是随着ADC位数的增加,二进制权电容阵列中的电容值也成指数倍增加,增大了面积,并且在当前CMOS工艺条件下,大电容失配率较高,从而造成精度降低的问题。

针对这个问题主要有两种解决方法,一种是采用电阻-电容型DAC(即RC-DAC),另一种是分段式电容阵列。前者高位由二进制加权电容阵列所组成,低位由多个相等的分压电阻串形成,多用于分辨率较高(一般大于10位)的ADC中,由于高位采用了一部分电容阵列,因此匹配精度比电阻要高,并且高位有较小的电容失配误差,而低位的电阻串DAC具有很好的单调性,能够减小系统的线性误差[2]。本文设计的8位SAR ADC,DAC精度不算很高,所以引入缩放电容CS,使用分段式DAC结构来满足要求。

2 DAC具体电路设计

2.1 传统电荷按比例缩放DAC

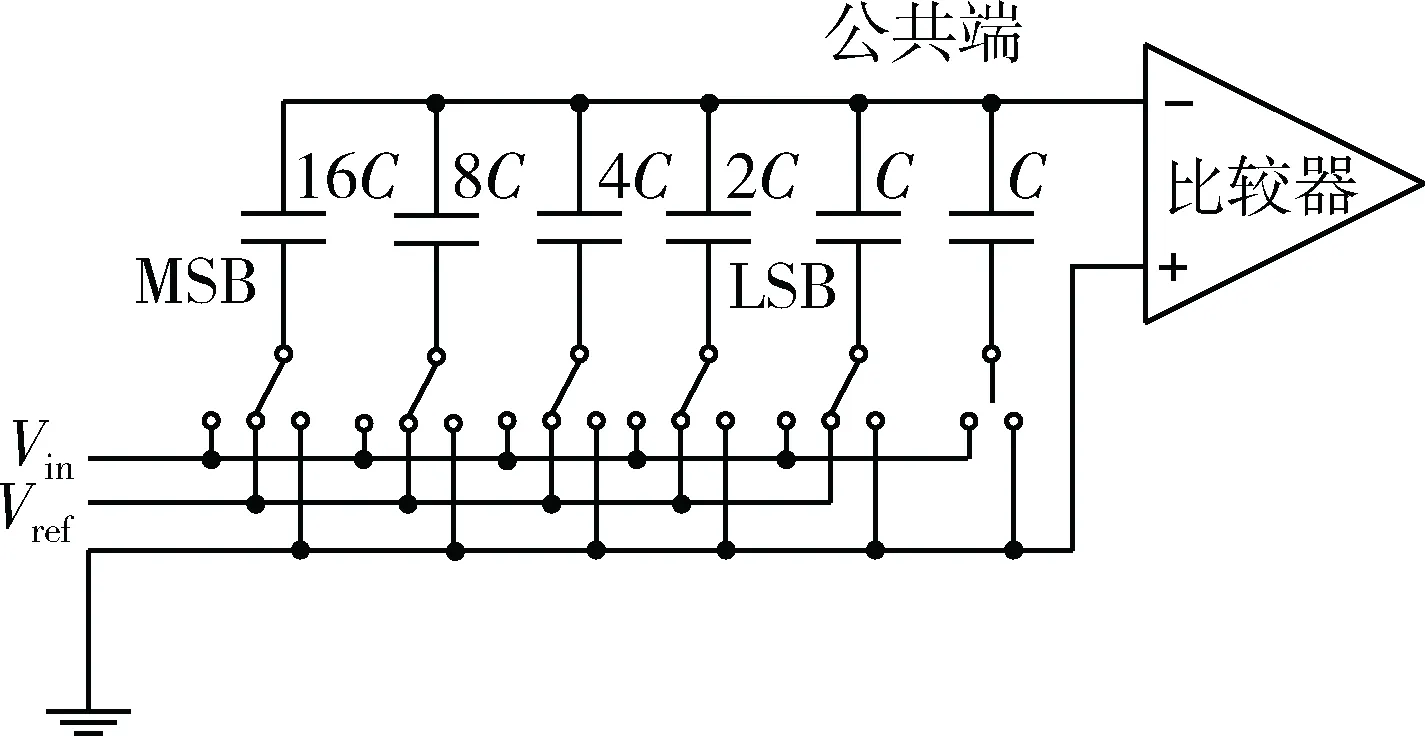

电荷按比例缩放DAC是当前运用最广的DAC结构,兼有采样保持功能和精度高的优点,是当前SAR ADC采用的主流结构。图1给出了一个5位的电荷按比例缩放DAC的电路结构示意图。

图1 电荷按比例缩放DAC电路结构示意图

整个SAR ADC采取的是二进制搜索算法[10],具体的转换过程如下。首先,SAR ADC的逻辑控制部分将寄存器输出的最高位MSB设置为1,即10000000,对应的参考电压为基准电压Vref的一半,即为1/2Vref。比较开始,最高位MSB的电容的自由端连接到基准电压Vref,由于整个电容阵列是按2的指数形式并联,这样,驱动公共端电压向正端移动1/2Vref。例如,如果输入Vin=5/8Vref,那么公共端电压被驱动至-5/8Vref+1/2Vref=-1/8Vref<0,之后比较器将该电位与地电位比较,输出逻辑高电平1,说明正在比较的输入信号Vin大于参考电压1/2Vref,所以将比较的该位保持1。如果Vin=3/8Vref,那么公共端电压被驱动至-3/8Vref+1/2Vref=1/8Vref>0,之后比较器将该电位与地电位比较,输出逻辑低电平0,说明正在比较的输入信号Vin小于参考电压1/2Vref,因此将比较的该位清0。MSB位的比较结束以后,如此循环,开始次高位的比较,由比较器输出比较的结果,直到所有的数字位都比较完毕,最后产生8位二进制数字编码输出。

由电荷按比例缩放DAC的工作原理可知,只有电容的充放电过程会产生直流功耗,因此该结构功耗较低,而且CMOS工艺中电容的匹配精度要比电阻更高,因此该结构在SAR ADC中应用也更为广泛。此外,电荷按比例缩放DAC可以同时实现采样保持电路的功能,不需要使用额外的采样保持电路。但当DAC的位数比较高时,由于电容阵列的电容值是二进制指数关系递增,例如对8位的SAR ADC,最小的单位电容大小为C0,最大为28C0=256C0,电容的取值范围很广,增加了电容的失配,降低了精度的同时还增加了芯片面积,并且由于大电容的充放电时间比较长,很大程度上影响了电路的转换速度,这也是该结构的缺点[11-12]。

2.2 加有缩放电容的分段式DAC

图2是本文采用的8位分段式电荷再分配DAC的电路结构示意图。其工作原理与传统电荷再分配DAC相同,改进之处在于采用缩放电容Cs将二进制加权电容阵列分隔成为两个4位的电容阵列,所以原本应该是16C,32C,64C,128C的电容分别减小为C,2C,4C,8C。由图中可得缩放电容Cs满足:

(1)

整理可得缩放电容Cs的大小为:

(2)

图2 8位分段式电荷再分配DAC

分段式电荷再分配的工作原理也与传统电荷再分配DAC相同。采样阶段,公共端接地,开关S8~S0全部接采样输入信号Vin,之后,公共端断开,开关S8~S0全部接地,驱动比较器的反相输入端电压VX=-Vin。保持阶段,最高位MSB开关S8与地断开,接参考电压Vref,驱动X端电压正向移动1/2Vref,变为VX=-Vin+1/2Vref,此时比较器工作,比较正负输入端电压差。如果-Vin+1/2Vref>0,即Vin<1/2Vref,则比较器输出为0,将该位清零,开始下一轮次高位的比较,开关S8改为接地;如果-Vin+1/2Vref<0,即Vin>1/2Vref,比较器输出为1,维持该位为1,开始下一轮次高位的比较,开关S8继续接参考电压Vref。最高位比较结束,如此循环,进行次高位的比较,直到所有位数全部比较完毕,最终可得X点电压为:

(3)

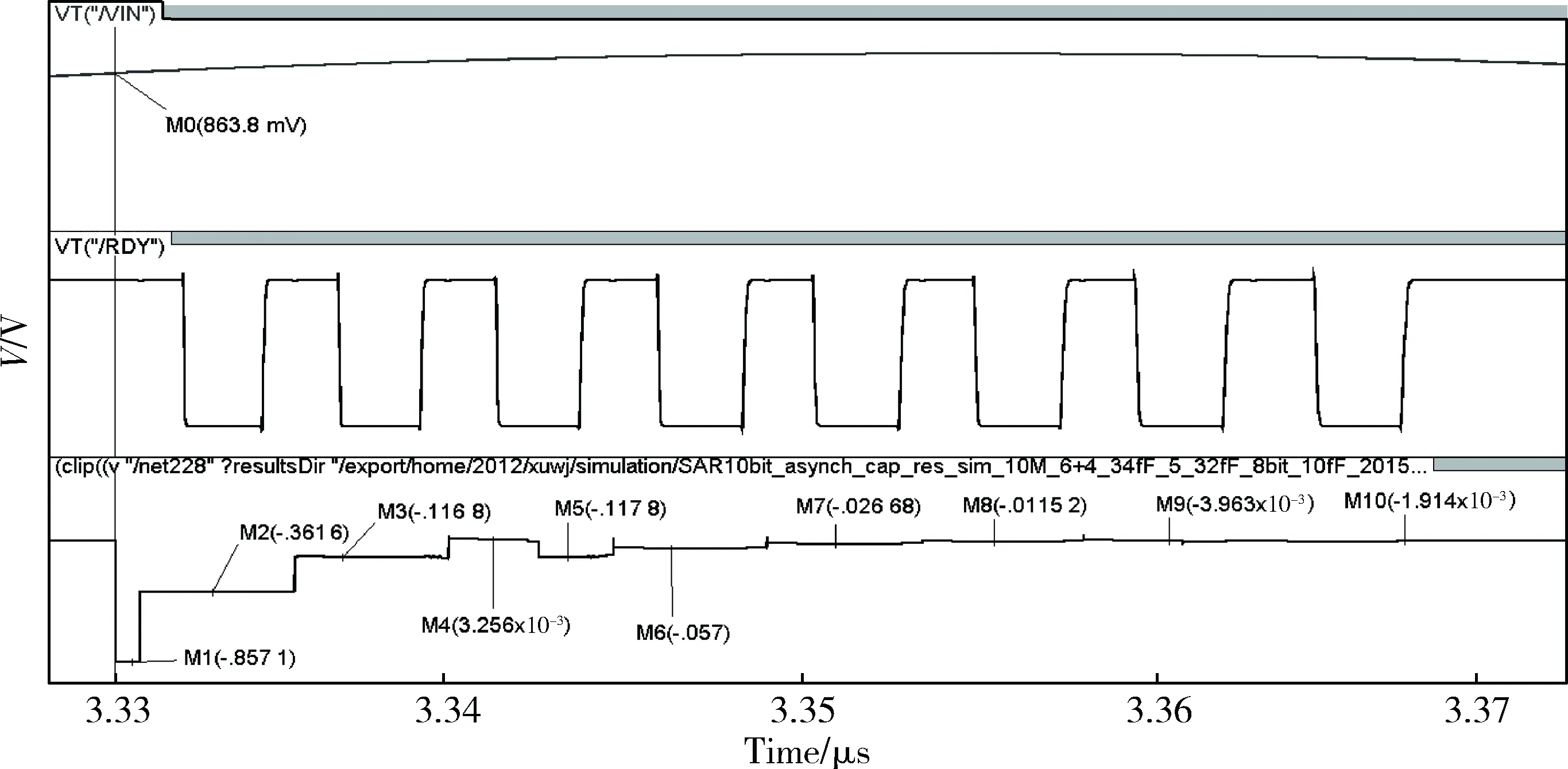

图3 DAC的逐次逼近过程图

其中,S8,…,S1取值0或者1,具体取决于所对应的该位清零还是置1,如果比较结果显示该位清零则取0,置1则取1。S8、S7、S6,…,S1即为整个ADC的转换结果。

分段式结构的优点非常明显,一是有效减小电容取值范围,提高电容阵列的匹配性,从而提高精度;二是总电容减小,电容充放电速度加快,提高了速度,也降低了功耗和面积。所以,分段式结构在精度、速度、功耗、面积方面取得了很好的折衷。

3 仿真与分析

在SMIC 65 nm CMOS工艺下,采用Cadence公司Spectre系列软件,对图2的8位分段式电荷再分配DAC进行仿真,电源电压1.2 V,时钟频率10 MHz。

图3所示是一个转换周期内DAC输出的瞬态仿真结果,显示了DAC逐次逼近过程。从上到下依次为外界输入信号VIN、比较器反馈信号RDY、DAC输出与输入电压VIN的差值曲线。设置输入信号为幅值1 V的正弦信号,基准电压Vref为1 V。RDY是比较器的反馈信号,高电平表示比较器复位,此时比较器的两个正负输出端均为低电平,RDY低电平表示比较器工作,此时比较器输出为高低电平。

观察图3曲线,分析可知,第一个时钟到来之前,输入的采样信号约为863.8 mV,紧接着,DAC被清为零,此时差值电压理论值为VDAC-VIN=-VIN,符合M1点实际电压-857.1 mV。第一个RDY周期内,DAC最高位置1,也就是10000000,差值电压理论值为VDAC-VIN= 1/2Vref-VIN=-359.3 mV<0,近似等于M2点实际电压-361.6 mV,由于VDAC

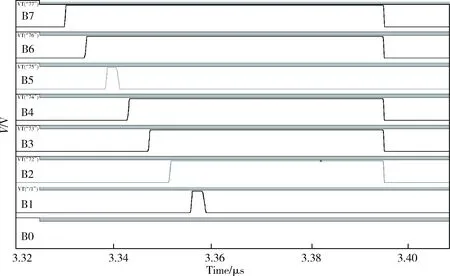

如图4所示,从上到下分别是输出级B7,B6,B5,B4,B3,B2,B1和B0的输出波形,对应采样信号VIN约为863.9 mV时,B7~B0是高位到低位的最后输出端编码11011101,这与理论计算结果相同,图4中转换的最后一位M10点所对应的DAC输出VDAC与输入VIN差值为1.914 mV,控制在0.5LSB以内,所以DAC的整体电路满足设计要求。

4 结论

本文提出了一种应用于8位SAR ADC的分段式电荷按比例缩放DAC电路,工作于10 MHz采样时钟频率,1.2 V电源电压,采用SMIC 65 nm工艺设计实现。采用缩放电容CS,有效减小了电容取值范围,提高了电容阵列的匹配性,有效提高了精度,并且总电容减小,电容充放电速度加快,提高了速度,降低了功耗,减小了面积和成本。仿真结果表明,该分段式DAC可以有效实现8位的数模转换,已成功应用于SMIC 65 nm工艺、时钟频率10 MHz的8位SAR ADC设计中。

图4 输入VIN对应的数字编码输出波形图

[1] ALLEN P E, HOLBERG D R. COMS analog circuit design, Second Edition[M]. 北京: 电子工业出版社, 2002.

[2] 章大伟. 一种 SAR ADC 的设计与研究[D]. 合肥: 合肥工业大学, 2014.

[3] WU J, LI F, ZHANG C, et al. An asynchronous SAR ADC with gate-controlled ring oscillator for multi-phase clock generator[C].Solid-State and Integrated Circuit Technology (ICSICT), 2014: 1-3.

[4] 杨秀丽. 基于 CMOS 工艺的 10 位 SAR ADC 的研究与设计[D]. 合肥: 合肥工业大学, 2007.

[5] 郝乐. 基于低电压高精度12-bit SARADC 设计[D]. 北京: 北京交通大学, 2008.

[6] Han Xue, Qi Wei, Yang Huazhong, et al. A single channel 6-bit 230-MS/s asynchronous SAR ADC based on 2 bits/stage[J]. Journal of Semiconductors, 2014, 35(7): 075005.

[7] 郑烷.12 位逐次逼近型A/D转换器的设计[D]. 武汉: 华中科技大学, 2007.

[8] 毛泽龙.10位逐次逼近型ADC芯片设计[D]. 武汉: 湖北大学, 2008.

[9] TANG H, SUN Z C, CHEW K W R, et al. A 5.8 nW 9.1-ENOB 1-kS/s local asynchronous successive approximation register ADC for implantable medical device[J]. Very Large Scale Integration (VLSI) Systems, 2014, 22(10): 2220-2224.

[10] Wu Huanling, Meng Qiao, Zhi Hao. A novel 10bit 90MS/s 2b/cycle SAR ADC[C]//Advanced Technologies for Communications (ATC), 2013: 521-524.

[11] 王俊博. 基于 CMOS 工艺 10 位模数转换电路的设计[D]. 哈尔滨: 黑龙江大学, 2010.

[12] 何全. 一种 12 位 CMOS SAR ADC的研究[D]. 天津: 南开大学, 2011.