基于EP3C40的FPGA最小系统设计和实现

2018-03-16鲁睿其

鲁睿其

基于EP3C40的FPGA最小系统设计和实现

鲁睿其

(湖南理工学院信息与通信工程学院,湖南 岳阳 414006)

本文介绍了基于Altera公司Cyclone III系列的EP3C40 FPGA最小系统的设计和验证过程,详细介绍了高速FPGA电路设计、PCB电路板设计和数字系统集成设计等相关设计.FPGA最小系统硬件设计包括时钟、电源、存储器、接口、配置、以及USB Blaster等部分,最小系统的功能验证包括键盘和LCD控制、总控制、DDS模块等。最终测试结果表明,本系统工作正常,DDS时钟频率可以达130MHz.

现场可编程门阵列 可编程片上系统 直接数字合成

0 引言

随着可编程逻辑器件集成的规模越来越大,出现了可编程片上系统(SOPC),把处理器、外围的逻辑控制电路集成在一块可编程逻辑器件上,大大的减少了系统芯片的数量、缩小了系统的体积,提高了系统的可靠性[1,2]。由于可编程器件有着巨大的优点,可编程逻辑器件得到了广泛应用,掌握可编程逻辑器件技术是一个电子工程技术人员的基本要求。

1 最小系统硬件实现

1.1技术指标

本文设计的FPGA最小系统要求FPGA最小系统的功能,要求如下:根据设计需要划分好模块;编写好键盘和液晶控制的程序,实现人机接口;DDS的频率输出通过键盘控制,并由液晶显示相关的参数;DDS的工作频率要大于100 MHz,输出的信号能驱动高速D/A;开发中使用FPGA内部嵌入的RAM、PLL等资源。

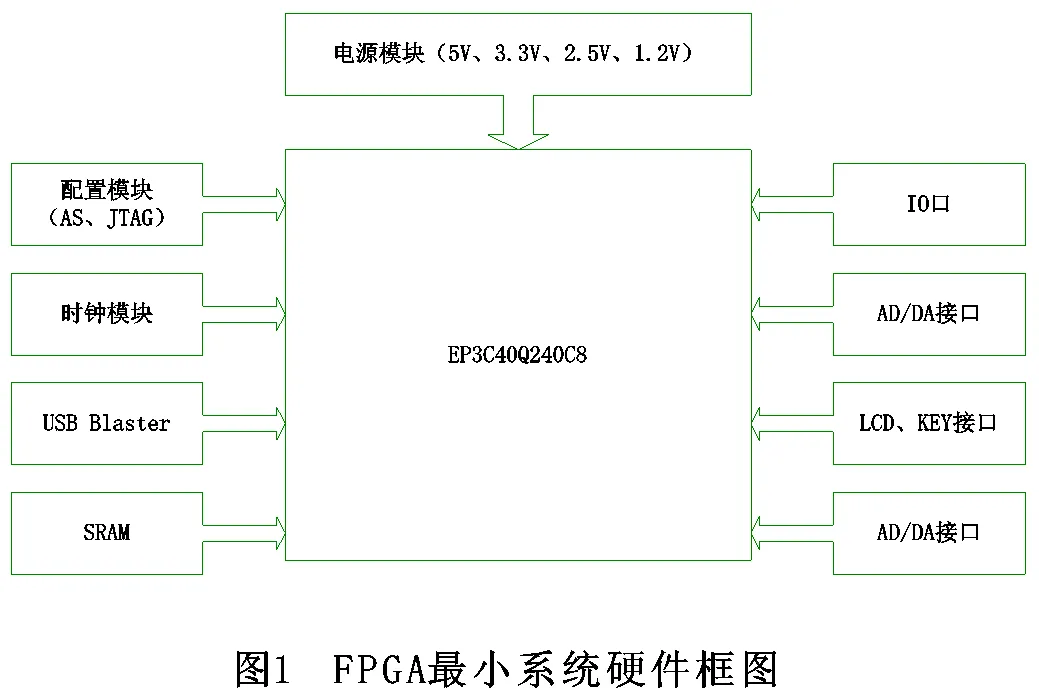

1.2系统原理框图

FPGA最小系统的硬件框图如图1所示。系统包含FPGA工作最基本的单元电路:电源、时钟、配置、存储器、USB Blaster等模块。另外,考虑到系统扩展的灵活,系统留有外部扩展接口。

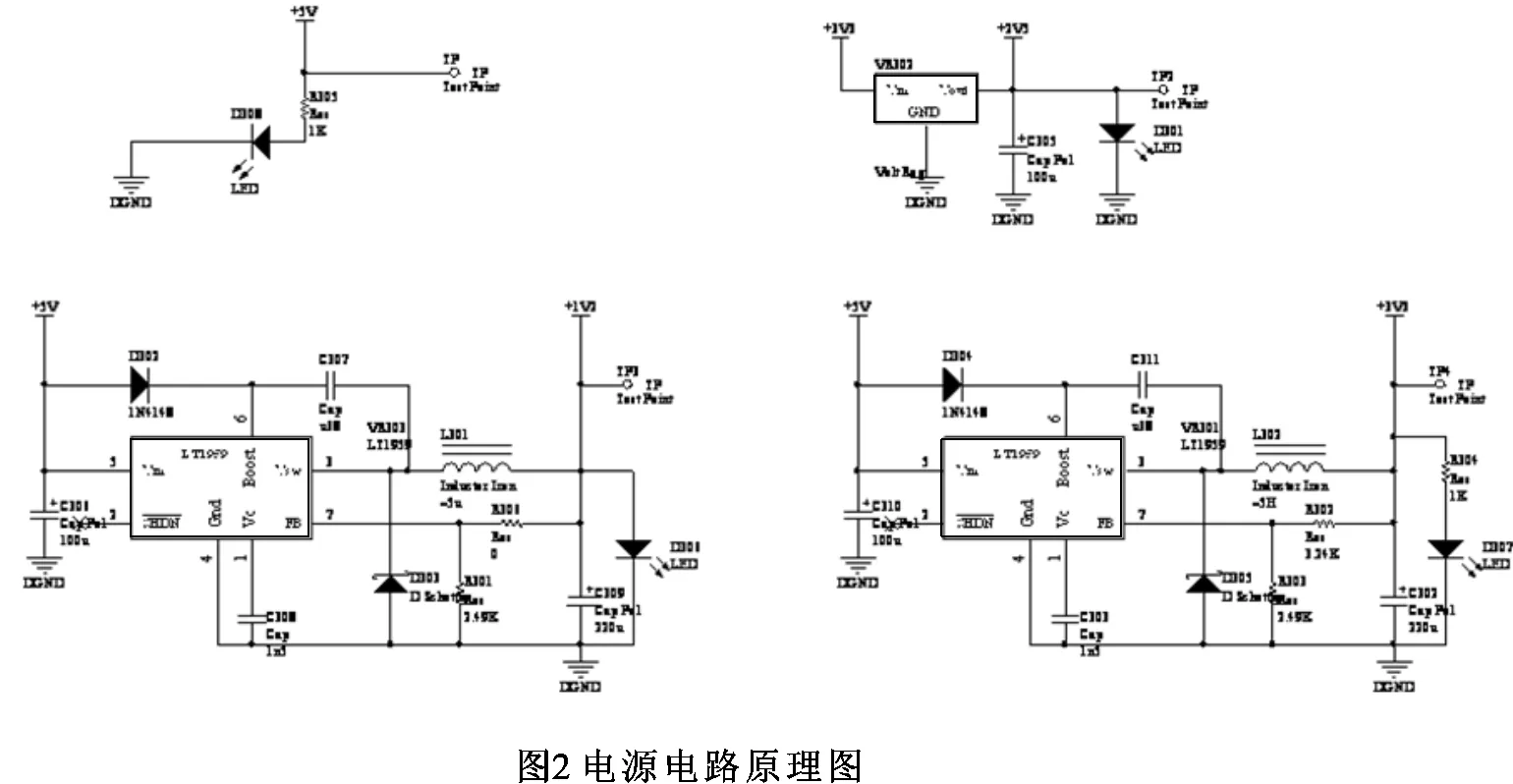

1.3系统电源设计

EP3C40工作需要三个电源,每个接口上需要一个5 V电源以支持外围扩展电路的工作,电路原理图如图2所示。根据Altera公司提供的datasheet以及功耗估算工具,本设计选用Linear公司的开关型稳压器LT1959,它的拓扑结构为电流模式,以获得快速瞬态响应及良好的环路稳定性。

1.4时钟电路设计

为充分利用EP3C40的时钟资源,本设计采用四时钟源方案,其中三个由晶振提供,SMA外部输入时钟,这样使最小系统拥有了良好的时钟扩展性能。时钟部分的具体电路原理图如图3所示,有源晶振的电源提供通过电感与VIO隔离,大大降低振荡器件对电源的高频干扰;另外一路由外部SMA输入接口CLK3。每路时钟输出通过外加电阻消除高速数字时钟的回流效应,以保持良好的信号完整性。

图3 时钟部分原理图

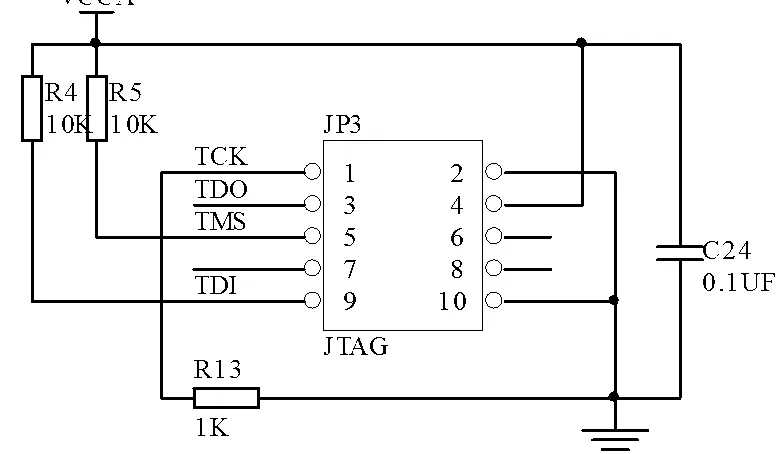

1.5JTAG电路设计

FPGA最小系统与工程开发的产品不同,它具有良好的调试特性。为此,本最小系统设置了JTAG接口,JTAG接口可以配置和调试FPGA。Quartus II自带有信号分析的工具SignalTap II,它支持在线调试功能。具体实现是通过在开发工具中设定相关测试信号,再与原来的文件综合、下载、运行,之后,在工具中可以看到设计中有关信号的波形。因此,JTAG接口为系统调试提供了极大的便利。该部分电路原理图如图4所示。

图4 JTAG接口原理图

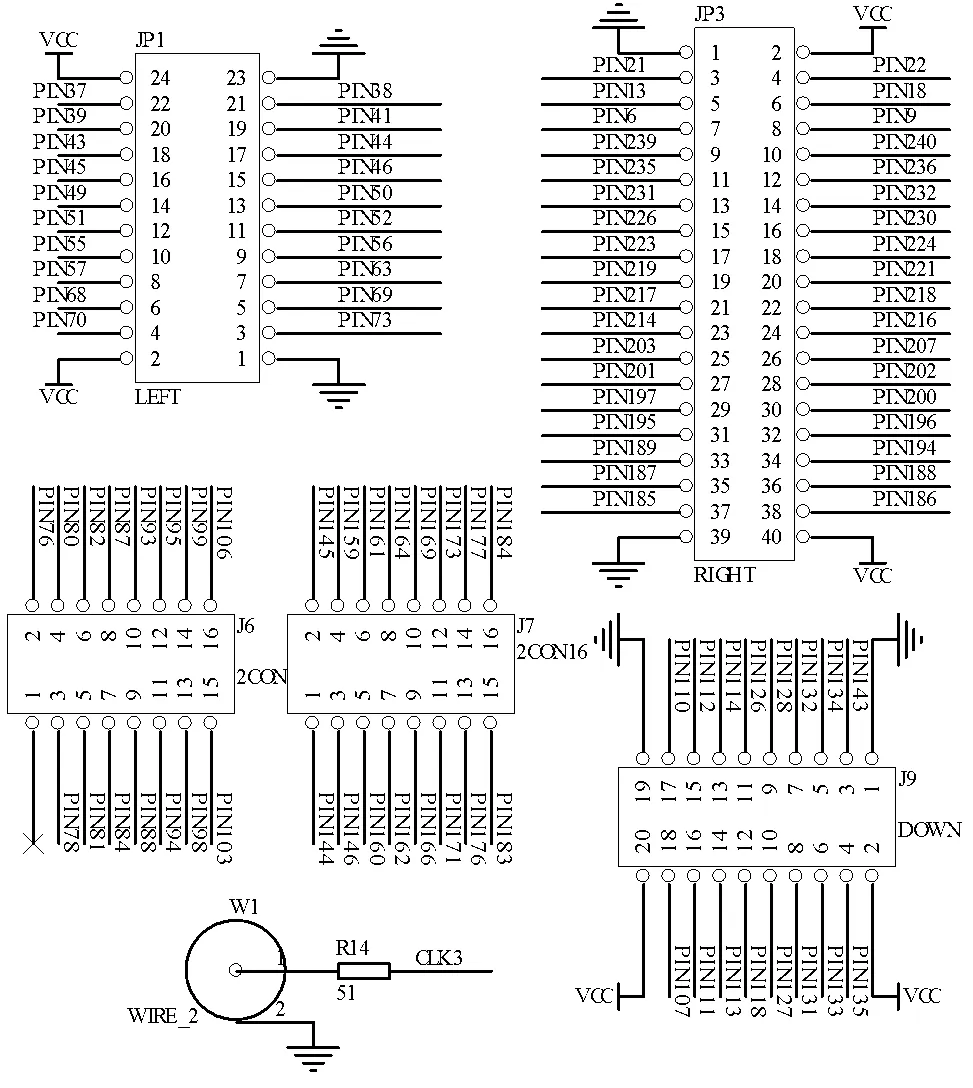

1.6接口电路设计

FPGA最小系统必须具有良好的可扩展性,能方便地与外部电路接口。可以选择设计成HSMC(高速Mezzanine卡接口)接口。HSMC接口是Altera自己定义的一种高速Mezzanine接口,该接口定义有Transceiver 、LVDS以及普通IO。考虑到本系统不需要跑上GHz频率,所以接口部分采用40针插座GPIO方式引出,另外一路时钟信号通过FPGA的专用时钟输出引脚以SMA接口输出。该引脚可以被设置为FPGA内部全局网络直接输出,因此经该引脚输出的时钟信号具有较好的信号完整性,同时外部SMA接口线良好的屏蔽效果可以避免电磁干扰。考虑到外部电路的电源供应,每个40针的接口配上+5V的电源,为FPGA最小系统的外扩电路提供基本的电源供应。接口部分的电路原理图如图5所示。

图5 接口部分的电路原理图

1.7 SRAM存储电路设计

SRAM存储器可以用于存储数据,以及NIOS II的程序存储等等。SRAM存储器优点在于速度快、节能,不必配合内存刷新电路,可提高整体的工作效率。本系统采用ISSI公司的IS61LV25616AL SRAM芯片,256K*16bit的容量,电路原理图如图6所示。

图6 SRAM接口电路

2 FPGA最小系统功能验证

控制功能用RTL级硬件描述语言设计控制状态机,其它逻辑部分也用RTL级硬件描述语言实现。此方法对硬件描述语言和数字系统集成的要求较高,特别是要把握好整体观念,采用自顶向下的设计方法、逐步细分以及完成设计。

2.1内部逻辑图验证框图

内部逻辑验证采用国际上流行的自顶向下的设计方法,先确定总体框图,然后逐步细分,最后综合成一个系统[3]。

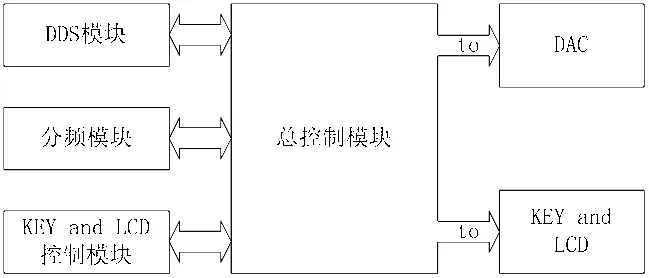

经过认真的考虑和分析,设计的内部总体逻辑框图如图7所示,括号中的英文名为设计模块名。其中,分频模块的作用是产生状态机工作时钟;键盘和液晶控制模块控制键盘和液晶;DDS模块产生数字合成信号;总控制模块协调各模块之间的工作。

图7 内部逻辑验证框图

2.2分频器设计

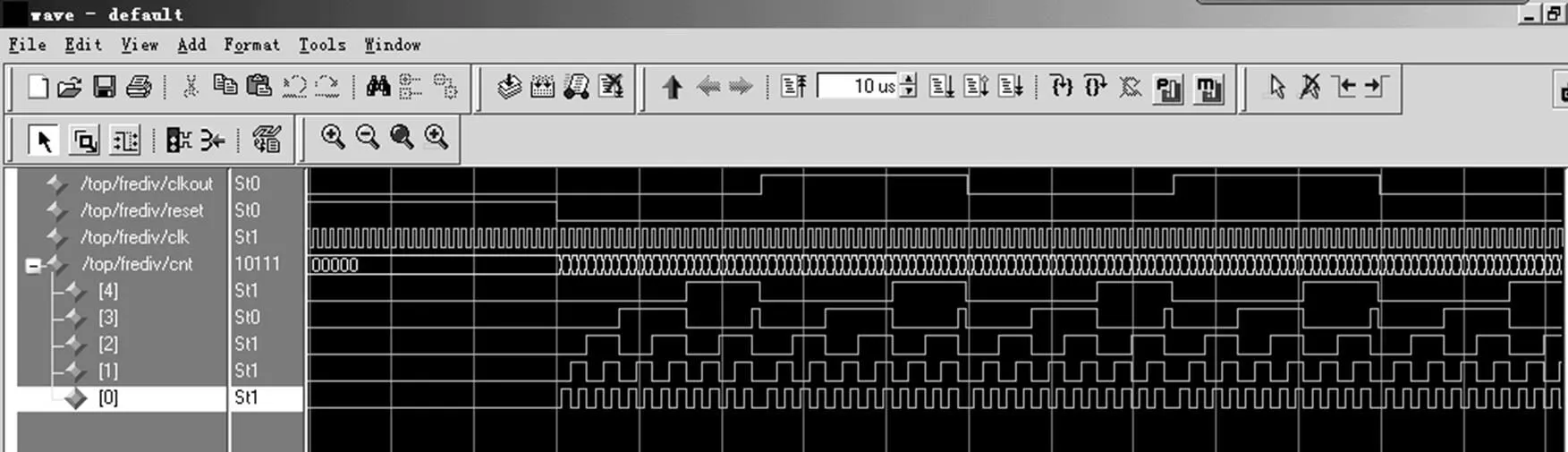

分频器的设计相对简单,50 MHz的时钟输入,经过50分频后输出1 MHz的状态机工作时钟。用Modelsim对分频模块仿真的波形如图8所示。计数器cnt在时钟沿的激励下从0开始不断增加,最大值24。所以每25个输入时钟周期使得输出时钟反相一次,输出时钟的频率为输入时钟的1/50。在输入50 MHz的频率下,输出频率为1 MHz。

2.3DDS模块设计

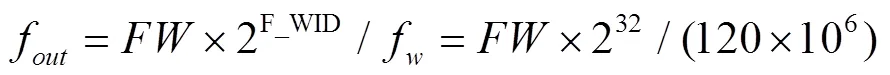

DDS模块包括相位累加器、正弦查找表和PLL(锁相环)。相位累加器在时钟沿的激励下不断以输入频率字为单位累加相位;正弦查找表根据相位值查出对应相位的幅度值输出到DA转换器;PLL模块把外部的时钟倍频到120 MHz给DDS提供工作频率。逻辑框图如图9所示。正弦查找表用的ROM和倍频用的PLL均利用Quartus II工具自动生成。根据DDS的工作原理,输出正弦波的频率为[4]:

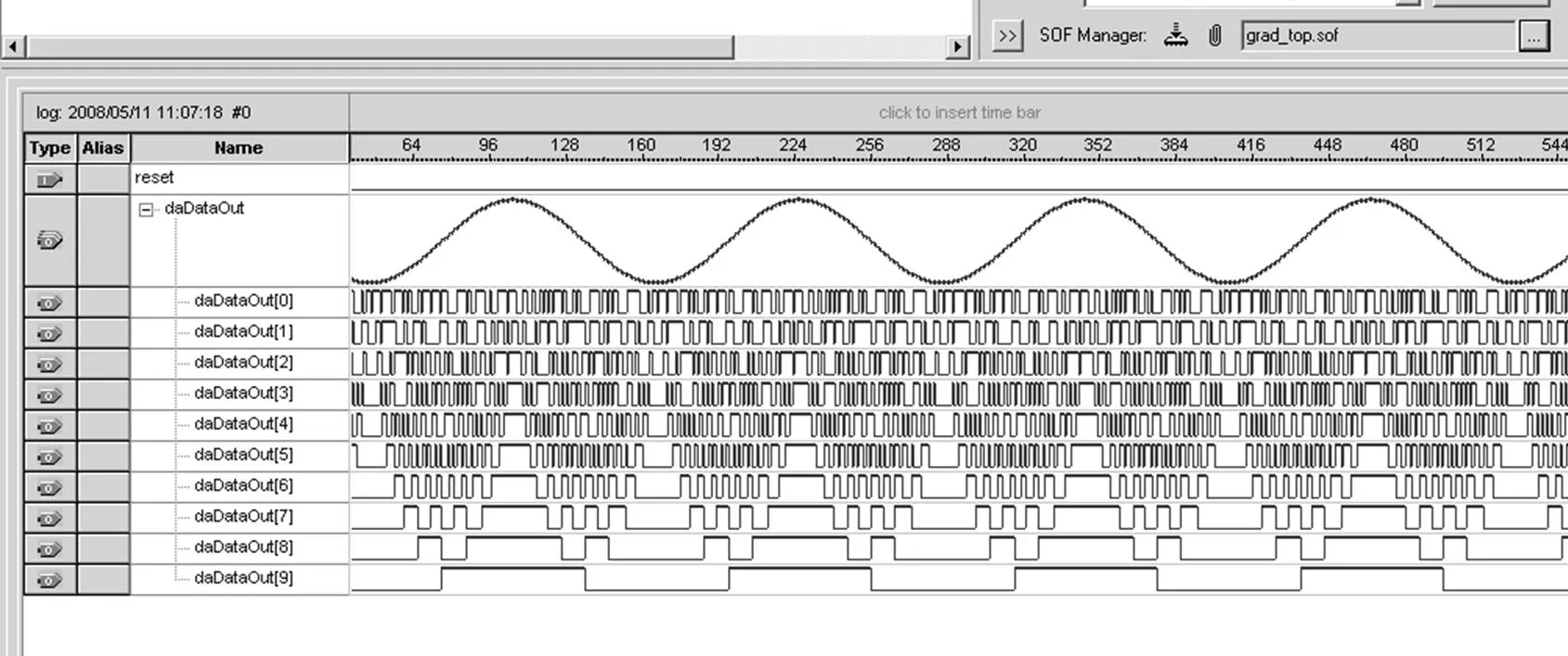

DDS模块由Quartus II软件综合,生成Modelsim需要的仿真文件,编写好激励文件后,在Modelsim中的仿真波形如图11所示。

由仿真结果可以看出,通过改变频率控制字可以实现输出频率的调节,达到了设计要求。

图8分频器时序仿真图

2.4键盘和液晶控制程序设计

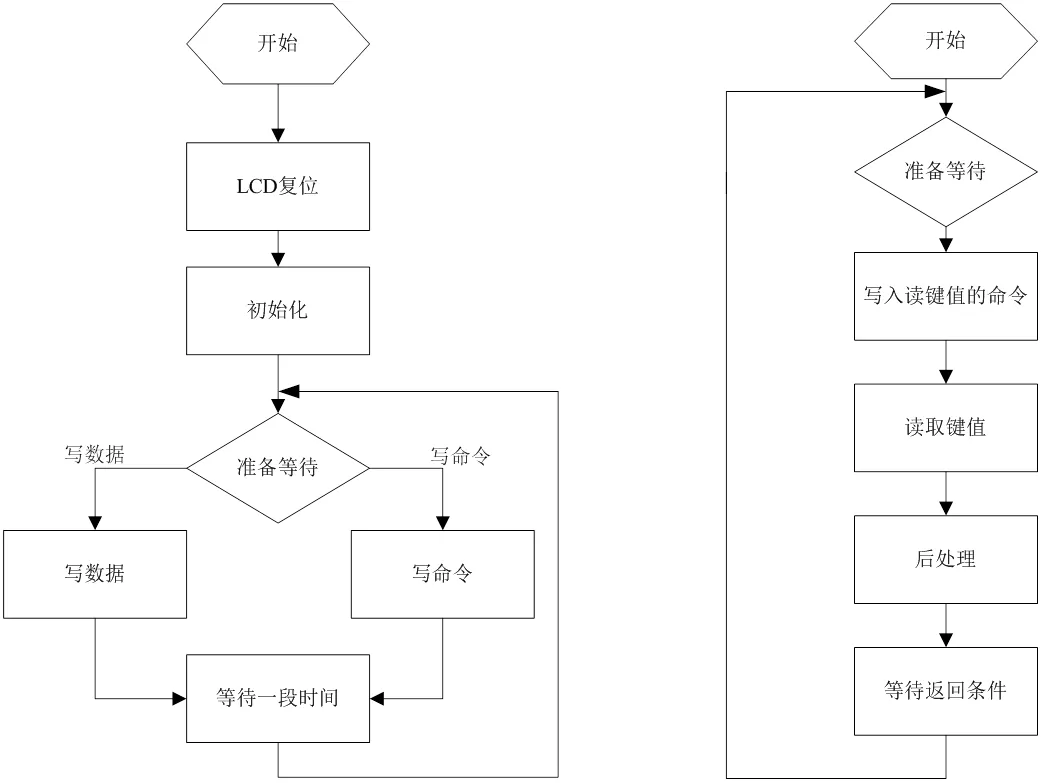

本最小系统中键盘控制采用专用芯片HD7279,液晶采用核心控制器为ST7920的12864LCD模块。本设计采用两个状态机分别对键盘和液晶模块进行控制,程序流程图如图11所示。控制键盘的时候要注意连续按键的处理,否则在状态机的工作频率下,就是稍稍按一下键也会得到很多个一样的键值,所以需要设定一个计数器,当计数到一定时间再返回到等待的状态,这样这个计数器计数的多少决定了等待时间的长短。本程序中,设定的这个计数值为250000,在1 MHz的状态机工作频率下等待时间为0.25 s,实际的等待时间还受其它模块的影响,会稍微大于这个值。另外的一种方法是用锁存器的方法实现,这样可以占用小的资源。由于本设计中的FPGA资源够用,所以采用计数器的方法实现。

3 实验结果分析及分析

顶层文件的作用是把各子模块连接到一起,形成一个最终的系统模块。采用Verilog HDL描述语言描述的顶层文件的输入输出只保留了FPGA与外部通信的接口。如图12所示,图中的连线显示了各子模块的连接关系,四个模块是上文中的四个模块。顶层文件的外部接口有键盘接口、LCD接口、D/A接口、输入时钟、复位等。顶层文件确定无误后,在Quartus II开发平台中加入在线信号分析的相关设置,然后综合,对整个系统的重要信号进行在线分析,结果如图13所示,达到了设计要求。本最小系统与外扩的D/A和键盘显示电路进行了联调和测试,使用的D/A转换器是TI公司的DAC5674,该D/A转换器精度为10位、速度可达125 MHz。调试成功后测出输出频率为1 kHz、10 MHz的正弦波形如图13所示。

图10 键盘和液晶控制模块程序流程图

4 结束语

本文以Altera公司的FPGA芯片EP3C40Q240C8为核心设计了FPGA最小系统板,并完成了实物的制作与相应的软硬件调试。完成了FPGA最小系统的硬件设计与制作。设计的FPGA最小系统具有体积小、使用方便、扩展性好等优点。把FPGA的JTAG与AS下载方式组合到一个系统中,并制作了Altera公司的USB Blaster下载线,方便程序下载和调试。验证程序采用了国际上流行的设计方法和开发软件,Quartus II和Modelsim配合使用,很接近工程应用的实际,为以后的工作打下了坚实的基础。充分的利用了FPGA内部的资源,使用了FPGA内部嵌入的ROM和PLL,综合后的系统也使用了嵌入的乘法器。使用Verilog HDL硬件描述语言描述实现了液晶控制、键盘控制和DDS功能,并把这些功能集成到一个数字系统中。DDS工作的频率达到130 MHz,证明本最小系统完全也可以用于其它的高速数字系统中。

图11 DDS模块仿真波形

图12 顶层文件在线信号分析结果

[1] 张庆玲. FPGA原理与实践[M]. 北京航天航空大学出版社, 2006.

[2] 求是科技. CPLD/FPGA 应用开发技术与工程实践[M]. 人民邮电出版社, 2005.

[3] 候伯亨. VHDL硬件描述语言与数字逻辑电路设计[M]. 西安:西安电子科技大学出版社, 1999.

[4] 陈智萍.基于CPLD的单片机结构设计研究[D]. 燕山大学硕士学位论文, 2003:4-5.

Design and Implementation of FPGA Minimum System Based on EP3C40

Lu Ruiqi

(Department of Information and Communication Engineering, Hunan Institute of Science and Technology, Yueyang 414006, Hunan, China)

TN741

A

1003-4862(2018)01-0048-05

2017-11-15

鲁睿其(1988-),女,硕士。研究方向:可编程逻辑器件技术。