基于FPGA的DDR3 SDRAM控制器设计与实现方法

2018-03-09丁培培通讯作者

丁培培(通讯作者),郑 列,李 宏

(西安石油大学<电子工程学院> 陕西 西安 710065)

1 引言

随着现代科技的高速发展,在雷达、无线通信、图像处理等领域需要高速传输大量的数据,高速数据采集作为系统中比较关键的部分,对数据处理的速度、稳定性、实时性以及功耗提出了更高的要求[1]。

从现有的存储器来看,当DDR2内核的工作频率达到200MHz时,数据传输速率将提高到极限值800MHz[2]且不会再有显著提升。由此可见,一般的存储器已不能满足目前高速度、高宽带、大容量的数据存储和访问,并制约存储器的发展和应用。DDR3作为一种双倍数据速率的同步动态随机存储器,相比DDR2的不足,DDR3具有高带宽、高可靠性、低功耗和低成本的特点,因此成为高速数据采集系统的首选方案[3]。

Xilinx公司推出新一代低成本Kintex-7系列FPGA与Virtex-6系列FPGA相比[4],其功耗和成本都降低了50%,而性价比却提高了2倍。并且Kintex-7 FPGA可提供高密度逻辑、高性能收发器、存储器、DSP以及灵活混合信号,通过这些功能可以提高数据采集速度、优化图像质量。因此,在介绍DDR3的工作原理的基础上,结合Kintex-7自带的IP核,采用Verilog HDL描述语言来设计一种DDR3控制器接口的设计方案,并在Kintex-7系列FPGA平台上实现。

2 DDR3 SDRAM的技术特点和关键操作

本文选择Micron公司提供的型号为MT8JFT12864AZ-1G4G1的DDR3作为研究对象,与镁光公司其它型号DDR3相比,该型号DDR3具有数据传输速率快、内存时钟响应时间短的特点。单颗DDR3中,有14根行(Row)地址线,10根列(Column)地址线,8个Bank,而IO Buffer的对外通信则需要8组数位线(DQ0-DQ7)才能完成,故此单颗DDR3芯片的容量为2的14次方乘2的10次方乘8乘8,结果为1Gbit,因为1B包含8bit,1GB/8=128MB[2]。所以内存条的容量为1GB时就需要有8颗这样的DDR3内存芯片,每颗芯片含8根数位线(DQ0-DQ7),则总数宽为64bit,这样正好用一个Rank。

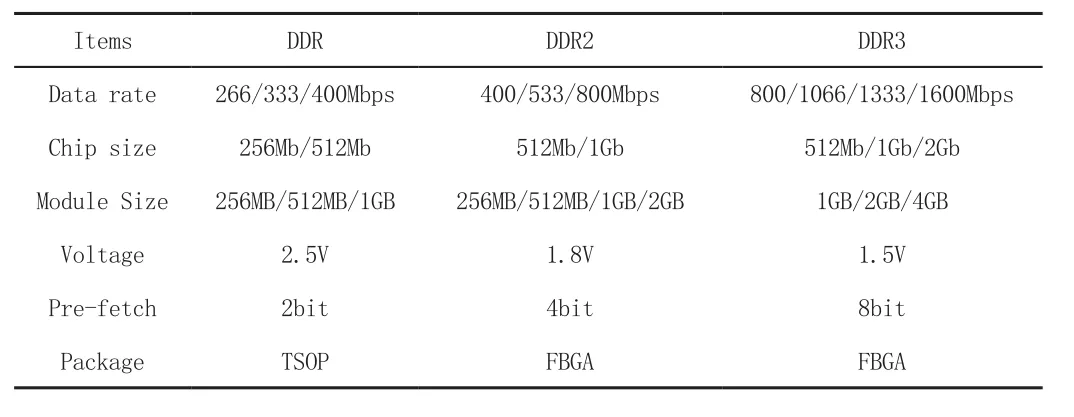

通过查看JEDEC协会所制定的规格,从技术层面来分析DDR3与DDR2的异同点[5]:DDR3拥有高频率低功耗的特点,比DDR2运作时功耗降低30%,1.5V的电压比DDR2的1.8V降低了7%;速度方面DDR3从800Mbps上升到1600Mbps时,速度是DDR2的2倍,数据传输量也是DDR2的2倍。由此可知,新一代存储器DDR3 SDRAM在提高了带宽的同时也大大降低了系统的功耗。表1总结了DDR,DDR2,以及DDR3的一些重要的区别。

表1 DDR3内存的规格比较表

DDR3操作过程主要包括:读命令、写命令、预充电命令、刷新命令与激活命令,DDR3根据接收命令的不同顺序执行相应的操作。上电后,为使DDR3进入正常工作状态,需要初始化操作,并且必须按照预先设定的顺序进行,与此同时,还需要对四种模式寄存器(MRS)进行配置,否则会引起未知错误。初始化后,DDR3进入有效工作状态,通过状态机控制状态跳变,并根据接收的命令执行相应的操作。

3 DDR3 SDRAM系统总体设计

本文中DDR3 SDRAM控制器采用Xilinx MIG IP核来设计,可以大大降低设计人员的开发周期和工作量。用户需要在Xilinx ISE中MIG IP核的GUI图形界面选择DDR3芯片的型号,总线宽度和速度级别,并设置CAS延迟,突发长度,引脚分配等参数,得到包含Verilog HDL代码和UCF 约束文件控制器[6]。选用的FPGA芯片为Kintex-7,型号为XC7K70T,封装为FBG484,速度等级-2。Xilinx Kintex-7系列FPGA的存储器接口解决方案模型如图1所示,用户设计模块通过用户界面直接调用IP内核来控制DDR3 SDRAM的读写。

图1 Xilinx Kintex-7 FPGA内存接口解决方案模型

该方案由用户控制模块,用户接口模块,内存控制模块和物理层接口模块组成[7]。其中,内存控制模块位于用户界面模块和物理层接口模块之间,前端为用户界面模块提供数据传输机制,后端从物理层接口接收并处理请求;物理层模块直接与DDR3进行通信,其功能是捕获由DDR3发送的数据,并通过缓存发送和接收DDR3控制信号,地址信号和数据信号,同时确保命令和地址、数据保持信号同步[8-9]。

4 DDR3 SDRAM控制器接口的仿真

4.1 ISE下FPGA的设计流程

使用Xilinx ISE软件的MIG工具生成基于Verilog HDL的DDR3控制器的IP核代码,然后进行综合优化、综合后仿真、布局布线和时序仿真,其软件实现流程如图2所示。

图2 ISE下FPGA设计流程

4.2 控制器接口的仿真结果分析

利用Verilog HDL完成控制器和物理层中的代码之后,需要对控制器进行功能性仿真验证。在功能仿真时忽略电路中逻辑门的时延,着重验证理想情况下电路的行为和设计思路的一致性[10]。

此次设计采用DDR3内存核心频率是200MHz,总线位宽数是64位,一次预读取8位,根据内存带宽的计算公式:带宽=内存时钟频率×内存总线位数×倍增系数/8[1]。DDR3的内存带宽可以达到12.5GB,传输速率可达到1600MB/s。由于数的传输速率非常快,采用Chipscope很难抓取到由控制器接口写入到DDR3中的数据,因此采用动态时序分析的方法来观测写入与读出的数据是否正确。

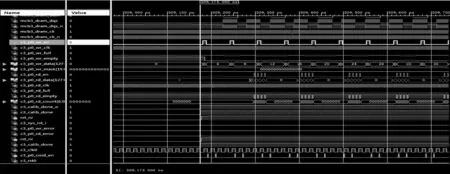

其中,仿真工具使用Xilinx ISE 14.7编译环境中自带的仿真工具Simulate Behavioral Model,仿真验证结果如图3所示。

图3 动态仿真结果

由图3可知,c3_calib_done信号被设置为1,表示初始化完成,否则为0。只有rst_nr为高电平时,c3_p0_wr_en和c3_p0_rd_en才会有效。对于突发长度BL,将其值设置为8,地址位每增加64,数据端口就会同时写入两个256位数据,可以通过c3_p0_wr_error和c3_p0_rd_error这两个比较信号判断DDR3控制器是否读写正确。从仿真结果看出比较信号c3_p0_wr_error和c3_p0_rd_error始终为低电平,表明从接口传输过来的数据能够准确写入到DDR3内存中,且写入的数据和读取的数据相同,所以该测试模块仿真通过。

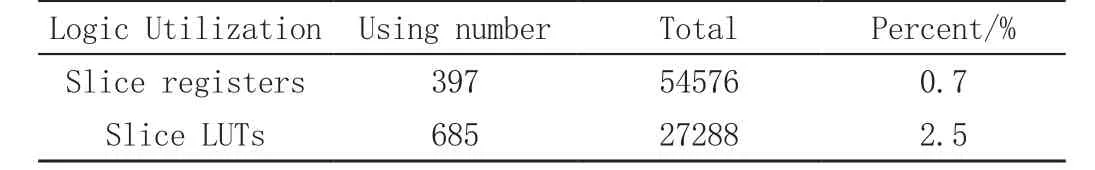

该DDR3控制器已成功应用于遥感图像压缩系统中[11],选用Xilinx公司的Kintex-7系列型号为XC7K325T-2FGG900I的FPGA芯片,用ISE综合图像压缩系统中的DDR3控制模块,其资源占用情况如表2所示,该模块占用很少的片上资源,在存储速度和可移植性方面均能满足要求。

表2 DDR3控制器模块资源利用

5 结语

通过比较分析DDR3 SDRAM的新特性及工作过程,给出基于FPGA的DDR3控制器的设计与实现,并结合软件仿真分析,证明该DDR3控制器能够实现等效频率高达1600MHz的数据读写操作。设计者根据用户需求灵活改变参数设置来对DDR3内存模块进行管理,可以最大限度提高访问内存的速度和带宽。由于DDR3具有存储速度快、高带宽等特点,该DDR3控制器在遥感图像压缩系统中有较好的应用效果,在未来的云计算、服务器和消费类电子上前景也更加广泛。

[1]丁宁,马游春,秦丽,等.基于FPGA的DDR3-SDRAM控制器用户接口设计[J].科学技术与工程,2014,14(17):225-229.

[2]黄万伟.XilinxFPGA应用进阶:通用IP核详解和设计开发[M].电子工业出版社,2014.

[3]刘天祥.基于片上标准总线接口的SDRAM控制器设计与验证[D].西安电子科技大学,2015.

[4]孙俊杰.赛灵思7系列FPGA统一可扩展架构[J].中国电子商情:基础电子,2010(8):30-31.

[5]杨军.基于FPGA的DDR3控制器IP设计与验证[D].南昌航空大学,2015.

[6]焦淑红,程仁涛.基于FPGA的DDR3控制器设计[J].电子科技,2015,28(7):41-43.

[7]宋明,赵英潇,林钱强.基于FPGA的DDR3SDRAM控制器的设计与优化[J].电子科技,2016,29(11):47-50.

[8]夏宇闻.Verilog数字系统设计教程[J].单片机与嵌入式系统应用,2003(6):51-51.

[9]吴进,刘路.同步动态随机存储器的控制器设计与实现[J].西安邮电大学学报,2012,17(5):78-80.

[10]陈芳,黄秋萍.基于多种EDA工具的ASIC设计[J].半导体行业,2006(5):42-46.

[11]陈占良,金龙旭,陶宏江,等.高速图像压缩系统中DDR3控制器的实现[J].电光与控制,2016(8):85-88.