用FPGA和改进的LMS算法实现自适应滤波器

2018-03-01,,,

,,,

(兰州大学 信息科学与工程学院,兰州 730000)

引 言

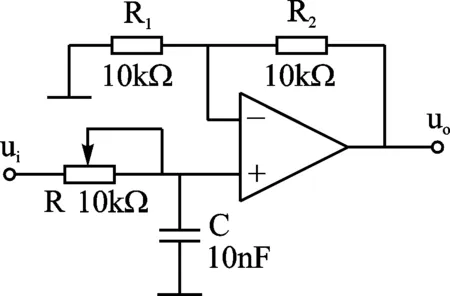

本文需要设计并制作一个自适应滤波器,用来滤除特定的干扰信号。自适应滤波器工作频率为 10~100 kHz。系统主要由电源模块、加法器模块、移相器模块和自适应滤波器模块4部分组成。

1 方案分析

1.1 移相器模块的比较与选择

采用RC阻容网络一般是将RC运算放大器(以下简称运放)联系起来组成有源的移相电路。优点是电路调节方便,细节清晰,可以实现相位连续可调。

1.2 自适应算法的论证与选择

自适应算法主要有两类思路,分别是递推最小二乘法(Recursive Least Square,RLS)和最小均方算法(Least mean square,LMS),近几年也有许多基于这两类算法的优化方法被提出。

方案一:RLS算法

RLS算法是基于最小二乘准则的精确方法,它的收敛速度快,稳定性强, 因此常被应用于实时系统识别和快速启动的信道均衡,但其算法复杂度较高,算法结构较为复杂。

方案二:LMS算法

LMS算法优点是结构简单,算法复杂度低,易于实现,稳定性好,便于硬件实现。当今,在FPGA上的实现算法已经趋于成熟,而且修改方便灵活,同时具备良好的性能。

综合考虑以上两种方案,本文选择方案二。

2 系统理论分析与计算

2.1 LMS滤波算法简介

自适应滤波器在时刻n的向量如下:

抽头权向量:

W(n)=[b0(n),b1(n),…,bM-1(n)]T

参考输入向量:

X(n)=[x(n),x(n-1),…,x(n-M+1)]T

LMS算法可以用下面一组递推公式来表示,即

y(n)=WH(n)X(n)

e(n)=d(n)-y(n)

W(n+1)=W(n)+2μX(n)e(n)

y(n)是输出信号,d(n)是期望输出值,e(n)是误差信号,也是系统输出值,μ是权矢量更新时的步长因子,μ值越大,则算法收敛越快。由维纳-霍夫方程可知,最小均方误差为:

通过梯度下降法:

Wj+1=Wj+2μejXj

算法步骤如下:

① 迭代计算:n=1,2,3,…;

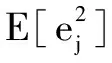

图4 移相器电路图

② 滤波输出:y(n)=WT(n)X(n);

③ 误差估计:e(n)=d(n)-y(n);

④ 权向量自适应:W(n+1)=W(n)+2μe*(n)X(n)。

其中μ是用来控制稳定性和收敛速度的步长参数,μ(μ<1)为2的整数次幂分之一。

2.2 移相器的分析

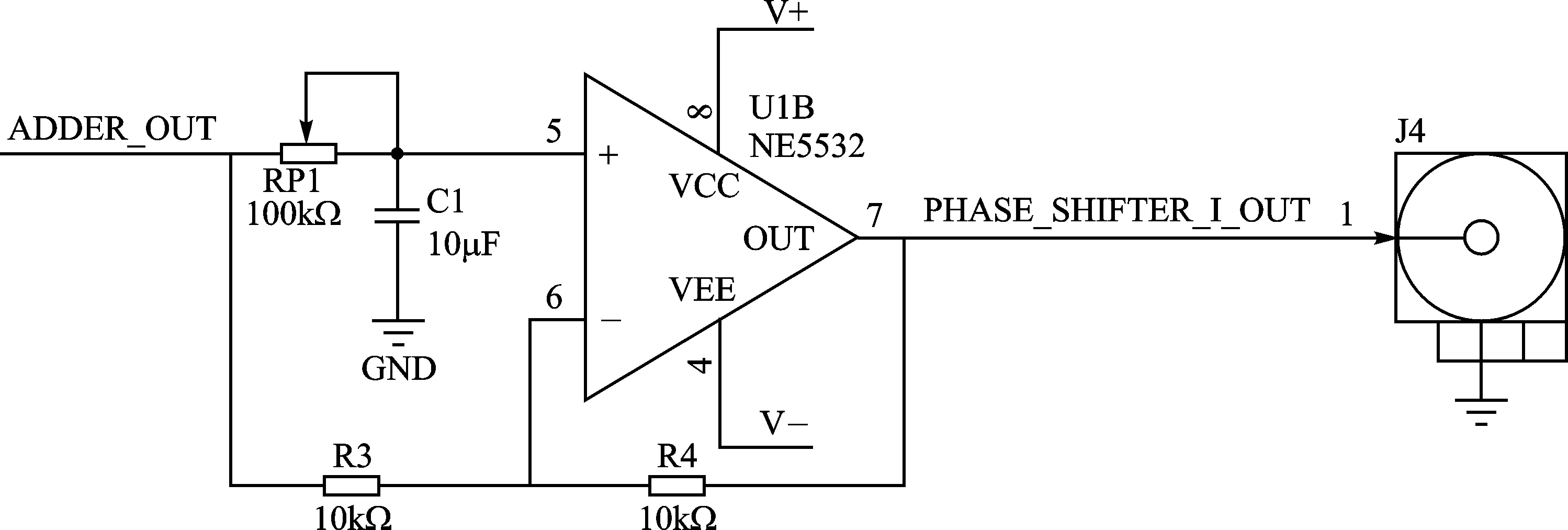

一般将RC与运放联系起来组成有源的移相电路。移相电路如图1所示。

图1 RC移相电路

图1电路调节的范围局限在90°以内,要使其调节的范围增大,可以采用多个移相电路级联的方案。理论上单个移相电路能移相的范围为0°~90°,所以为确保移相的连续性和较好的电压传输特性,采用三级RC网络级联的方法实现0°~180°移相。

3 电路与程序设计

3.1 电路的设计

系统总体框图如图2所示。

图2 系统总体框图

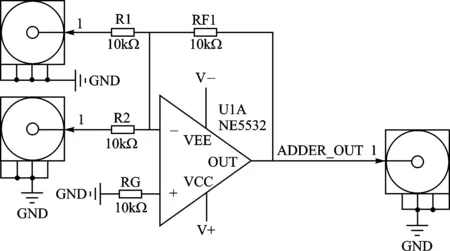

加法器电路采用运算放大器,电路结构如图3所示。

图3 加法器电路图

3.2 移相器电路

通过前面的分析,移相电路如图4所示。

3.3 电 源

电源为整个系统提供±5 V电压,确保电路的正常稳定工作。这部分电路比较简单,采用市售开关电源模块实现。

3.4 基于FPGA的LMS算法实现

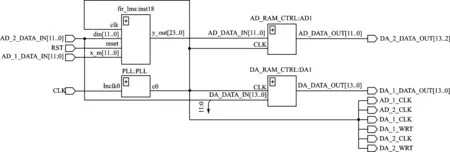

在QuartusII下设计的电路如图5所示。

(1)LMS算法模块内部信号

系统时钟:10 MHz(50 MHz FPGA系统时钟经PLL模块5分频得到)。

输入位宽:12位(适配参数为12位65 MSPS的A/D模块,芯片为AD926)。

输出位宽:14位(适配参数为14位125 MSPS的A/D模块,芯片为AD9767)。

滤波器阶数:7阶(受芯片内部集成乘法器数量的限制无法做到更多阶数,经验证,在收敛结果上4阶以上的滤波效果改进相比投入的逻辑资源收效甚微,理论上4阶就已足够)。

(2)逻辑资源消耗分析

每阶滤波器消耗的乘法器为4个,而EP4CE6芯片内部集成的乘法器只有30个,这是制约无法做出更多阶数滤波器的原因。而该芯片共有6 272个LE,此7阶滤波器只使用了337个LE。

3.5 算法仿真结果

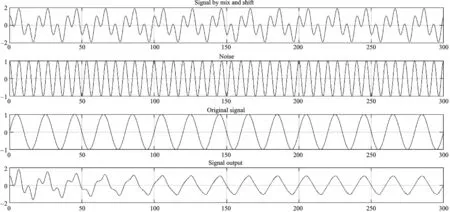

用MATLAB仿真结果如图6所示,很好地恢复出了原始信号。

图5 QuartusII下系统整体原理图

图6 MATLAB仿真结果

结 语

[1] Thomas D,Moorby P.The Verilog Hardware Description Language[M].New York:Springer Science&Business Media,2008.

[2] Meyer-Baese U,Meyer-Baese U.Digital signal processing with field programmable gate arrays[M].Berlin:springer,2007.

[3] Widrow B,McCool J M,Larimore M G,et al.Stationary and nonstationary learning characteristics of the LMS adaptive filter[J].Proceedings of the IEEE,1976,64(8):1151-1162.

[4] Haykin S S.Adaptive filter theory[M].New York:Pearson Education,2008.

[5] Kwong R H,Johnston E W.A variable step size LMS algorithm[J].IEEE Transactions on signal processing,1992,40(7):1633-1642.

[6] Chou C J,Mohanakrishnan S,Evans J B.FPGA implementation of digital filters[C]//Proc.Icspat,1993.

[7] 高鹰,谢胜利.一种变步长LMS自适应滤波算法及分析[J].电子学报,2001,29(8):1094-1097.

[8] 胡广书.数字信号处理:理论,算法与实现[M].北京:清华大学出版社,2003.

[9] 赵文兵,杨建宁.FIR 滤波器的FPGA实现及其仿真研究[J].微计算机信息,2005,21(6Z):108-109.

[10] 夏宇闻.Verilog 数字系统设计教程[J].单片机与嵌入式系统应用,2003(6):51.

汤书森(高级实验师),研究方向为嵌入式系统及其应用。