FPGA的虚拟JTAG技术对并口FLASH快速编程

2018-03-01,

,

(诺基亚上海贝尔股份有限公司,杭州 310053)

引 言

联合测试行动小组(Joint Test Action Group, JTAG) 边界扫描(Boundary Scan) 是IEEE1149.1标准,其接口在大量的数字芯片中集成,方便调试和编程。集成电路板上一般将各个芯片的JTAG接口串接起来形成菊花链,这样可以通过JTAG工具进行统一的自动化操作。FLASH存储芯片往往挂载在具有JTAG接口的芯片的总线上,这样在工厂进行大规模生产时,可以通过JTAG链对FLASH芯片进行编程。

1 JTAG接口简介

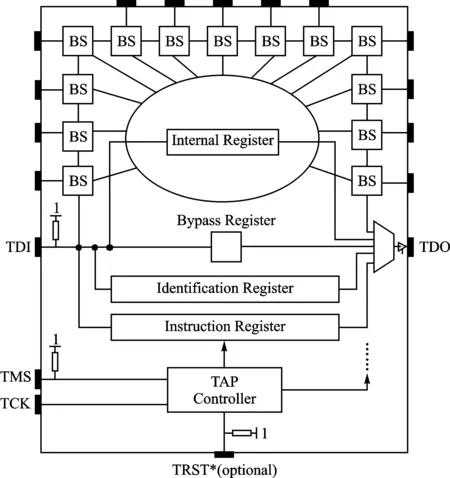

JTAG接口一般有4个信号,分别为测试数据输入(TDI)、测试数据输出(TDO)、测试时钟(TCK)、测试模式选择(TMS),测试复位信号(TRST)是可选的。TMS、TCK连入芯片内部的测试接入端口(TAP),TDI串接到芯片引脚的边界扫描单元(BS)上,这些单元串接后通过TDO连出芯片。TAP控制器在TCK触发下通过一系列的TMS信号进行状态机的改变,这些状态包括:Capture DR(得到当前数据寄存器的内容),Shift DR(对数据寄存器进行数据移位,从TDI移入,TDO移出),Update DR(更新当前数据寄存器的内容),Capture IR(得到当前数据指令寄存器的内容),Shift IR(对指令寄存器进行数据移位,从TDI移入、TDO移出),Update IR(更新当前指令寄存器的内容)。

IR和DR一起进行边界扫描单元的控制,比如当IR是全1时,一般对应的功能是测试数据直通输出(通过1比特的移位寄存器Bypass Register)。还可以控制引脚数据是从内部逻辑得到还是扫描单元得到,扫描单元的数据是从引脚输入还是输出到引脚上,从而实现特定的JTAG动作(如图1所示)。

图1 TAP控制器原理框图

2 FLASH器件的编程

集成电路板上的FLASH器件一般挂载在具有JTAG接口的芯片上,在批量生产中往往需要通过JTAG烧写一个小的引导程序或数据文件,大小从几十KB到几MB不等。

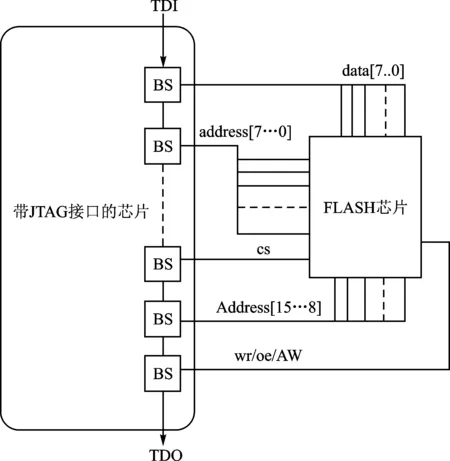

传统的边界扫描方式是依次将数据串行移位到芯片的扫描单元(BS)里,准备好各个数据线(data)、地址线(address)、片选线(cs)、读写使能线(wr)、输出使能(oe)、编程使能(AW),接线如图2所示。

图2 FLASH连接图

因为每次移位都需要遍历芯片的所有BS,一次数据的准备需要额外的开销,所以这种方式的编程十分低效,只能用来烧写小块的程序和数据。即便这样,这种方式的耗时也不可小觑,以1 MB的数据和有100个引脚的芯片以及有32字节编程块缓存的FLASH(即有N=32K字节块,一次性可以编程32字节)为例。

为方便计算,忽略FLASH的命令字,仅仅计算有效字节编程时间。一个块编程周期包含片选CS从高到低,然后写有效信号WE从高到低,数据有效(可同时),WE从低到高,WE从高到低,数据有效(可同时),WE从低到高…… 最后CS从低到高。JTAG控制器就需要至少移位K=(2N+3) cycles(对应一个TCK时钟周期),每次都需要移位Tshift=100次。假设JTAG控制器的TCK时钟为Ttck=20 MHz,那么T cycle=50 ns。总时间就是:

T=K×Tcycle×Tshift=327.695 s>5 min

实际上的引脚会更多,编程命令字的开销也不少,JTAG工具每批次移位的间隔还有时间,需要更多的编程时间。

3 虚拟JTAG简介

批量生产的自动化测试需要用到JTAG接口,而传统的JTAG编程又比较低效费时,有没有两全其美的方法呢?答案是肯定的,就是可编程器件FPGA或CPLD(Complex Programmable Logic Device)的虚拟JTAG技术。Virtual JTAG 是ALTERA(已被Intel收购)公司提出的一个概念,XILINX公司和LATTICE公司也有相对应的提法,具体实现大同小异。

在可编程器件里面,JTAG TAP控制器可以作为一个硬核对用户开放,用户可以得到TAP状态机的各种状态,当然包括TDI、TCK、TDO,从而可以接管TDI的数据,自定义返回给TDO的数据。

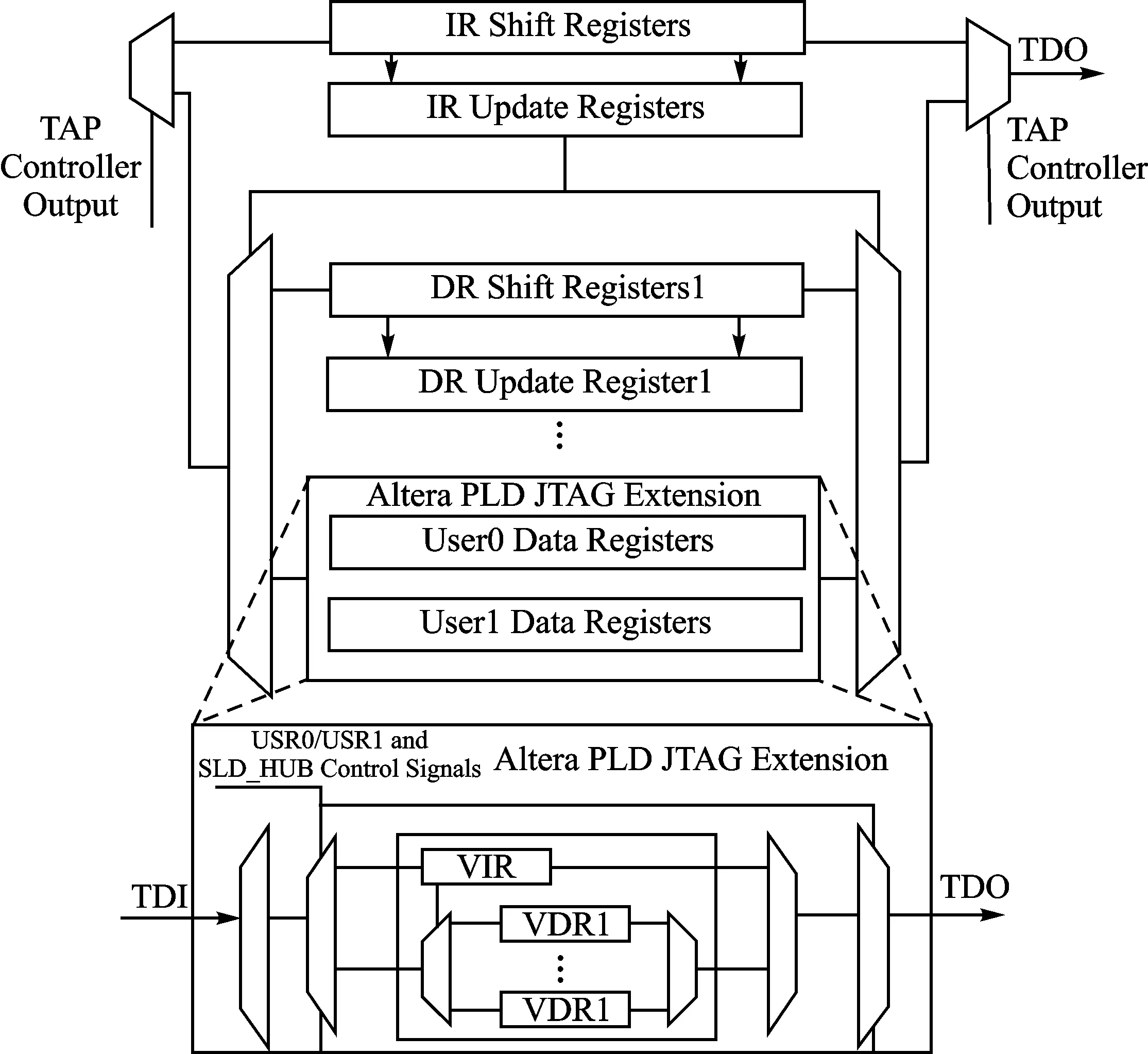

触发用户自定义的JTAG后级控制器的原理用到了指令寄存器(instruction register)里面的用户数据寄存器(user data register)。当输入特定数据给用户寄存器0和用户寄存器1后,相应的状态指示线发出高电平,JTAG后级控制器就可以知道后面的数据都是输入给它的,就可以对这些数据进行自定义的操作、自定义虚拟指令寄存器(Virtual Instruction Register,VIR)和虚拟数据寄存器(Virtual Data Register, VDR), 从而完成了虚拟JTAG的实现,如图3所示。

图3 Virtual JTAG实现原理图

4 挂载FPGA上的FLASH的快速编程

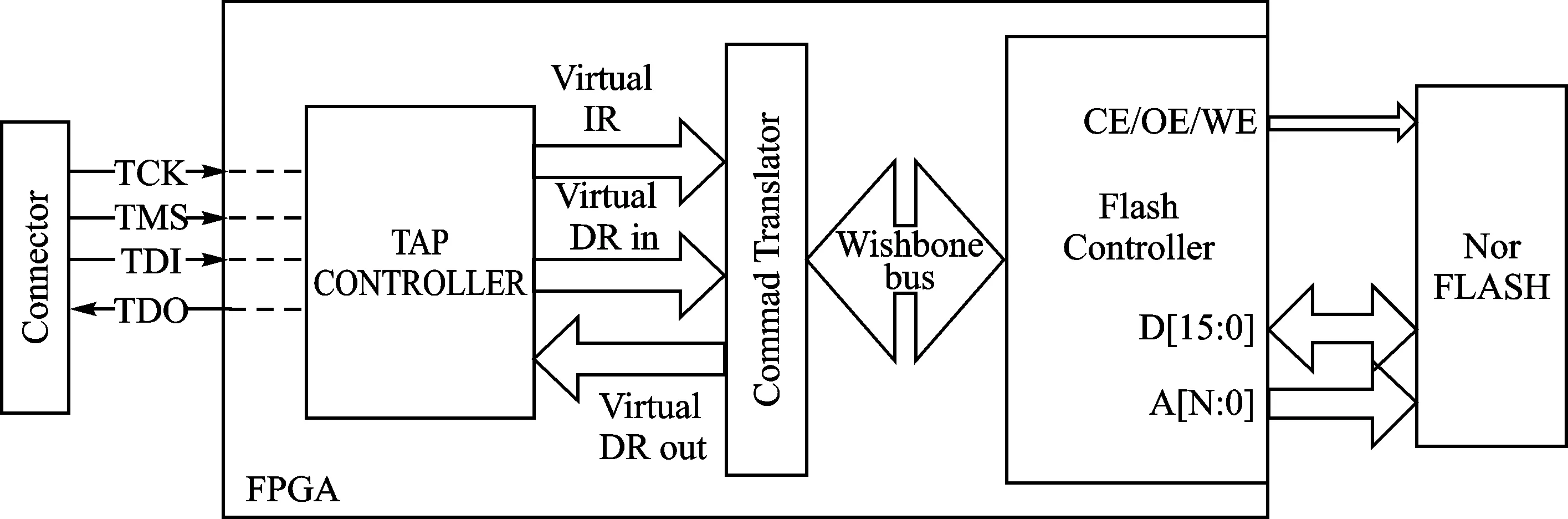

基于Virtual JTAG技术,可以自定义后级JTAG TAP控制器,定义好虚拟数据寄存器(VDR)和虚拟指令寄存器(IR)。再移植一个Flash Memory Controller,由相应的虚拟IR指令得到擦除、读取、编程等命令,相应的数据从VDR得到或保存于VDR。一般的FPGA有足够的内部存储空间RAM,所以上位机可以一次性把大容量数据通过虚拟JTAG传给VDR,后级的Flash Controller就可以启动相应的编程序列,从而节省了很多传输和边界移位的开销,极大地提高了FLASH的编程效率。图4就是一种实现的功能框图。

图4 虚拟JTAG 快速FLASH编程实现框图

TAP控制器里面对Virtual JTAG的内核进行了封装,导出了三个总线,分别是对下级模块输出的虚拟IR、虚拟DR以及从下级模块输入的虚拟DR。下级的命令转换模块从输入的VIR和VDR得到命令和数据,通过Wishbone总线转换为FLASH控制器的命令和数据,以及得到返回的数据。FLASH控制器进行对FLASH的实际读写操作。

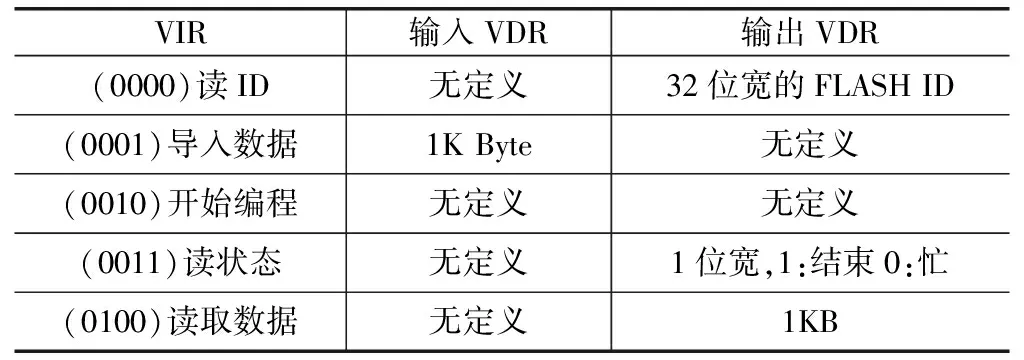

VIR定义为4比特位宽, 其定义如表1所列。

还是以1 MB的数据为例,VDR存储深度为1 KB,如果VDR的存储深度变得更大(一般FPGA里面有足够多的内存),那么时间将更少,最后的瓶颈取决于FLASH自身的编程速度。

表1 VIR VDR对应关系表

T=K×Tcycle×Tshift=52.633 6 s<1 min

结 语

[1] Dr. Ben Bennetts.IEEE 1149.1 JTAG and Boundary Scan Tutorial[EB/OL].[2017-10]. https://www.asset-intertech.com/eresources/ieee-11491-jtag-and-boundary-scan-tutorial.

[2] ALTERA. Virtual JTAG (altera_virtual_jtag) IP Core User[EB/OL].[2017-10]. https://www.altera.com/en_US/pdfs/literature/ug/ug_virtualjtag.pdf.

丁峰平(硬件工程师), 主要研究方向为电信硬件电路、FPGA设计和实现;陈莉萍(项目经理),主要研究方向为电信工程项目组织计划和实现。