基于PowerPC的嵌入式大容量高速率存储技术

2018-02-26孙德荣

孙德荣

摘要 本文分析了国内外多种嵌入式数据存储和管理的常用方案的优劣,提出了一种基于PowerPC处理器的大容量高速率数据存储及数据转发技术实现方案。该方案以高速串行Rapidl0作为信号处理机数据和控制命令输入接口,千兆以太网口为数据输出转发接口,以大容量PCI Express为NAND FLASH存储阵列的接口,以VxWorks买时操作系统为运行环境,构建了一种具有强实时性、以标准文件系统进行存储管理的大容量高速率数据存储系统。

【关键词】PowerPC Rapidlo PCI Express 数据存储

1 引言

嵌入式系统大容量高速率存储技术广泛应用于航空、航天、雷达、侦察等领域,从机载的“黑匣子”到航天测控的数据记录设备,到侦查设备的大容量存储阵列,都对大容量高速率数据存储设备有极大的需求。因此,急需构建一种运行强实时处理,高可靠性,并可按照标准文件系统进行数据存储和管理的设备。

2 国内外发展现状

2.1 基于PCIE的嵌入式设备存储方案

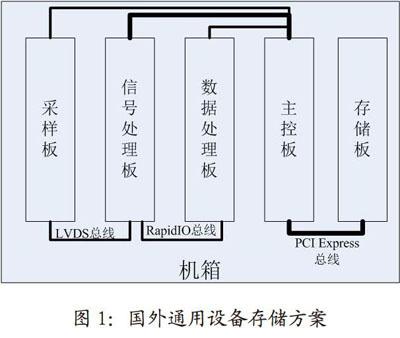

如图1所示,国外常见的嵌入式设备存储方案具有高速大容量数据存储能力,通常进行机箱内存储,机箱具有主控板,通常是单板计算机,存储阵列采用PCI Express标准电子盘存储器阵列,单板计算机与存储器阵列通过PCI Express背板总线进行互联。

这种设备的优点在于作为单机箱设备,板卡配备齐全,具有计算机主板,可运行Windows等具有良好用户界面的操作系统;具有PCI Express接口的存储板为标准电子盘结构,直接连接在主控板的北桥设备上,可直接通过主控板访问;PCI Express设备在主板程序开发过程中可完全延续过去PCI总线开发的经验,开发难度降低。缺点在于设备背板总线结构复杂,需满足多种总线拓扑结构,实现难度大。同时,在高速总线接口上不支持Rapidl0总线接口。

2.2 基于Rapidl0的嵌入式存储设备方案

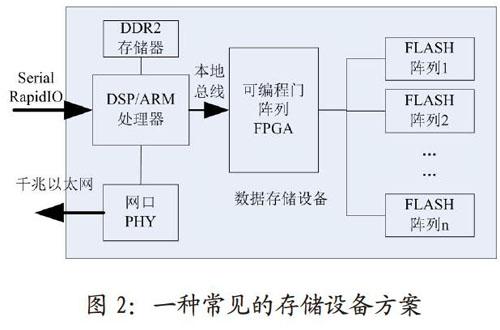

如图2所示,国内常见嵌入式存储设备方案采用DSP+FPGA架构,DSP和FPGA之间采用Local并行总线数据交互,在FPGA后扩展大规模并行NAND FLASH存储阵列。

由于NAND FLASH芯片由于工艺等问题天生就存在缺陷,在其生产和使用过程中容易产生坏块,而坏块无法正常存储数据。因此,有效的坏块管理是嵌入式数据存储无法回避的关键问题。坏块管理的实现可通过软件实现也可通过硬件实现,通常在CPU里建立坏块表,对FLASH阵列进行扫描,对坏块进行标注,数据存储时跳过坏块,并重新建立逻辑地址与物理地址的映射。同时每次上电都需要重建坏块表,并将坏块表存入非易失性存储器中。

这种通过FPGA进行阵列管理的存储方案的优缺点非常明显。优点在于:

(1)硬件架构易实现;

(2)具有高速串行数据总线接口,可实现高传输带宽;

(3)在FPGA中对数据进行分路并行存储到多个FLASH矩阵中,可实现数据横向位宽的提升和纵向数据容量的提高,从而实现高速数据记录。

然而,此种方案的缺点同样不容忽视。由于将所有FLASH阵列管理工作都交由FPGA或CPU实现,并行分配、坏块管理、数据校验等工作都由FPGA或CPU完成,同时FPGA还要兼顾高速接口、DDR2、网口MAC等若干IP核的开发。软件开发难度高,工作量极大,换句话说,此方案入门容易但做精却有很多技术门槛需要突破。因此,该方案的可靠性很大程度上受到软件开发质量的影响,难以保证。故而该方案尚未见大规模实用。

3 基于PowerPC的存储方案

3.1 存储方案硬件设计

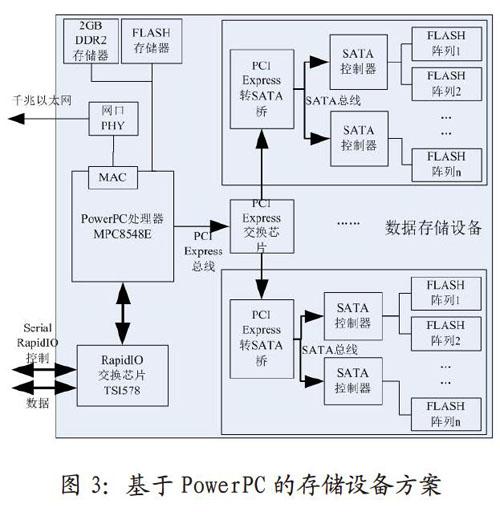

基于PowerPC的大容量高速率存储,克服了已有嵌入式存储设备方案的接口和可靠性缺陷。采用FLASH控制器芯片连接多个NAND FLASH芯片,完成坏块管理、数据校验等工作,通过横向扩展位宽、纵向扩展容量成为存储器阵列。由于FLASH控制器芯片只具备SATA接口,与大多数嵌入式处理器并不兼容。因此添加PCI Express转SATA的桥片,从而满足与高性能PowerPC嵌入式处理器接口的要求。

选用PowerPC MPC8548E处理器为存储设备的核心,它具有一个e500处理器内核,支持一个8x PCI Express接口或者一个4x PCIExpress接口加一个4x Rapidl0接口,它具有最大可支持16Gb的大容量DDR2外部存储器,具有千兆以太网MAC接口,在接口上能满足系统构建的需要。如图3所示。

存储设备具有Rapidl0接口,通过交换芯片TSI578,提供4x 2.5Gbps传输速率,与外部多个Rapidl0输入端口相连,分别接收控制命令和存储的数据。PowerPC通过PCIExpress交换芯片和转SATA桥Marvell芯片,直接控制FLASH控制器,读写FLASH阵列。每个存储阵列容量为512 GB。两个存储阵列容量可达到1TB。

3.2 FLASH阵列设计

存储设备通过NAND FLASH存储器阵列组合进行扩展,存储阵列的设计是容量和访问速率提高的关键。

FLASH控制器选用Indilinx公司的IDX110MOO芯片,它提供4个存储阵列通道,每个通道( Channel)可由8个块区(BANK)组成,每个BANK分配一个CE空间进行访问。如通道A,有8个BANK组成,分别通过CEO、CE4、CE8------CE28对该通道的每个BANK进行访问。FLASH控制器通道组成如图4所示。

FLASH控制器有32個CE空间,外接4个通道的FLASH存储阵列,每组空间具有16位数据和地址位。因此,用两片8位的NAND FLASH芯片并行连接组成16位,这两片NAND FLASH芯片共享CE空间。如FLASH1作为低位数据(DQO-DQ7),FLASH2作为高位数据(DQ8-DQ15).这两片FLASH共享CEO、CE8、CE16、CE24。如图5所示。

3.3 存储方案应用软件设计

大容量高速存储方案主要需解决两个问题,一是数据如何可靠的存储,二是数据如何方便的转发。本方案在PowerPC处理器上运行VxWorks实时操作系统,保证软件的实时性和可靠性,在VxWorks上运行文件系统,保证数据维护和转发的便捷易用。

如图6所示,数据存储实际工作流程为:PowerPC处理器从Rapidl0控制接口收到存储指令,通过文件系统建立文件列表,打开文件,从数据接口接收数据,组包并写入文件,从控制接口收到停止命令,停止接收数据。存储过程中有两點是需要注意的。

其一是文件管理。由于在VxWorks上运行文件系统,文件系统要求文件不可大于4GB,因此,大于4GB的数据需分成多个文件进行存储。在创建文件列表时,首先建立文件夹,文件夹名字即为显示在文件列表的名字,在文件夹内,创建文件名为Ol.dat、02.dat之类的文件名,若当前文件即将存满,就建立新的文件,继续存储。

其二是数据组包。数据通过Rapidl0接口输入,最大4KB为一包,考虑到FLASH读写效率,包分得太细,则写操作过于频繁并不利于写速率的提高,包分得太大,则数据存储的延时过大,不满足用户需要。综合考虑,选择32KB为一包,对数据暂存组包并存储,能达到较好的效果。

数据网络转发实际工作流程为:在停止状态PowerPC处理器从Rapidl0控制接口收到转发命令,处理器依照默认TCP或UDP的地址和端口参数配置Socket,建立链接后,从指定文件列表依次读取文件数据,并通过Socket发送到网络总线上。如图7所示。

3.4 VxWorks驱动软件移植

本文采用基于嵌入式实时操作系统VxWorks的软件运行环境,需开发PCIExpress设备的驱动程序,即PCI Express转SATA桥芯片的驱动程序。

驱动程序软件在VxWorks 6.7环境下进行设计。从VxWorks 6.5版本以上,风河公司提出了基于VxBus的设备驱动程序架构。VxBus驱动程序架构对与操作系统和硬件设备互联提供了标准定义的接口,在系统最小板级支持包(BSP)的基础上,通过匹配机制实现驱动到硬件设备的访问。在程序编写的时候通过适当的添加宏定义和修改相关配置文件,可在WorkBench开发环境上,方便的加入和去掉设备驱动程序,便于程序移植。

(1)在config.h文件中,定义设备的宏定义。

(2)注册驱动程序到VxBus。通过注册,告诉VxBus存在一个设备,VxBus根据hcfDeviceList[]表格定义的设备查询VxBus总线上挂接的设备。在sysHwlnit2函数中调用vxbXxAhciStorageRegister()函数,将设备注册到总线设备上。

(3) 设备初始化。 包括vxbXxAhcilnstlnit、vxbXxAhcilnstlnit2和vxbXxAhciInstConnect,完成后,设备被连接到VxBus总线上。

完成初始化后设备可按照标准文件系统方式对存储阵列进行正常访问。

4 存储能力测试

大容量高速率数据存储设备的关键指标在于存储容量和读写速率。存储容量由NANDFLASH存储阵列的排列和芯片数量等硬件因素决定。本方案在一个6U的板卡上实现了64片128Gb的NAND FLASH芯片,总共可达到1TB的存储容量。

存储设备的读写速率指标主要由硬件操作带宽,操作系统的效率,驱动程序的效率,读写数据包的大小,存储区域是否连续等因素影响。

由于PCI Express存储阵列可看作标准固态电子盘的形式,因此制作了存储子板,可直接在计算机测试其读写能力。通过第三方IO测试软件对存储设备的读写能力进行测试,分别设置数据包大小和访问方式,在使用一个存储阵列时,得到测试结果如图7所示。

连续读数据速率达到460MB/s,连续写数据速率达到260MB/s。可满足高速数据存储要求。

对数据网络转发进行测试,按照TCP协议进行测试,将存储设备与普通调试计算机通过直连网线进行连接,在计算机上开发socket收数程序。当打开计算机写入开关,转发速率测试为20MB/s,与通常理解的TCP在千兆以太网下的效率相当。当按照UDP协议进行测试,数据转发速率可达到45MB/s。当接收计算机使用固态硬盘或其他高速设备时,转发速率还应能进一步提高。

5 结束语

使用专用FLASH控制器芯片可极大减少软件开发工作量,避免坏块管理、数据校验等复杂运算算法,而将软件开发的重心放在高速接口,协议解析上,文件系统上,实现的难度也降低了。

嵌入式系统大容量高速率存储技术是嵌入式设备中的关键技术之一,本文分析了国内外的多种数据存储技术的实现方案,提出了一种基于PowerPC处理器的大容量高速率数据存储技术实现方案。该方案以高速串行Rapidl0作为信号处理机数据和控制命令输入接口,千兆以太网口为数据输出转发接口,以大容量PCI Express为NAND FLASH存储阵列的接口,以VxWorks实时操作系统为运行环境,构建了一种具有强实时性、以标准文件系统进行存储管理的大容量高速率数据存储系统。它的优势在于具有标准硬件架构,稳定可靠,具有标准的文件系统进行存储,数据访问、数据转发简单易行。此外,采用VxWorks嵌入式实时操作系统,软件实时性也能得到保证。本方案己成功应用于某高速数据收发设备。

参考文献

[1]张元凯,蔡惠智,刘垚,王维.基于PCIe和RAID5的高速存储系统设计[J].微计算机信息,2010(23):12-2.

[2]张萍,沈辉.基于PCI Express总线的高速数据记录卡设计[J].现代雷达,2010 (11).

[3]王立峰,胡善清,刘峰等,基于闪存的高速海量存储模块设计[J].计算机工程,2011 (04).

[4]FreescaleMPC8548E PowerQUICC rM IIIIntegrated Processor ReferenceManual,2005 (07).

[5] Wind RiverVxWorks Device DriverDeveloper' s Guide 6.7,2008 (11).