基于0.18μm CMOS工艺的锁相环频率综合器设计

2018-02-25马意彭葛飞翔

马意彭 葛飞翔

摘要 本文设计了一种基于3.3V0.18umCMOS工艺的锁相环频率综合器电路,该电路的压控振荡器部分采用LC型压控振荡器,保证了高谐振频率与低相位噪声。锁相环频率综合器输出频率在0.9GHz-9.2GHz之间,相位噪声为-95dB,锁定时间为6.1 μs,適用于时钟频率在1. 2GHz-9CHz之间的应用场合。

【关键词】锁相环频率综合器电路 LC型压控振荡器 相位噪声

在现代无线通信系统中,稳定的本地震荡源是影响通信效果的重要模块。常见的稳定震荡源是晶体震荡电路,然而晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。锁相环( Phase Locked Loop)的提出解决了上述问题,并在电子设备中得到了广泛的应用。

随着集成电路工艺的飞速发展,基于CMOS工艺的锁相环频率综合器逐渐成为研究热点。本文设计了一种基于0.18umCMOS工艺的锁相环频率综合器电路,并完成了对该电路进行了仿真分析。

1 电路设计

1.1 锁相环频率综合器的基本结构设计

锁相环电路是一个相位同步的自动控制电路,其基本组成模块包括鉴相鉴频器( PhaseFrequencyDetector,PFD)、 电荷泵(ChargePump,CP)、环路滤波器(Loop Filter,LPF)、 压控振荡器(Voltage ConrrolledOscillator,VCO) 和分频器(Divider,DIV)。其工作原理如下:首先PFD将参考信号REF与反馈信号FB的频率和相位进行比较,控制CP对LPF进行充放电;LPF可将CP的电流信号转换成电压信号,并产生一个比较稳定的直流电压VC控制VCO的输出频率Fo;Fo经过DIV后参数FB并输入PFD完成循环过程。当FB与REF的相位差不为0时,锁相环由负反馈机制自动调节,直至FB与REF的相位差为0,Ve保持恒定,vco的输出频率稳定。

1.2 PFD、CP与LPF电路设计

鉴相鉴频器通常由两个D触发器和一个与门构成。两触发器的D端接高电平,CLK端分别接参考信号REF端和反馈信号FB端;两个触发器的输出端UP与DOWN均与与门的输入端相连,与门的输出端同时接两触发器的RST端。UP端与DOWN端分别控制CP的充电开关和放电开关,两开关分别用PMOS管和NMOS管实现。充电开关和放电开关的开合可对后级电容充电和放电。LPF使用二阶低通滤波器,其作用是将电荷泵后级电容输出电压中的高频成分滤除,使得输入VCO的控制电压VC更加平稳。

1.3 VCO电路设计

VCO是整个锁相环频率综合器的核心模块,其工作频率范围直接决定了锁相环频率综合器的工作频率。常见的VCO分为环形VCO和LC型VCO两大类,其中,环形VCO多为三个以上延时单元级联而成,优点是占用面积较小、功耗较低,缺点是震荡频率较低、相位噪声较大。LC型VCO主要由高0值电感和可变电容阵列组成,并利用MOS交叉耦合负阻管提供震荡所需的能量,交叉耦合负阻管的结构包括双NMOS管、双PMOS管和NMOS/PMOS互补管三种。本文采用NMOS/PMOS交叉耦合负阻电路。

1.4 分频器电路设计

分频器根据结构类型可分为模拟分频器和数字分频器,根据分频比可分为整数分频器和小数分频器。本文使用固定分频比为20的整数分频器。该分频器由6级D触发器构成。D触发器的电路结构使用文献中的新型半静态低功耗D触发器电路,该电路具有功耗低、面积小、速度快等优点。

2 电路仿真

由Cadence Virtuoso仿真本锁相环频率综合器,仿真结果如下:

2.1 FPD与CP联合仿真

t=0时,在PFD的REF端和FB端加两个频率不同的方波激励源,在F4um时倒换两激励源,仿真结果如图1所示。由图1可以明显地看出CP的充电与放电过程。

2.2 VCO仿真

使VCO的VC端电压为0.2V,其输出波形如图2所示。由图2可以看出,在Vc=0.2V时,vco输出1GHz正弦波,且输出的波形没有明显失真。

2.3 锁相环频率综合器仿真

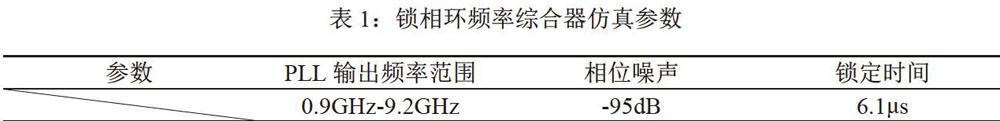

联合仿真结果见表l。

由表1可以看出,锁相环频率综合器的输出频率在0.9GHz-9.2GHz之间,带宽较宽;相位噪声为-95 dB,噪声性能较好;锁定时间为6.lμs,锁定速度快。

3 结论

本文设计了一种基于0.18umCMOS工艺的锁相环频率综合器电路,输出频率在0.9GHz-9.2GHz之间,相位噪声为-95dB,锁定时间为6.lμs,适用于时钟频率在1.2GHz-9GHz之间的应用场合。

参考文献

[1]李剑宏.13GHz VCO及锁相环设计[D].东南大学,2016.

[2]鲍进华,吕荫学,李博等.一种基于标准CMOS工艺实现的锁相环电路[J].电子设计工程,2016,24 (02): 90-92.

[3]曲明,翟越,王楠,基于射频收发应用的低噪声频率综合器设计[J].无线电通信技术,20 7,43 (03): 76-80.

[4]邓贤进,李家胤,张健,锁相频率合成器相位噪声的精确估计与仿真[J].西南科技大学学报(自然科学版),2006,21(01):128-131.

[5]张淑娥,王丹,基于LTC15 62的谐振器设计与实现[J].无线电工程,2011,41 (11):40-42.

[6]刘欣,欧阳萍.基于YIG振荡器的宽带频率综合器设计[J].无线电工程,2012,42 (02):58-61.

[7]王伦耀,吴训威,叶锡恩,新型半静态低功耗D触发器设计[J].电路与系统学报,2004,9 (06): 26-28.